6. Debugging multiple cores¶

6.1. Loading program in multiple cores¶

This section is applicable for CPU1, CPU2 and CM.

There are different ways to launch a debug session and load programs to various cores.

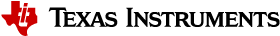

Project Debug : Once the CCS project is built, load the .out by selecting Run→Debug. CCS will identify compatible cores and prompt the user to select the required core(s). CCS will automatically connect to the selected cores and load the .out.

Project-less Debug Session : Under Target Configurations, right click on the required target configuration file and select ‘Launch selected configuration’. Connect the required targets and load the .out by selecting Run->Load.

Note

The C28x1 is the master core in this device and must be connected and loaded prior to the other cores. The clocks and other basic system initialization must be done by the CPU1 application. For example, if you want to run a CM example, CPU1 should be loaded with a basic application that does the system initialization.

For more details on Multi-Core Debug in CCS : https://processors.wiki.ti.com/index.php/Multi-Core_Debug_with_CCS

6.2. Loading program in CLA¶

The CLA program is usually embedded in the corresponding C28x program itself and is loaded as part of loading the C28x core. Once the .out is loaded to C28x core, connect to the CLA core and execute ‘Load symbols’. This option adds the symbols available in the .out for debugging purposes instead of loading the actual .out in the core.

The CLA program must be loaded in the LSxRAM. Note that the LSRAM must be configured as CLA program memory. In case of Flash configuration, the CLA program can be loaded in Flash, but must be copied to the LSxRAM. The linker command file should be updated to have this section load to Flash and run from LSxRAM. All the CLA data sections must be loaded into LSxRAM and RAM blocks must be configured as CLA Data RAM.

Please refer to the CLA example in C2000ware on memory configurations and linker command file updates needed.

6.3. Exercise 1 - Multi-core Debug Example¶

Loading program in CPU1, CPU2, CPU2.CLA using the C2000ware example. The example is available in <C2000Ware>\driverlib\f2838x\examples\c28x_dual\cla\cla_ex1_asin.

This is a dual core example in which CPU1 application initializes the system clock and the CPU2 application triggers CLA tasks and shares some data to and fro. CPU2 application includes the CLA core code as well. In this exercise, we shall load both the applications in CPU1 and CPU2 cores respectively and Load symbols of CPU2 application in CPU2’s CLA core.

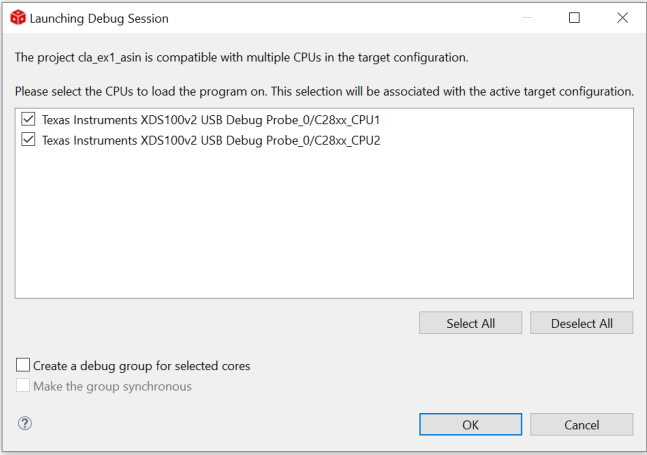

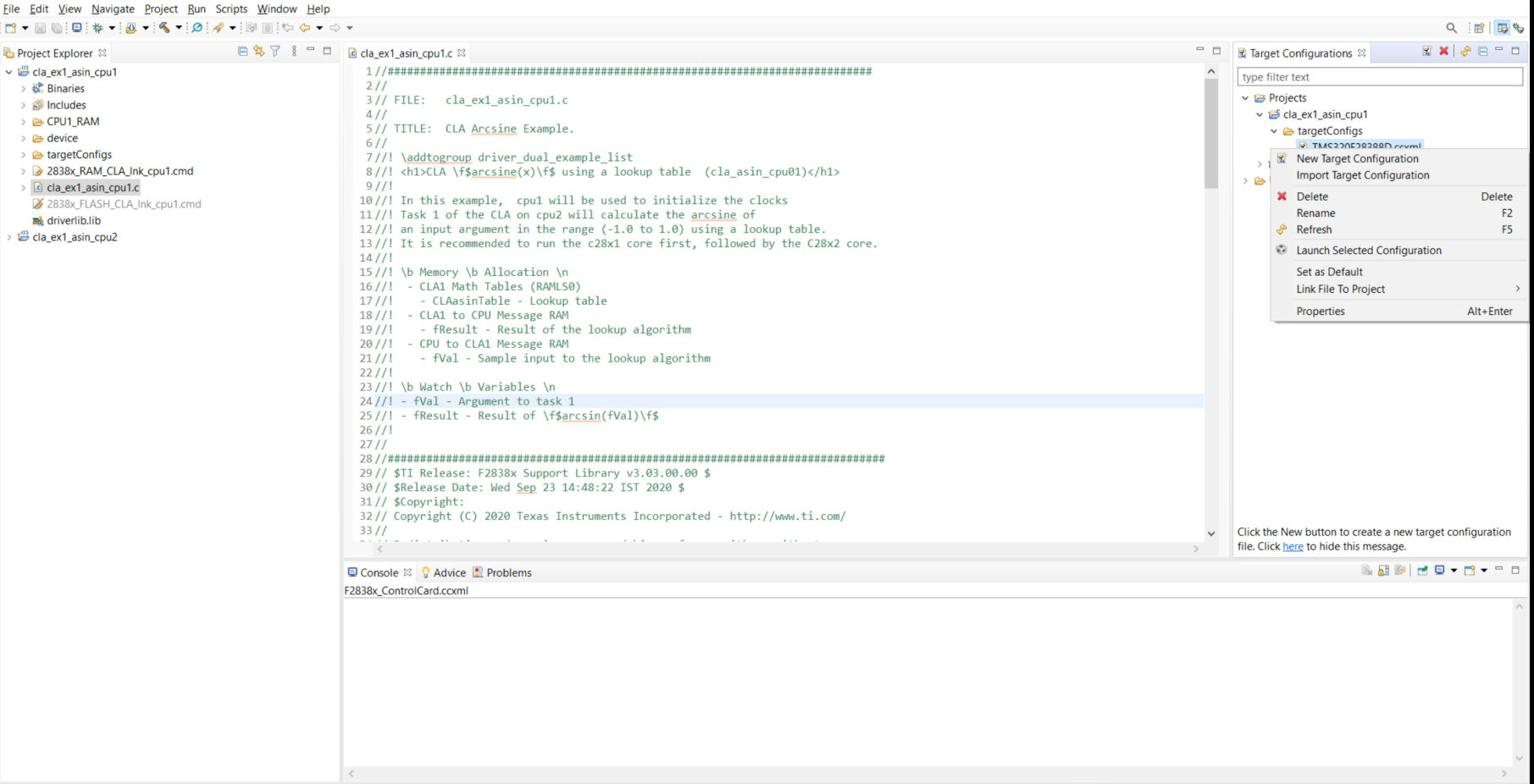

Step 1 : Launch the Target CCXML file.

Right click on the ccxml file in Target Configurations view -> Launch selected configuration.

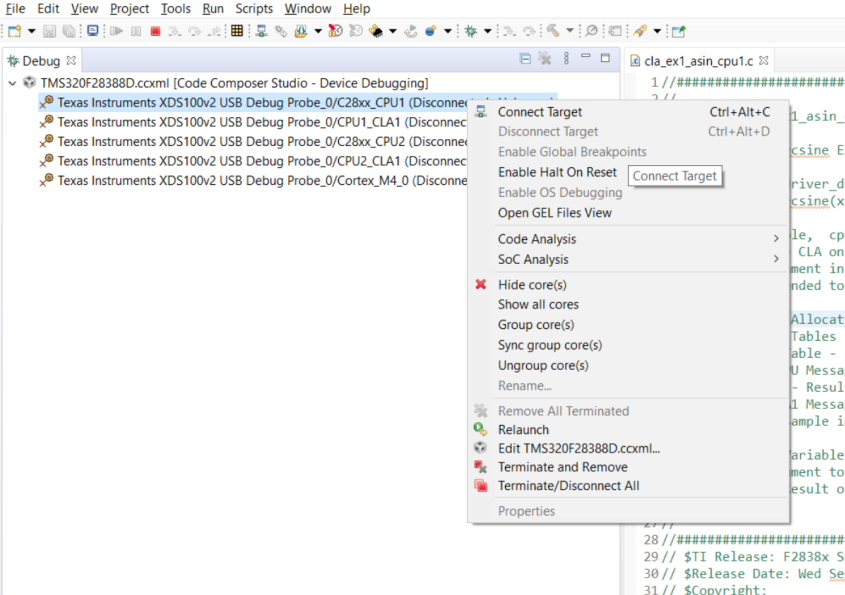

Step 2 : Connect to CPU1 and load the CPU1 application.

In the Debug view, right click on CPU1 core -> Connect Target.

Run -> Load -> Load Program and select the cla_ex1_asin_cpu1.out file.

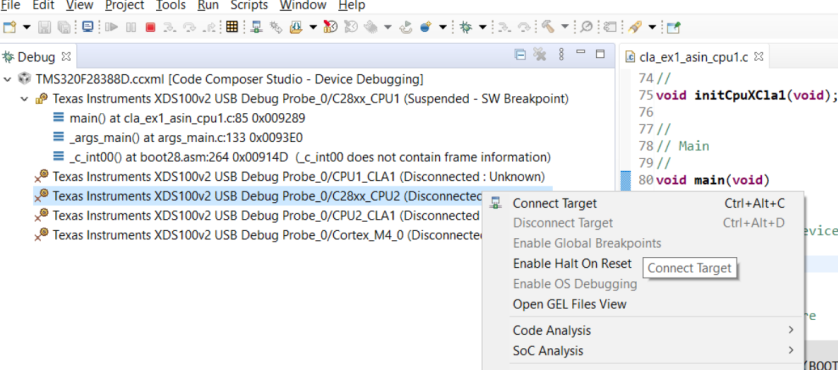

Step 3 : Connect to CPU2 and load the CPU2 application.

In the Debug view, right click on CPU2 core -> Connect Target.

Run -> Load -> Load Program and select the cla_ex1_asin_cpu2.out file.

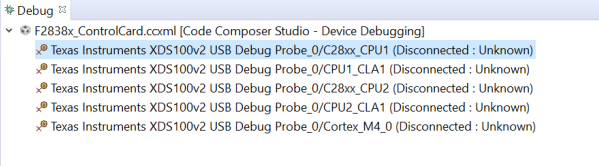

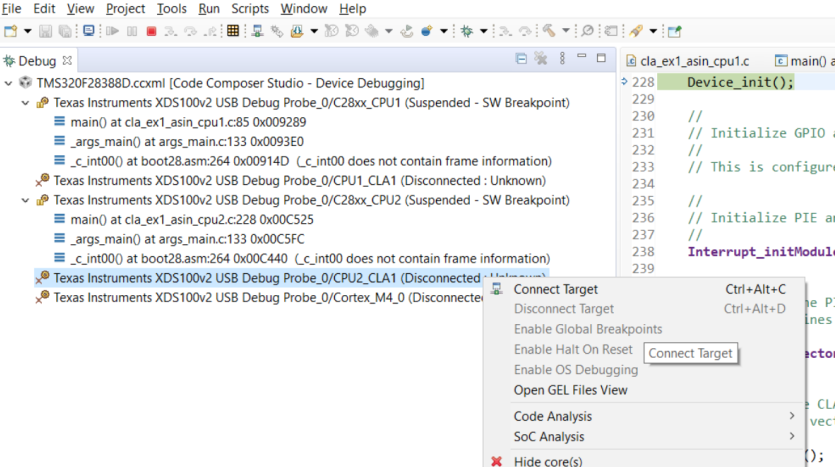

Step 4 : Connect to CLA and load the CPU2 application symbols.

Since the CPU2 application is already loaded, we just need to Load the symbols of CPU2 application on the CLA core. In the Debug view, right click on CLA core -> Connect Target.

Run -> Load -> Load Symbols and select the cla_ex1_asin_cpu2.out file.

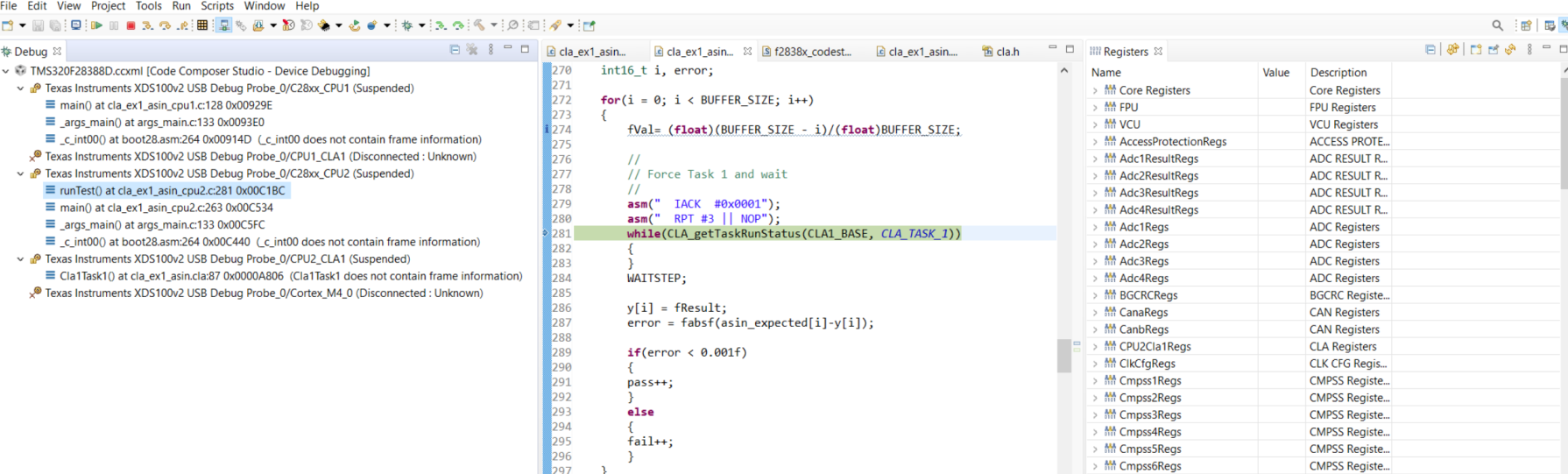

All the cores are currently in halted state. Select each core and click “Run” to execute the application. The CPU1 application should be run before running the CPU2 application. Note that this application has breakpoints inserted in the CLA code, and hence will be halted once the breakpoint is hit.

All the debugging features such as run, halt, step into, step over, breakpoints etc are available for all the cores. Make sure you select the correct core before using the controls.

6.4. Viewing Memories/Registers/Expressions¶

All the CCS views available for viewing the memory contents such as Registers, Memory Browser, Expressions, Variables, Disassembly etc are shared across cores. The contents will vary based on the active core.

6.5. Exercise 1 - Multi-core Debug Example (continued)¶

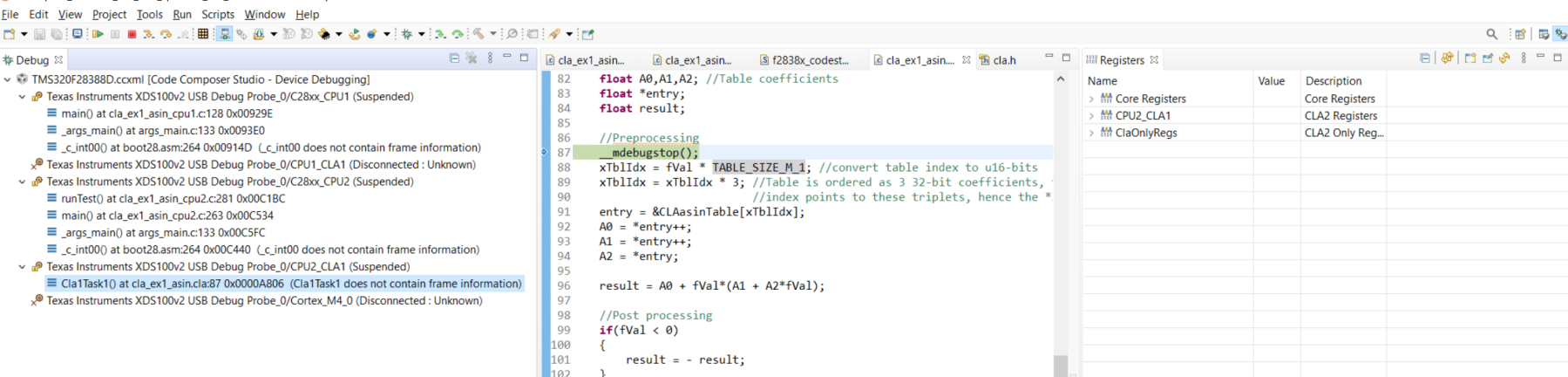

Click on the CPU2 core, the registers view displays all the registers available on the CPU2 core.

Click on the CLA core, the registers view displays all the registers available on the CLA core.

For more details on CLA debugging : https://training.ti.com/control-law-accelerator-cla-hands-workshop?context=1128629