3.3.4. Kernel Drivers¶

3.3.4.1. ADC¶

Introduction

An analog-to-digital converter (abbreviated ADC) is a device that uses sampling to convert a continuous quantity to a discrete time representation in digital form.

The TSC_ADC_SS (Touchscreen_ADC_subsystem) is an 8 channel general purpose ADC, with optional support for interleaving Touch Screen conversions. The TSC_ADC_SS can be used and configured in one of the following application options:

- 8 general purpose ADC channels

- 4 wire TS, with 4 general purpose ADC channels

- 5 wire TS, with 3 general purpose ADC channels

ADC used is 12 bit SAR ADC with a sample rate of 200 KSPS (Kilo Samples Per Second). The ADC samples the analog signal when “start of conversion” signal is high and continues sampling 1 clock cycle after the falling edge. It captures the signal at the end of sampling period and starts conversion. It uses 12 clock cycles to digitize the sampled input; then an “end of conversion” signal is enabled high indicating that the digital data ADCOUT<11:0> is ready for SW to consume. A new conversion cycle can be initiated after the previous data is read. Please note that the ADC output is positive binary weighted data.

Convert Analog voltage to Digital

To cross verify the digital values read use,

D = Vin * (2^n - 1) / Vref

Where:

D = Digital value

Vin = Input voltage

n = No of bits

Vref = reference voltage

Ex: Read value on channel AIN4 for input voltage supplied 1.01:

Formula:

D = 1.01 * (2^12 -1 )/ 1.8

D = 2297.75

Accessing ADC Pins on TI EVMs

AM335x EVM

On top of EVM, on LCD daughter board, J8 connector can be used, where ADC channel input AIN0-AN7 pins are brought out. For further information of J8 connector layout please refer to EVM schematics here

Beaglebone/Beaglebone Black

On BeagleBone platform, P9 expansion header can be used. For further information on expansion header layout please refer to the Beaglebone schematics here

Driver Configuration

You can enable ADC driver in the kernel as follows.

Device Drivers --->

[*] Industrial I/O support --->

[*] Enable buffer support within IIO

Analog to digital converters --->

<*> TI's AM335X ADC driver

Should the entry “TI’s AM335X ADC driver” be missing the MFD component —>

Device Drivers --->

Multifunction device drivers --->

<M> TI ADC / Touch Screen chip support

Building as Loadable Kernel Module

- In-case if you want to build the driver as module, use <M> instead of <*> during menuconfig while selecting the drivers (as shown below). For more information on loadable modules refer Loadable Module HOWTO

Device Drivers --->

[M] Industrial I/O support --->

[*] Enable buffer support within IIO

Analog to digital converters --->

<M> TI's AM335X ADC driver

- Use “make modules” during kernel build to build the ADC driver as

module. The module should be present in

drivers/iio/adc/ti_am335x_adc.ko. - The driver should autoload on filesystem boot. If not, load the driver using

modprobe ti_am335x_adc.ko

Device Tree

ADC device tree data is added in

file(arch/arm/boot/dts/am335x-evm.dts) as shown below.

&tscadc {

adc {

ti,adc-channels = <4 5 6 7>;

};

};

- This example is using channels AIN4, AIN5, AIN6, and AIN7 are used by ADC. The remaining channels (0 to 3) are used by TSC.

You can find the source code for ADC here

Usage

To test ADC, Connect a DC voltage supply to each of the AIN0 through AIN7 pins (based on your channel configuration), and vary voltage between 0 and 1.8v reference voltage.

CAUTION Make sure that the voltage supplied does not cross 1.8v

On loading the module you would see the IIO device created

root@arago-armv7:~# ls -al /sys/bus/iio/devices/iio\:device0/

drwxr-xr-x 5 root root 0 Nov 1 22:06 .

drwxr-xr-x 4 root root 0 Nov 1 22:06 ..

drwxr-xr-x 2 root root 0 Nov 1 22:06 buffer

-r--r--r-- 1 root root 4096 Nov 1 22:06 dev

-rw-r--r-- 1 root root 4096 Nov 1 22:06 in_voltage4_raw

-rw-r--r-- 1 root root 4096 Nov 1 22:06 in_voltage5_raw

-rw-r--r-- 1 root root 4096 Nov 1 22:06 in_voltage6_raw

-rw-r--r-- 1 root root 4096 Nov 1 22:06 in_voltage7_raw

-r--r--r-- 1 root root 4096 Nov 1 22:06 name

lrwxrwxrwx 1 root root 0 Nov 1 22:06 of_node -> ../../../../../../firmware/devicetree/base/ocp/tscadc@44e0d000/adc

drwxr-xr-x 2 root root 0 Nov 1 22:06 power

drwxr-xr-x 2 root root 0 Nov 1 22:06 scan_elements

lrwxrwxrwx 1 root root 0 Nov 1 22:06 subsystem -> ../../../../../../bus/iio

-rw-r--r-- 1 root root 4096 Nov 1 22:06 uevent

Modes of operation

When the ADC sequencer finishes cycling through all the enabled channels, the user can decide if the sequencer should stop (one-shot mode), or loop back and schedule again (continuous mode). If one-shot mode is enabled, then the sequencer will only be scheduled one time (the sequencer HW will automatically disable the StepEnable bit after it is scheduled which will guarantee only one sample is taken per channel). When the user wants to continuously take samples, continuous mode needs to be enabled. One cannot read ADC data from one channel operating in One-shot mode and and other in continuous mode at the same time.

One-shot Mode

To read a single ADC output from a particular channel this interface can be used.

root@arago-armv7:~# cat /sys/bus/iio/devices/iio\:device0/in_voltage4_raw

645

This feature is exposed by IIO through the following files:

- in_voltageX_raw: raw value of the channel X of the ADC

Continuous Mode

Overview

Important folders in the iio:deviceX directory are:

bufferenable: get and set the state of the bufferlength: get and set the length of the buffer.

root@charlie:~# ls -l /sys/bus/iio/devices/iio\:device0/buffer/

total 0

-rw-r--r-- 1 root root 4096 Nov 3 22:53 enable

-rw-r--r-- 1 root root 4096 Nov 3 22:53 length

-rw-r--r-- 1 root root 4096 Nov 3 22:53 watermark

- Scan_elements directory contains interfaces for elements that will be captured for a single sample set in the buffer.

root@arago-armv7:~# ls -al /sys/bus/iio/devices/iio\:device0/scan_elements/

drwxr-xr-x 2 root root 0 Jan 1 00:00 .

drwxr-xr-x 5 root root 0 Jan 1 00:00 ..

-rw-r--r-- 1 root root 4096 Jan 1 00:02 in_voltage0_en

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage0_index

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage0_type

-rw-r--r-- 1 root root 4096 Jan 1 00:02 in_voltage1_en

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage1_index

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage1_type

-rw-r--r-- 1 root root 4096 Jan 1 00:02 in_voltage2_en

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage2_index

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage2_type

-rw-r--r-- 1 root root 4096 Jan 1 00:02 in_voltage3_en

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage3_index

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage3_type

-rw-r--r-- 1 root root 4096 Jan 1 00:02 in_voltage4_en

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage4_index

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage4_type

-rw-r--r-- 1 root root 4096 Jan 1 00:02 in_voltage5_en

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage5_index

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage5_type

-rw-r--r-- 1 root root 4096 Jan 1 00:02 in_voltage6_en

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage6_index

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage6_type

-rw-r--r-- 1 root root 4096 Jan 1 00:02 in_voltage7_en

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage7_index

-r--r--r-- 1 root root 4096 Jan 1 00:02 in_voltage7_type

root@arago-armv7:~#

scan_elements exposes 3 files per channel:

- in_voltageX_en: is this channel enabled?

- in_voltageX_index: index of this channel in the buffer’s chunks

- in_voltageX_type : How the ADC stores its data. Reading this file should return you a string something like below:

root@arago-armv7:~# cat /sys/bus/iio/devices/iio\:device0/scan_elements/in_voltage1_type

le:u12/16>>0

Where:

- le represents the endianness, here little endian

- u is the sign of the value returned. It could be either u (for unsigned) or s (for signed)

- 12 is the number of relevant bits of information

- 16 is the actual number of bits used to store the datum

- 0 is the number of right shifts needed.

How to set it up

To read ADC data continuously we need to enable buffer and channels to be used.

Set up the channels in use (you can enable any combination of the channels you want)

root@arago-armv7:~# echo 1 > /sys/bus/iio/devices/iio\:device0/scan_elements/in_voltage0_en

root@arago-armv7:~# echo 1 > /sys/bus/iio/devices/iio\:device0/scan_elements/in_voltage5_en

root@arago-armv7:~# echo 1 > /sys/bus/iio/devices/iio\:device0/scan_elements/in_voltage7_en

Set up the buffer length

root@arago-armv7:~# echo 100 > /sys/bus/iio/devices/iio\:device0/buffer/length

Enable the capture

root@arago-armv7:~# echo 1 > /sys/bus/iio/devices/iio\:device0/buffer/enable

/dev/iio:device0To stop the capture, just disable the buffer

root@arago-armv7:~# echo 0 > /sys/bus/iio/devices/iio\:device0/buffer/enable

Userspace Sample Application

The source code is located under kernel sources at

tools/iio/iio_generic_buffer.c.

How to compile:

$ make -C <kernel-src-dir>/tools/iio ARCH=arm

The iio_generic_buffer application does all the ADC channel “enable”

and “disable” actions for you. You will only need to specify the IIO

driver. Application takes buffer length to use (256 in this example)

and the number of iterations you want to run (3 in this example). By

just enabling the buffer ADC switches to continuous mode.

root@charlie:~# ./iio_generic_buffer -?

Usage: generic_buffer [options]...

Capture, convert and output data from IIO device buffer

-a Auto-activate all available channels

-A Force-activate ALL channels

-c <n> Do n conversions

-e Disable wait for event (new data)

-g Use trigger-less mode

-l <n> Set buffer length to n samples

--device-name -n <name>

--device-num -N <num>

Set device by name or number (mandatory)

--trigger-name -t <name>

--trigger-num -T <num>

Set trigger by name or number

-w <n> Set delay between reads in us (event-less mode)

For example:-

root@charlie:~# ./iio_generic_buffer -N 0 -g -a

iio device number being used is 0

trigger-less mode selected

Enabling all channels

Enabling: in_voltage7_en

Enabling: in_voltage4_en

Enabling: in_voltage6_en

Enabling: in_voltage5_en

525.000000 924.000000 988.000000 1039.000000

754.000000 986.000000 1071.000000 1117.000000

877.000000 1067.000000 1150.000000 1169.000000

1003.000000 1143.000000 1230.000000 1226.000000

1078.000000 1222.000000 1298.000000 1286.000000

1139.000000 1286.000000 1372.000000 1343.000000

...

...

1863.000000 1954.000000 2031.000000 2074.000000

1858.000000 1959.000000 2023.000000 2083.000000

1852.000000 1958.000000 2024.000000 2076.000000

1866.000000 1964.000000 2029.000000 2083.000000

1850.000000 1952.000000 2026.000000 2074.000000

Disabling: in_voltage7_en

Disabling: in_voltage4_en

Disabling: in_voltage6_en

Disabling: in_voltage5_en

ADC Driver Limitations

This driver is based on the IIO (Industrial I/O subsystem), however this driver has limited functionality:

- “Out of Range” not supported by ADC driver.

3.3.4.2. Audio¶

Introduction

- This page gives a basic information for audio usage on supported boards

- More comprehensive information regarding to Linux audio (ALSA, ASoC) can be found:

http://processors.wiki.ti.com/index.php/AM335x_Audio_Driver%27s_Guide

http://processors.wiki.ti.com/index.php/Sitara_SDK_Linux_Audio

- For a generic linux kernel guide, try:

http://processors.wiki.ti.com/index.php/Linux_Kernel_Users_Guide

Generic commands and instructions

Most of the boards have simple audio setup which means we have one sound card with one playback and one capture PCM. To list the available sound cards and PCMs for playback:

aplay -l

To list the available sound cards and PCMs for capture:

arecord -l

In most cases -Dplughw:0,0 is the device we want to use for audio

but in case we have several audio devices (onboard + USB for example)

one need to specify which device to use for audio:

-Dplughw:omap5uevm,0 will use the onboard audio on OMAP5-uEVM

board.

To play audio on card0’s PCM0 and let ALSA to decide if resampling is needed:

aplay -Dplughw:0,0 <path to wav file>

To record audio to a file:

arecord -Dplughw:0,0 -t wav <path to wav file>

To test full duplex audio (play back the recorded audio w/o intermediate file):

arecord -Dplughw:0,0 | aplay -Dplughw:0,0

To request specific format to be used for playback/capture take a look

at the help of aplay/arecord and specify the format with -f -r -c

and open the hw device not the plughw -Dhw:0,0

For example, record 48KHz, stereo 16bit audio:

arecord -Dhw:0,0 -fdat -t wav record_48K_stereo_16bit.wav

Or to record record 96KHz, stereo 24bit audio:

arecord -Dhw:0,0 -fS24_LE -c2 -r96000 -t wav record_96K_stereo_24bit.wav

It is a good practice to save the mixer settings found to be good and reload them after every boot (if your distribution is not doing this already)

Set the mixers for the board with amixer, alsamixer

alsactl -f board.aconf store

After booting up the board it can be restored with a single command:

alsactl -f board.aconf restore

Board specific instructions

TBAL

OMAP5 uEVM

Kernel config

Device Drivers --->

Common Clock Framework --->

<*> Clock driver for TI Palmas devices

Sound card support --->

Advanced Linux Sound Architecture --->

ALSA for SoC audio support --->

<*> SoC Audio for the Texas Instruments OMAP chips

<*> SoC Audio support for OMAP boards using ABE and twl6040 codec

User space

To set up the audio routing on the board (Headset playback/capture):

amixer -c omap5uevm sset 'Headset Left Playback' 'HS DAC' # HS Left channel from DAC

amixer -c omap5uevm sset 'Headset Right Playback' 'HS DAC' # HS Right channel from DAC

amixer -c omap5uevm sset Headset 4 # HS volume to -22dB

amixer -c omap5uevm sset 'Analog Left' 'Headset Mic' # Analog Left capture source from HS mic

amixer -c omap5uevm sset 'Analog Right' 'Headset Mic' # Analog Right capture source from HS mic

amixer -c omap5uevm sset Capture 1 # Analog Capture gain to 12dB

To play audio to the HS:

aplay -Dplughw:omap5uevm,0 <path to wav file (stereo)>

On kernels where the AESS (ABE) support is not available the Line Out can be used only when playing 4 channel audio. In this case the first two channel will be routed to HS and the second two will be the Line Out.

amixer -c omap5uevm sset 'Handsfree Left Playback' 'HF DAC' # HF Left channel from DAC

amixer -c omap5uevm sset 'Handsfree Right Playback' 'HF DAC' # HF Right channel from DAC

amixer -c omap5uevm sset AUXL on # Enable route to AUXL from the HF path

amixer -c omap5uevm sset AUXR on # Enable route to AUXR from the HF path

amixer -c omap5uevm sset Handsfree 11 # HS volume to -30dB

To play audio to the Line Out one should have 4 channel sample crafted and channel 3,4 should have the audio destined to Line Out:

aplay -Dplughw:omap5uevm,0 <path to wav file (4 channel)>

DRA7 and DRA72 EVM

Kernel config

Device Drivers --->

Sound card support --->

Advanced Linux Sound Architecture --->

ALSA for SoC audio support --->

<*> SoC Audio for the Texas Instruments OMAP chips

<*> SoC Audio for Texas Instruments chips using eDMA

<*> Multichannel Audio Serial Port (McASP) support

CODEC drivers --->

<*> Texas Instruments TLV320AIC3x CODECs

<*> ASoC Simple sound card support

User space

The hardware defaults are correct for audio playback, the routing is OK and the volume is ‘adequate’ but in case the volume is not correct:

amixer -c DRA7xxEVM sset PCM 90 # Master Playback volume

Playback to Headphone only:

amixer -c DRA7xxEVM sset 'Left HP Mixer DACL1' on # HP Left route enable

amixer -c DRA7xxEVM sset 'Right HP Mixer DACR1' on # HP Right route enable

amixer -c DRA7xxEVM sset 'Left Line Mixer DACL1' off # Line out Left disable

amixer -c DRA7xxEVM sset 'Right Line Mixer DACR1' off # Line out Right disable

amixer -c DRA7xxEVM sset 'HP DAC' 90 # Adjust HP volume

Playback to Line Out only:

amixer -c DRA7xxEVM sset 'Left HP Mixer DACL1' off # HP Left route disable

amixer -c DRA7xxEVM sset 'Right HP Mixer DACR1' off # HP Right route disable

amixer -c DRA7xxEVM sset 'Left Line Mixer DACL1' on # Line out Left enable

amixer -c DRA7xxEVM sset 'Right Line Mixer DACR1' on # Line out Right enable

amixer -c DRA7xxEVM sset 'Line DAC' 90 # Adjust Line out volume

Record from Line In:

amixer -c DRA7xxEVM sset 'Left PGA Mixer Line1L' on # Line in Left enable

amixer -c DRA7xxEVM sset 'Right PGA Mixer Line1R' on # Line in Right enable

amixer -c DRA7xxEVM sset 'Left PGA Mixer Mic3L' off # Analog mic Left disable

amixer -c DRA7xxEVM sset 'Right PGA Mixer Mic3R' off # Analog mic Right disable

amixer -c DRA7xxEVM sset 'PGA' 40 # Adjust Capture volume

Record from Analog Mic IN:

amixer -c DRA7xxEVM sset 'Left PGA Mixer Line1L' off # Line in Left disable

amixer -c DRA7xxEVM sset 'Right PGA Mixer Line1R' off # Line in Right disable

amixer -c DRA7xxEVM sset 'Left PGA Mixer Mic3L' on # Analog mic Left enable

amixer -c DRA7xxEVM sset 'Right PGA Mixer Mic3R' on # Analog mic Right enable

amixer -c DRA7xxEVM sset 'PGA' 40 # Adjust Capture volume

AM335x EVM

Kernel config

Device Drivers --->

Sound card support --->

Advanced Linux Sound Architecture --->

ALSA for SoC audio support --->

<*> SoC Audio for the Texas Instruments OMAP chips

<*> SoC Audio for Texas Instruments chips using eDMA

<*> Multichannel Audio Serial Port (McASP) support

CODEC drivers --->

<*> Texas Instruments TLV320AIC3x CODECs

<*> ASoC Simple sound card support

User space

The hardware defaults are correct for audio playback, the routing is OK and the volume is ‘adequate’ but in case the volume is not correct:

amixer -c AM335xEVM sset PCM 90 # Master Playback volume

For audio capture trough stereo microphones:

amixer sset 'Right PGA Mixer Line1R' on

amixer sset 'Right PGA Mixer Line1L' on

amixer sset 'Left PGA Mixer Line1R' on

amixer sset 'Left PGA Mixer Line1L' on

In addition to previois commands for line in capture run also these:

amixer sset 'Left Line1L Mux' differential

amixer sset 'Right Line1R Mux' differential

AM335x EVM-SK

NOTE: The Headphone jack wires are swapped. This means that the channels will be swapped on the output (Left channel -> Right HP, Right channel -> Left HP)Kernel config

Device Drivers --->

Sound card support --->

Advanced Linux Sound Architecture --->

ALSA for SoC audio support --->

<*> SoC Audio for the Texas Instruments OMAP chips

<*> SoC Audio for Texas Instruments chips using eDMA

<*> Multichannel Audio Serial Port (McASP) support

CODEC drivers --->

<*> Texas Instruments TLV320AIC3x CODECs

<*> ASoC Simple sound card support

User space

The hardware defaults are correct for audio playback, the routing is OK and the volume is ‘adequate’ but in case the volume is not correct:

amixer -c AM335xEVMSK sset PCM 90 # Master Playback volume

AM43x-EPOS-EVM

Kernel config

Device Drivers --->

Sound card support --->

Advanced Linux Sound Architecture --->

ALSA for SoC audio support --->

<*> SoC Audio for Texas Instruments chips using eDMA

<*> Multichannel Audio Serial Port (McASP) support

CODEC drivers --->

<*> Texas Instruments TLV320AIC31xx CODECs

<*> ASoC Simple sound card support

User space

Note

Before audio playback ALSA mixers must be configured for either Headphone or Speaker output. The audio will not work with non correct mixer configuration!

To play audio through headphone jack run:

amixer sset 'DAC' 127

amixer sset 'HP Analog' 66

amixer sset 'HP Driver' 0 on

amixer sset 'HP Left' on

amixer sset 'HP Right' on

amixer sset 'Output Left From Left DAC' on

amixer sset 'Output Right From Right DAC' on

To play audio through internal speakers run:

amixer sset 'DAC' 127

amixer sset 'Speaker Analog' 127

amixer sset 'Speaker Driver' 0 on

amixer sset 'Speaker Left' on

amixer sset 'Speaker Right' on

amixer sset 'Output Left From Left DAC' on

amixer sset 'Output Right From Right DAC' on

To capture audio from both microphone channels run:

amixer sset 'MIC1RP P-Terminal' 'FFR 10 Ohm'

amixer sset 'MIC1LP P-Terminal' 'FFR 10 Ohm'

amixer sset 'ADC' 40

amixer cset name='ADC Capture Switch' on

If the captured audio has low volume you can try higer values for ‘Mic PGA’ mixer, for instance:

amixer sset 'Mic PGA' 50

Note: The codec on has only one channel ADC so the captured audio is dual channel mono signal.

AM437x-GP-EVM

Kernel config

Device Drivers --->

Sound card support --->

Advanced Linux Sound Architecture --->

ALSA for SoC audio support --->

<*> SoC Audio for Texas Instruments chips using eDMA

<*> Multichannel Audio Serial Port (McASP) support

CODEC drivers --->

<*> Texas Instruments TLV320AIC3x CODECs

<*> ASoC Simple sound card support

User space

The hardware defaults are correct for audio playback, the routing is OK and the volume is ‘adequate’ but in case the volume is not correct:

amixer -c AM437xGPEVM sset PCM 90 # Master Playback volume

Playback to Headphone only:

amixer -c AM437xGPEVM sset 'Left HP Mixer DACL1' on # HP Left route enable

amixer -c AM437xGPEVM sset 'Right HP Mixer DACR1' on # HP Right route enable

amixer -c AM437xGPEVM sset 'Left Line Mixer DACL1' off # Line out Left disable

amixer -c AM437xGPEVM sset 'Right Line Mixer DACR1' off # Line out Right disable

amixer -c AM437xGPEVM sset 'HP DAC' 90 # Adjust HP volume

Record from Line In:

amixer -c AM437xGPEVM sset 'Left PGA Mixer Line1L' on # Line in Left enable

amixer -c AM437xGPEVM sset 'Right PGA Mixer Line1R' on # Line in Right enable

amixer -c AM437xGPEVM sset 'Left PGA Mixer Mic3L' off # Analog mic Left disable

amixer -c AM437xGPEVM sset 'Right PGA Mixer Mic3R' off # Analog mic Right disable

amixer -c AM437xGPEVM sset 'PGA' 40 # Adjust Capture volume

BeagleBoard-X15 and AM572x-GP-EVM

Kernel config

Device Drivers --->

Sound card support --->

Advanced Linux Sound Architecture --->

ALSA for SoC audio support --->

<*> SoC Audio for the Texas Instruments OMAP chips

<*> SoC Audio for Texas Instruments chips using eDMA

<*> Multichannel Audio Serial Port (McASP) support

CODEC drivers --->

<*> Texas Instruments TLV320AIC3x CODECs

<*> ASoC Simple sound card support

User space

The hardware defaults are correct for audio playback, the routing is OK and the volume is ‘adequate’ but in case the volume is not correct:

amixer -c BeagleBoardX15 sset PCM 90 # Master Playback volume

Playback (line out):

amixer -c BeagleBoardX15 sset 'Left Line Mixer DACL1' on # Line out Left enable

amixer -c BeagleBoardX15 sset 'Right Line Mixer DACR1' on # Line out Right enable

amixer -c BeagleBoardX15 sset 'Line DAC' 90 # Adjust Line out volume

Record (line in):

amixer -c BeagleBoardX15 sset 'Left PGA Mixer Mic2L' on # Line in Left enable (MIC2/LINE2)

amixer -c BeagleBoardX15 sset 'Right PGA Mixer Mic2R' on # Line in Right enable (MIC2/LINE2)

amixer -c BeagleBoardX15 sset 'PGA' 40 # Adjust Capture volume

K2G EVM

NOTE 1: The Headphone jack is labeld as LINE OUT on the boardNOTE 2: Both analog and HDMI audio is served by McASP2, this means that they must not be used at the same time!NOTE 3: Sampling rate is restricted to 44.1KHz family due to the reference clock for McASP2 (22.5792MHz)Kernel config

Device Drivers --->

Sound card support --->

Advanced Linux Sound Architecture --->

ALSA for SoC audio support --->

<*> SoC Audio for the Texas Instruments OMAP chips

<*> SoC Audio for Texas Instruments chips using eDMA

<*> Multichannel Audio Serial Port (McASP) support

CODEC drivers --->

<*> Texas Instruments TLV320AIC3x CODECs

<*> ASoC Simple sound card support

User space

The hardware defaults are correct for audio playback, the routing is OK and the volume is ‘adequate’ but in case the volume is not correct:

amixer -c K2GEVM sset PCM 110 # Master Playback volume

For audio capture from Line-in:

amixer -c K2GEVM sset 'Right PGA Mixer Line1R' on

amixer -c K2GEVM sset 'Left PGA Mixer Line1L' on

If there’s an issue

In case of XRUN (under or overrun)

- increase the buffer size (ALSA buffer and period size)

- try to cache the file to be played in memory

- try to use application which use threads for interacting with ALSA and with the filesystem

ALSA period size must be aligned with the FIFO depth (tx/rx numevt)

Additional Information

3.3.4.3. VPFE¶

Introduction

For more general information consult the top level kernel user’s guide here.

Release Applicable

The latest release this documentation applies to is Kernel v3.12

References

- AM437x Technical Reference Manual

- Linux Media Infrastructure

API

- Documentation/media-framework.txtt

- Video for Linux Two API

Specification

- Documentation/video4linux/v4l2-framework.txt

Supported Devices

- AM437x

Driver Features

Supported Features

- Supports multiple VPFE hardware instance.

- Supports one software channel of capture and a corresponding device node (/dev/video0) is created per instance.

- Supports single I/O instance and multiple control instances.

- Supports buffer access mechanism through memory mapping and user pointers based on the videobuf2 API.

- Supports dynamic switching among input interfaces with some necessary restrictions wherever applicable.

- Supports NTSC and PAL standard on Composite and S-Video interfaces.

- Supports 8-bit BT.656 capture in UYVY and YUYV interleaved formats.

- Supports 10-bit Raw capture in Bayer formats.

- Supports V4L2 Media Controller framework.

- Supports V4L2 Sub-device framework.

- Supports V4L2 Asynchronous Sub-device registration scheme.

- Supports Device Tree infrastructure.

- Supports static and dynamic driver model (insmod and rmmod supported).

Unsupported Features/Limitations

- Internal processing block color pattern, black level compensation and culling are not supported.

- Cropping and scaling and their V4L2 IOCTLS are not supported.

- USERPTR has not been tested.

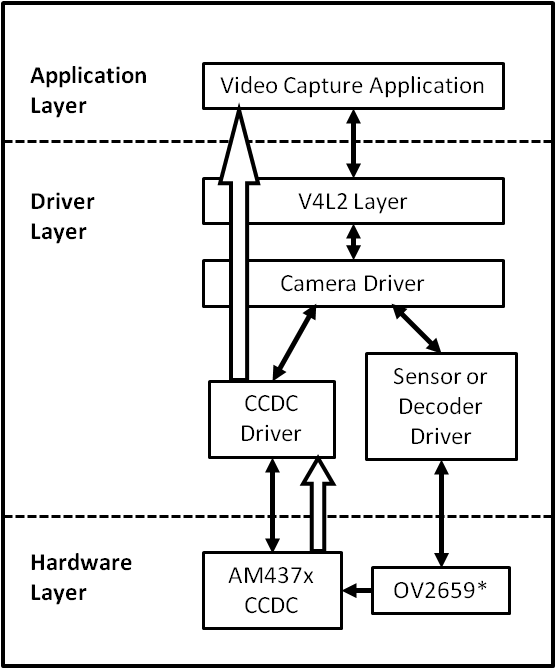

Driver Architecture

The following figure shows the basic block diagram of capture interface.

Capture Driver Component Overview

- Camera Applications

- Camera applications refer to any application that accesses the device node that is served by the Camera Driver. These applications are not in the scope of this design. They are here to present the environment in which the Camera Driver is used.

- V4L2 Subsystem

- The Linux V4L2 subsystem is used as an infrastructure to support the operation of the Camera Driver. Camera applications mainly use the V4L2 API to access the Camera Driver functionality. A Linux V4L2 implementation is used in order to support the standard features that are defined in the V4L2 specification.

- Videobuf2 Library

- This library is part of the V4L2 Layer. It provides helper functions to cleanly manage the video buffers through a video buffer queue object.

- Camera Driver

- The Camera Driver allows capturing video through an external sensor/decoder. It is a V4L2-compliant driver which provide access to the AM437x VPFE hardware feature. This driver conforms to the Linux driver model for power management. The camera driver is registered to the V4L2 layer as a master device driver. Any slave sensor/decoder driver added to the V4L2 layer will be attached to this driver through the new V4L2 sub-device interface layer. The current implementation supports only one slave device.

- Sensor/Decoder Driver

- The Camera Driver is designed to be AM437x VPFE module dependent, but platform and board independent. It is the sensor/decoder driver that manages the board connectivity. A decoder driver must implement the V4L2 sub-device interface. It should register to the V4L2 layer as a sub-device. Changing a sensor/decoder requires implementation of a new driver; it does not require changing the Camera Driver. Each sensor/decoder driver exports a set of IOCTLs to the master device through function pointers.

- CCDC library

- CCDC is a HW block, where it acts as a data input/entry port. It receives data from the sensor/decoder through parallel interface. The CCDC library exports API to configure CCDC module. It is configured by the master driver based on the sensor/decoder attached and desired output from the camera driver.

Source Location

- drivers/media/platform/ti_vpfe/

- AM437x VPFE Driver Sources

Kernel Configuration Options

The driver can be built as a static or dynamic module. When built as a dynamic module the driver is named ti_vpfe.ko.

By default VPFE support is built in to the 3.12 kernel when using omap2plus_defconfig.

$ make menuconfig ARCH=arm

- Select “Device Drivers” from the main menu.

...

...

Kernel Features --->

Boot options --->

CPU Power Management --->

Floating point emulation --->

Userspace binary formats --->

Power management options --->

[*] Networking support --->

Device Drivers --->

...

...

- Select “Multimedia support” from the menu and enter it.

...

...

[ ] ARM Versatile Express platform infrastructure

-*- Voltage and Current Regulator Support --->

<*> Multimedia support --->

Graphics support --->

<*> Sound card support --->

HID Devices --->

[*] USB support --->

...

...

- Select “V4L platform devices” from the menu.

--- Multimedia support

...

...

[ ] Media PCI Adapters ----

[*] V4L platform devices -->

[ ] Memory-memory multimedia devices ...

[ ] Media test drivers ----

*** Supported MMC/SDIO adapters ***

< > Cypress firmware helper routines

*** Media ancillary drivers (tuners, sensors, i2c, frontends) ***

[ ] Autoselect ancillary drivers (tuners, sensors, i2c, frontends)

Encoders, decoders, sensors and other helper chips --->

Sensors used on soc_camera driver ----

...

...

- Select “TI AM437x VPFE video capture driver” from the menu.

--- V4L platform devices

...

...

< > SoC camera support

<*> TI AM437x VPFE video capture driver

...

...

- Selection of OV2659 Camera Sensor driver -

- Now go back to the Multimedia support level

De-select option Autoselect pertinent encoders/decoders and other helper chips and go inside Encoders/decoders and other helper chips

--- Multimedia support

...

...

[ ] Autoselect ancillary drivers (tuners, sensors, i2c, frontends)

Encoders, decoders, sensors and other helper chips --->

Sensors used on soc_camera driver ----

...

...

- Select “OmniVision OV2659 sensor support” from the menu.

*** Audio decoders, processors and mixers ***

...

...

< > Texas Instruments THS8200 video encoder

*** Camera sensor devices ***

<*> OmniVision OV2659 sensor support

< > OmniVision OV7640 sensor support

...

...

Building as Loadable Kernel Module

- If you want to build the driver as a module, use <M> instead of <*> during menuconfig while selecting the drivers (as shown above). For more information on loadable modules refer Loadable Module HOWTO

DT Configuration

Example configuration in your board DTS file to enable VPFE instance 0. This an excerpt from the arch/arm/boot/dts/am437x-gp-evm.dts

&am43xx_pinmux {

pinctrl-names = "default";

pinctrl-0 = <&clkout2_pin &ddr3_vtt_toggle_default>;

...

...

vpfe0_pins_default: vpfe0_pins_default {

pinctrl-single,pins = <

0x1B0 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_hd mode 0*/

0x1B4 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_vd mode 0*/

0x1B8 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_field mode 0*/

0x1BC (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_wen mode 0*/

0x1C0 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_pclk mode 0*/

0x1C4 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_data8 mode 0*/

0x1C8 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_data9 mode 0*/

0x208 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_data0 mode 0*/

0x20C (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_data1 mode 0*/

0x210 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_data2 mode 0*/

0x214 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_data3 mode 0*/

0x218 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_data4 mode 0*/

0x21C (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_data5 mode 0*/

0x220 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_data6 mode 0*/

0x224 (PIN_INPUT_PULLUP | MUX_MODE0) /* cam0_data7 mode 0*/

>;

};

vpfe0_pins_sleep: vpfe0_pins_sleep {

pinctrl-single,pins = <

0x1B0 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_hd mode 0*/

0x1B4 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_vd mode 0*/

0x1B8 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_field mode 0*/

0x1BC (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_wen mode 0*/

0x1C0 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_pclk mode 0*/

0x1C4 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_data8 mode 0*/

0x1C8 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_data9 mode 0*/

0x208 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_data0 mode 0*/

0x20C (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_data1 mode 0*/

0x210 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_data2 mode 0*/

0x214 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_data3 mode 0*/

0x218 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_data4 mode 0*/

0x21C (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_data5 mode 0*/

0x220 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_data6 mode 0*/

0x224 (DS0_PULL_UP_DOWN_EN | INPUT_EN | MUX_MODE7) /* cam0_data7 mode 0*/

>;

};

...

...

};

...

...

&i2c1 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&i2c1_pins>;

...

...

ov2659@30 {

compatible = "ti,ov2659";

reg = <0x30>;

port {

ov2659_0: endpoint {

remote-endpoint = <&vpfe0_ep>;

mclk-frequency = <12000000>;

};

};

};

};

...

...

&vpfe0 {

status = "okay";

pinctrl-names = "default", "sleep";

pinctrl-0 = <&vpfe0_pins_default>;

pinctrl-1 = <&vpfe0_pins_sleep>;

/* Camera port \*/

port {

vpfe0_ep: endpoint {

remote-endpoint = <&ov2659_0>;

if_type = <2>;

bus_width = <8>;

hdpol = <0>;

vdpol = <0>;

};

};

};

- remote-endpoint is a reference to the i2c sensor node. This is used during sub-device registration.

- if-type defines the interface type used <0> BT656, <2> RAW.

- bus_width defines the number of data pins actually connected between the camera and the vpfe module. Only 2 values are supported 8 and 10. Pre-Beta boards had 10 data pins connected, Beta (and later) have 8 data pins connected which is a hardware level optimization reducing memory bus bandwidth and eliminating post-processing to compact the captured data.

- hdpol when set to 1 is used to invert the Hsync polarity

- vdpol when set to 1 is used to invert the Vsync polarity

Driver Usage

As seen previously the driver create a /dev/videoX device node when a sub-device is successfully registered. The device node provide access to the driver following a standard V4L2 API.

The driver support the following system calls and V4L2 ioctls:

open(), close(), mmap(), munmap() and ioctl()

| V4L2 ioctls | Definition |

|---|---|

| VIDIOC_REQBUFS | Allocating Memory Buffers |

| VIDIOC_QUERYBUF | Getting Buffer’s Physical Address |

| VIDIOC_QUERYCAP | Query Capabilities |

| VIDIOC_ENUMINPUT | Input Enumeration |

| VIDIOC_S_INPUT | Set Input |

| VIDIOC_G_INPUT | Get Input |

| VIDIOC_ENUMSTD | Standard Enumeration |

| VIDIOC_QUERYSTD | Query Standard |

| VIDIOC_S_STD | Set Standard |

| VIDIOC_G_STD | Get Standard |

| VIDIOC_ENUM_FMT | Format Enumeration |

| VIDIOC_ENUM_FRAMESIZES | Frame Size Enumeration |

| VIDIOC_S_FMT | Set Format |

| VIDIOC_G_FMT | Get Format |

| VIDIOC_TRY_FMT | Try Format |

| VIDIOC_QUERYCTRL | Query Control* |

| VIDIOC_S_CTRL | Set Control* |

| VIDIOC_G_CTRL | Get Control* |

| VIDIOC_QBUF | Queue Buffer |

| VIDIOC_DQBUF | Dequeue Buffer |

| VIDIOC_STREAMON | Stream On |

| VIDIOC_STREAMOFF | Stream Off |

| VIDIOC_CROPCAP | Query Cropping Capabilities+ |

| VIDIOC_S_CROP | Set Crop Parameters+ |

| VIDIOC_G_CROP | Get Current Cropping Parameters+ |

Table: Supported ioctls

There are plenty of generic V4L2 capture applications available:

There is also a media controller sample application which can be used as an example to configured sensor/decoder sub-device:

Debugging

As vpfe driver is based on the V4L2 framework, framework level tracing can be enable as follows:

- echo 3 >/sys/class/video4linux/video1/dev_debug This allows V4L2 ioctl calls to be logged.

- echo 3 > /sys/module/videobuf2_core/parameters/debug This allows VB2 buffers operation to be logged.

In addition vpfe also has specific debug log which can be enabled as follows:

- echo 3 > /sys/module/am437x_vpfe/parameters/debug

3.3.4.4. VIP¶

Introduction

This page gives a basic description of Video Input Port (VIP) hardware, the Linux kernel driver (ti-vip) and various TI boards which uses VIP. The technical reference manual (TRM) for the SoC in question, and the board documentation give more detailed descriptions.

Release Applicable

This page applies to TI’s v4.4 kernel. Although most of it is also applicable to TI’s v4.1 and v3.14 kernel.

Supported Devices

The VIP IP is only available on the following TI SoCs or SoC families:

- AM5x

- DRA7x

Hardware Architecture

On supported SoCs the Video Input Port (VIP) module is used for video capture from video encoder/decoder and camera sensor.

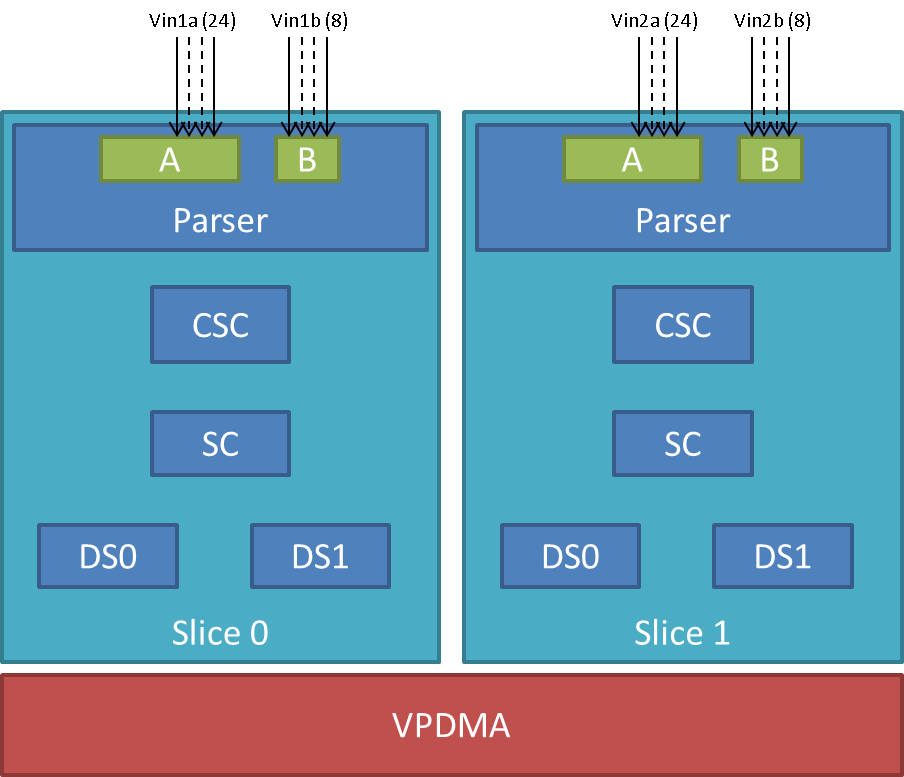

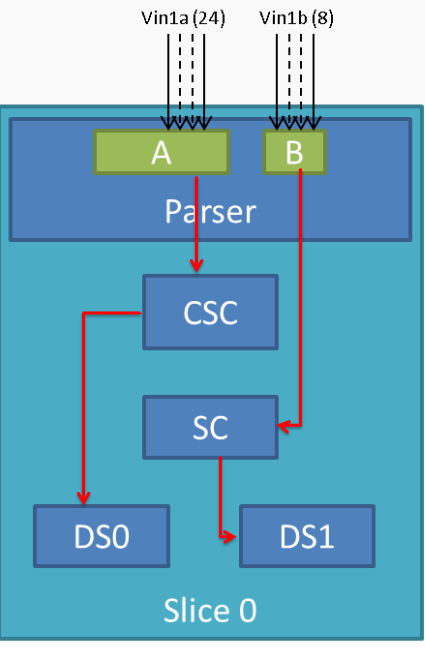

VIP Instance block diagram

VIP instance has two slices each having one 24/16/8 bit port and one 8 bit video port. Each slice has a color space converter block, a scaler block and a pair of down-sampler block. A common VPDMA block is used for writing frames to memory. VIP Parser supports video capture from discrete sync / embedded sync, YUV / RGB format video sources. It calculates the frame size based on the count of clocks in hsyncs(width) and count of hsyncs in vsyncs(height). The complex data path configurability allows to have up to four parallel ports captures from one instance. One port per slice can utilize the inline CSC and/or SC block at a time. VPDMA block has a TI proprietary custom programmable processor. A custom firmware is needed for this custom processor. VPDMA programming is descriptor based. It allows to setup, configure, control, abort DMA transactions from different channels to and from memory. VPDMA needs physically contiguous buffers for capture. It also supports addressing in the TILER space.

SoC Hardware Feature

- AM572x/DRA74x/DRA75x

- VIP1 and VIP2 instance each supporting up to

- Two separate 24-bit video ports for parallel RGB/YUV/RAW (or BT656/1120) data, up to 165 MHz

- Two separate 8-bit video ports for YUV/RAW (or BT656) data, up to 165 MHz

- VIP3 instance supporting up to

- Two separate 16-bit video ports for parallel RGB/YUV/RAW (or BT656/1120) data, up to 165 MHz

- VIP1 and VIP2 instance each supporting up to

- AM571x/DRA72x

- VIP1 instance supporting up to

- Two separate 24-bit video ports for parallel RGB/YUV/RAW (or BT656/1120) data, up to 165 MHz

- Two separate 8-bit video ports for YUV/RAW (or BT656) data, up to 165 MHz

- VIP1 instance supporting up to

Driver Architecture

Linux kernel driver for the VIP is implemented as per the V4L2 standard for capture devices. VIP driver is responsible only for the programming of the VIP device. For programming external video devices, we need a V4L2 subdevice driver which is used in conjunction with the V4L2 driver. It also uses some of the helper kernel libraries videobuf2 (VB2) for common buffer operations, queue management and memory management.

- Linux Media Subsystem Documentation

- Video for Linux API

- V4L2 videobuf2 functions and data structures

- V4L2 sub-devices

V4L2 endpoint device tree bindings

Different camera / video sources have different configuration parameters when interfacing with the VIP video ports. Common interfacing properties like Hsync, Vsync, Pclk polarities can be different across different devices. V4L2 endpoint allows to describe these as part of device tree definition. This makes the VIP driver generic enough to have no dependency on the camera device. It also provides the flexibility to work with new cameras by doing simple device tree modifications.

Following is an example showcasing the DT entries of VIP device node and its usage when interfacing different video sources.

| VIP device definition | Camera device definition |

|---|---|

vip1 {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

ports {

vin1a: port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

endpoint@0 {

remote-endpoint = <&cam1>;

};

};

...

vin2a: port@2 {

...

reg = <2>;

};

...

};

};

|

ov10633@37 {

compatible = "ovti,ov10633";

reg = <0x37>

...

port {

cam1: endpoint {

remote-endpoint = <&vin1a>;

hsync-active = <1>;

vsync-active = <1>;

pclk-sample = <0>;

};

};

};

|

V4L2 asynchronous subdevice registration

Each camera device that VIP driver communicates to is modelled as a V4L2 subdevice. In the probe sequence, VIP and camera drivers are probed at different time. V4L2 async subdevice binding helps to bind the VIP device and the camera device together. VIP driver looks for the camera entries in the endpoints and registers (v4l2_async_notifier_register) a callback if any of the requested devices become available. vip_async_bound implements the priority based binding which allows to have multiple cameras muxed against same video port. The device tree order determines which of these gets picked up by the driver. Note that the V4L2 g/s_input ioctls are not supported, userspace won’t be able to select specific camera with these ioctls.

Of course the target subdevice driver also needs to support the asynchronous registration framework. On top of this the subdevice driver must implements the following ioctls for the handshake with the VIP driver to work properly:

- get_fmt()

- set_fmt()

- enum_mbus_code()

- enum_frame_sizes()

- s_stream()

Driver Features

Note: this is not a comprehensive list of features supported/not supported.

Supported Features

- VIP input Pixel formats

- Sub device is expected to support one of the below format. Only YUV422 interleaved format arranged as UYVY is supported in YUV mode. This restrictions in pixel arrangements is to take care of silicon errata i839 guidelines.

- The data formats mentioned in parenthesis in below table is in

V4L2 Media Bus Format.

- For instance, a format where pixels are encoded as 8-bit YUV values downsampled to 4:2:2 and transferred as 2 8-bit bus samples per pixel in the U, Y, V, Y order is named as MEDIA_BUS_FMT_UYVY8_2X8.

- The data bus width can be 8 bit or 16 bit wide when capturing in

UYVY mode.

- Default bus width configuration is 8 bit. When using 16 bit wide bus, specify the bus width in dts file as bus-width = <16>;

| YUV | RGB | RAW Bayer 8-bit |

|---|---|---|

| UYVY (UVYV8_2x8) | RGB24 (RGB888_1X24) | BGGR8 (SBGGR8_1X8) |

| RGB32 (ARGB8888_1X32) | GBRG8 (SGBRG8_1X8) | |

| GRBG8 (SGRBG8_1X8) | ||

| RGGB8 (SRGGB8_1X8) |

Table: Supported Input Pixel Format in FOURCC and V4L2 MEDIA_BUS_FMT

- Supported VIP output pixel formats

- Runtime pixel format availability is based on the sub-device capability. Use yavta –enum-formats /dev/video1 to get an accurate list.

| YUV | RGB | RAW Bayer 8-bit |

|---|---|---|

| NV12 | RGB3 | BA81 |

| YUYV | BGR3 | GBRG |

| UYVY | RGB4 | GRBG |

| VYUY | BGR4 | RGGB |

| YVYU |

Table: Supported Output Pixel Format

- Scaling (only available with YUV format)

- Down-scaling only (will use the closest native resolution larger than the desired frame size)

- Down-scaling ratio limitations -

- Horizontal - up to 1/8th

- Vertical - up to 3/16

- Color Space Conversion

- YUV to RGB (tested)

- RGB to YUV (untested)

- V4L2 single-planar buffers and interface

- Supports MMAP buffers (allocated by kernel from global CMA pool) and also allows to export them as DMABUF

- Supports DMABUF import (Reusing buffers from other drivers)

- Discrete Sync capture

- Embedded Sync capture in 8-bit mode

- Multi-channel capture when using embedded sync

Unsupported Features/Limitations By VIP Driver

- Media Controller Framework

- Cropping/Selection ioctls

- TILER memory space

- 16 bit embedded capture

- 16 bit RAW capture

- YUV444 Input format

- YUV444 mode is similar to RGB24 mode. Driver can be modified to enable YUV44 mode by referring to the RGB24 settings in vip.c file

- Input format capture for YUV422 mode in arrangements other than UYVY

- Refer to the settings of Raw Bayer input format in vip.c file to enable other YUV input mode capture

- Maximum capture resolution restricted to 2048x1536

- HSYNC and Discrete Basic Mode set as 1 are hard coded in the driver and not controlled through dts entries. VIP driver register settings will need changes if the signals used for capture are DE (ACTVID) and/or Discrete Basic Mode set as 0.

Hardware Limitations

VIP Slice

- CSC, SC and/or DS processing in discrete sync mode is supported only

for following combination -

- Input as RGB or UYVY format and output in supported YUV format

- CSC, SC and/or DS processing is not supported for embedded sync input in multiplexed source mode

- CSC and SC can not be used simultaneously by port A and port B of a Slice. For example, if port A is using CSC, then port B can only use SC but not CSC

- Maximum input resolution when using SC is 2047x2047 pixels (irrespective of pixel size).

- Maximum capture width when not using scaling is 8K bytes. This

translates to maximum frame width of -

- 4K when capturing in YUV422 mode (2 bytes/pixel)

- 2.2K when capturing in RGB24 mode (3 bytes/pixel)

- 8K when capturing as Raw Bayer 8-bit or other format treated as 1 bytes/pixel

- No restrictions on height of capture video

Driver Configuration

Kernel Configuration Options

ti-vip supports building both as built-in or as a module.

ti-vip can be found under “Device Drivers/Multimedia support/V4L platform devices” in the kernel menuconfig. You need to enable V4L2 (CONFIG_MEDIA_SUPPORT, CONFIG_MEDIA_CAMERA_SUPPORT) and then enable V4L platform driver (CONFIG_V4L_PLATFORM_DRIVERS) before you can enable ti-vip (CONFIG_VIDEO_TI_VIP).

Driver Usage

Loading ti-vip

If built as a module, you need to load all the v4l2-common, videobuf2-core and videobuf2-dma-contig modules before ti-vip will start.

Using ti-vip

When ti-vip is enabled, the capture device will appear as /dev/videoX. Standard V4L2 user space applications can be used as long as the capability of the application matches.

- dmabuftest example Use VIP to capture a 1280x800 YUYV video stream and display it on an HDMI display using DMABUF buffers.

dmabuftest -s 36:1920x1080 -c 1280x800@YUYV -d /dev/video1

- yavta example Capture 800x600 YUYV video stream to file.

yavta -c60 -fYUYV -Fvout_800x600_yuyv.yuv -s800x600 /dev/video1

dmabuftest can be found from:

https://git.ti.com/glsdk/omapdrmtest

yavta can be found from:

http://git.ideasonboard.org/yavta.git

Debugging

As ti-vip driver is based on the V4L2 framework, framework level tracing can be enable as follows:

- echo 3 >/sys/class/video4linux/video1/dev_debug This allows V4L2 ioctl calls to be logged.

- echo 3 > /sys/module/videobuf2_core/parameters/debug This allows VB2 buffers operation to be logged.

In addition ti-vip also has specific debug log which can be enabled as follows:

- echo 3 > /sys/module/ti_vip/parameters/debug

Troubleshooting common capture problem

Bootup/Probe checks

First thing to look for is if the video devices are created or not; Check the bootlog for prints in the kernel bootlog.

Check device probe status

dmesg | grep ov1063x

dmesg | grep video

Depending on the camera connected, the following prints can confirm the probe being successful.

| Bootlog print | Result |

|---|---|

| ov1063x 1-0037: ov1063x Product ID a6 Manufacturer ID 33 | Onboard camera probe success |

| ov1063x X-00XX: Failed writing register 0x0103! | Camera not connected |

No video captured

When the capture application is launched, it is expected to start video capture and display frames on to display. Sometimes, no video is not displayed on the screen. To identify this being an issue with capture, simple test can be done. Each VIP slice has a dedicated interrupt line. If the capture is successful, the interrupt count should increase periodically.

Check interrupts to confirm capture failure

cat /proc/interrupts | grep vip

362: 941 0 GIC 102 vip1-s0

363: 183 0 GIC 101 vip1-s1

364: 241 0 GIC 100 vip2-s0

365: 0 0 GIC 99 vip2-s1

366: 46 0 GIC 98 vip3-s0

367: 2 0 GIC 97 vip3-s1

In the above example, one can conclude that

- Capture from Vin1, Vin2, Vin3, Vin5 is working fine.

- Vin4(vip2-s1) capture was never attempted.

- Vin6(vip3-s1) capture is failing (Note that first two interrupts occur even if the camera isn’t connected. Refer VPDMA fifo)

Note that the IRQs are shared for different ports of same slice. This means, vip1-s0 line will carry interrupts from both vin1a and vin1b. This test can be used when only one of the port is in use.

VIP Parser is not able to detect the video

| Video Port | Parser size register | Parser config register |

|---|---|---|

| vin1a | 0x48975530 | 0x48975504 |

| vin1b | 0x48975570 | 0x4897550C |

| vin2a | 0x48975A30 | 0x48975A04 |

| vin2b | 0x48975A70 | 0x48975A0C |

| vin3a | 0x48995530 | 0x48995504 |

| vin3b | 0x48995570 | 0x4899550C |

| vin4a | 0x48995A30 | 0x48995A04 |

| vin4b | 0x48995A70 | 0x48995A0C |

| vin5a | 0x489B5530 | 0x489B5504 |

| vin6a | 0x489B5A30 | 0x489B5A0C |

Invalid parser configuration

Depending on the camera used, certain parameters of the video port needs to be configured correctly. Device tree definition (endpoint nodes) is used for specifying these parameters.

| Usecase | Required parameters |

|---|---|

| Parallel port | Bus width (8/16bit for YUV, 24bit for RGB) |

| Descrete sync | hsync, vsync, pclk polarities |

| Embedded sync | Multiplexing method, channel numbers |

To check if the correct parameters are being passed or not, procfs can be used for checking values of some of the properties on target.

Using procfs to read DT params

cat /proc/device-tree/ocp/i2c@480720000/ov10635@37/compatible

hexdump -b /proc/device-tree/ocp/i2c@480720000/ov10635@37/port/endpoint@0/pclk-sample

hexdump -b /proc/device-tree/ocp/i2c@480720000/ov10635@37/port/endpoint@0/bus-width

hexdump -b /proc/device-tree/ocp/i2c@480720000/ov10635@37/port/endpoint@0/channels

Note that some of the integer properties are not printable in ASCII format. Using hexdump gives readability to read integer values from device tree.

Camera isn’t started, pclk, syncs are dead

Video is being captured but image is pixelated or distorted

FAQ

Can VIP be used as high speed interface to bring any data in?

VIP can be used as high speed interface to bring any data as is (without any modifications) into the device. Following points to keep in mind –

- Data should be sent in discrete sync mode.

- No other VIP internal processing blocks like color space conversion, scaling or chroma format conversion should be used.

- Refer to Driver_Features section if there is need to bring data in resolution greater than the one supported by driver.

- If the cropping feature is disabled in VIP parser due to the need for capturing larger resolution and if interested in capturing last frame (that could be only frame), FPGA need to send additional VSYNC signal else the last frame will not get transferred to DDR.

- Add vip_fmt entry in the vip_formats table inside drivers/media/platform/ti-vpe/vip.c per sub-device driver need for ”.fourcc”, ”.code” and ”.colorspace”. Keep ”.coplanar” as 0. Refer to the entries of VPDMA_DATA_FMT_RAW8 in drivers/media/platform/ti-vpe/vpdma.c file for “vpdma_fmt” settings when using VIP slice in 8 bit port mode. Refer to the VPDMA_DATA_FMT_RAW16 format settings for 16 bit mode. Note that VIP driver supports only 8 bit RAW mode. Enabling 16 bit RAW mode capture needs minor driver modifications. If custom entries are not needed, then any of the raw format entries can be used. In that case, sensor driver will need to configure media bus format as ”.code” settings as shown in the vip_fmt.

static struct vip_fmt vip_formats[VIP_MAX_ACTIVE_FMT] = {

{

.fourcc = V4L2_PIX_FMT_SBGGR8,

.code = MEDIA_BUS_FMT_SBGGR8_1X8,

.colorspace = V4L2_COLORSPACE_SMPTE170M,

.coplanar = 0,

.vpdma_fmt = { &vpdma_raw_fmts[VPDMA_DATA_FMT_RAW8],

},

},

const struct vpdma_data_format vpdma_raw_fmts[] = {

[VPDMA_DATA_FMT_RAW8] = {

.type = VPDMA_DATA_FMT_TYPE_YUV,

.data_type = DATA_TYPE_CBY422,

.depth = 8,

},

What’s the maximum frame rate possible for W*H resolution using VIP?

As mentioned in Hardware_Architecture section, each slice in VIP instance has one 24/16/8 bit port through which data can come in. Each video port can be clocked up to 165 MHz. Assuming 27% left spare for horizontal and vertical blanking, roughly 120 MHz left for actual data. If VIP Slice is configured in 8 bit port mode, then 1 bytes can be brought in per clock cycle. In 8 bit port mode and with 120 MHz clock for data capture, maximum possible capture rate is 120 Mbytes/sec, in 16 bit port mode it will be 240 Mbytes/sec and in 24 bit port mode it will be 360 Mbytes/sec. Now for X*Y resolution, maximum possible frame rate can be calculated using following formula –

FPS = 120 * 1000000 * port_mode/(frame_resolution * num_bytes_per_pixel)

In above formula -

- port_mode can take value of 1 for 8 bit, 2 for 16 bit and 3 for 24 bit port mode configuration.

- Frame_resolution is product of width and height of frame.

- num_bytes_per_pixel is number of bytes per pixel. For example, if capturing in YUYV format it’s value is 2, when capturing in RGB24 format, it’s value is 3.

What is the maximum frame resolution that can be captured using VIP?

Refer to Hardware_Limitations section to understand maximum possible resolution supported by VIP IP. Refer to Unsupported_Features/Limitations section to understand the resolution supported by VIP driver. Driver changes will be needed to capture the resolution beyond the one supported by the driver but within VIP IP limits. Below are suggested modifications inside driver. There may be more changes needed.

- Change MAX_W and MAX_H in vip.c file per the desired capture resolution.

- Disable hardware enabled cropping feature inside the driver if the

desired resolution width is greater than 4K pixels (not bytes) and/or

height is greater than 4K lines.

- To disable cropping, comment the function call to vip_set_crop_parser() function inside vip_setup_parser() function defined in drivers/media/platform/ti-vpe/vip.c file

Why I am not seeing any interrupt generated from the sensor?

Not getting any interrupts usually means the module is not receiving/detecting video data. To proceed with debugging, probe the pclk, vysnc and hsync signal at the connector. If they look as what you are expecting, then verify the pinmux.

How do I capture 10-bit or 12-bit YUV data?

VIP can capture data in 8, 16 or 24 bus-width size. Configure VIP for 16 bit bus-width size in order to capture pixel of 10-bit or 12-bit size. This includes dts file configuration and pin-mux configuration. Connect the pixel size data lanes from the sensor board to VIP input port. Ground or tie to VDD remaining unused pins. VIP will receive the 10-bit/12-bit data in 16-bit container in memory with 6/4 LSb or MSb bit always being low or high based on how those unused bits are tied. Note that when capturing 10-bit/12-bit data in 16 bit container, you can not use any of the VIP internal processing module like scaling, format conversion etc.

In dts file, specify the bus-width field as 16

bus-width = <16>; /* Used data lines */

TI Board Specific Information

None at this time.

3.3.4.5. Crypto¶

Introduction

The Crypto API Driver is a set of Linux drivers that provide access to the hardware cryptographic accelerators available on AM335x/AM437x/AM57x/DRA7 devices. These drivers are available built-in in the kernel in the current SDK release.

Following are the Hardware accelerators supported on the following devices:

* AM335X : MD5, SHA1, SHA224, SHA256, AES, DES

* AM437X : MD5, SHA1, SAH224, SHA256, SHA384, SHA512, AES, DES, DES3DES

* AM57x/DRA7 : AES, DES, DES3DES

Building the Driver

For devices with available cryptographic hardware accelerators, a Linux driver and additionally an Cryptodev (or OCF on AMSDK v6.0 or older) kernel module (for OpenSSL) is needed to access them. Other devices use the pure software implementation of OpenSSL for the crypto demos.

AM335x, AM43xx - AES, DES, SHA/MD5 Drivers

Starting with AMSDK 5.05.00.00, the driver is completely integrated into the kernel source. The pre-built kernel that comes with the SDK already has the AES, DES and SHA/MD5 drivers built-in to the kernel. The kernel configuration has already been set up in the SDK and no further configuration is needed for the drivers to be built-in to the kernel. The configuration of the random number generator does require an extra step and this is detailed in the next section.

For reference, the configuration details are shown below. The configuration of the AES, DES and SHA/MD5 driver is done under the Hardware crypto devices sub-menu of the Cryptographic API menu in the kernel configuration.

--- Cryptographic API

[*] Hardware crypto devices --->

--- Hardware crypto devices

<*> Support for OMAP MD5/SHA1/SHA2 hw accelerator

<*> Support for OMAP AES hw engine

<*> Support for OMAP DES3DES hw engine

Messages printed during bootup will indicate that initialization of the crypto modules has taken place.

[ 2.120565] omap-sham 53100000.sham: hw accel on OMAP rev 4.3

[ 2.160584] mmc1: BKOPS_EN bit is not set

[ 2.173466] omap-aes 53500000.aes: OMAP AES hw accel rev: 3.2

[ 2.180241] edma-dma-engine edma-dma-engine.0: allocated channel for 0:5

[ 2.187808] edma-dma-engine edma-dma-engine.0: allocated channel for 0:6

Build the Cryptodev kernel module using SDK

For using OpenSSL to access the Crypto Hardware Accelerator Drivers above, the Cryptodev is required (can be built as module). The framework is not officially in the kernel and was ported to Linux under the name “cryptodev”.

Using Cryptographic Hardware Accelerators

Using the TRNG Hardware Accelerator

The pre built kernel that come with the SDK already has the TRNG driver built into the kernel. No further configuration is required.

For reference, the configuration details are shown below.

In the configuration menu, scroll down to Device Drivers and hit enter. Now scroll to Character devices and hit enter.

Device Drivers --->

Character devices --->

< > Hardware Random Number Generator Core support

< > OMAP Random Number Generator support

[ 1.660514] omap_rng 48310000.rng: OMAP Random Number Generator ver. 20

root@am335x-evm:~# ls -l /dev/hwrng

crw------- 1 root root 10, 183 Jan 1 2000 /dev/hwrng

root@am335x-evm:~#

root@am335x-evm:~# cat /dev/hwrng | od -x

0000000 b2bd ae08 4477 be48 4836 bf64 5d92 01c9

0000020 0cb6 7ac5 16f9 8616 a483 7dfd 6bf4 3aa5

0000040 d693 db24 d917 5ee7 feb7 34c3 34e9 e7a5

0000060 36b7 ea85 fc17 0e66 555c 0934 7a0c 4c69

0000100 523b 9f21 1546 fddb d58b e5ed 142a 6712

0000120 8d76 8f80 a6d2 30d8 d107 32bc 7f45 f997

0000140 9d5d 0d0c f1f0 64f9 a77f 408f b0c1 f5a0

0000160 39c6 f0ae 4b59 1a76 84a7 a364 8964 f557

root@am335x-evm:~#

Support tools for the hardware random number generator can be loaded from rng-tools on Sourceforge. The latest version at the time of this write-up is version 3.0, dated 2010-07-04.

1. We’re still in the Linux-devkit environment. Download the file rng-tools-3.tar.gz, and untar in a suitable location.

2. Change to the directory that contains the rng-tools distribution, and configure the package:

host $ ./configure --prefix=/home/user/targetfs/TI814x-targetfs_5_03_01/usr \

--exec-prefix=/home/user/targetfs/TI814x-targetfs_5_03_01/usr \

--host --target=arm-linux

3. Next make the rngd and rngtest executables.

host $ make

4. Install the generated executables in the target filesystem.

5. Test the random number generator on the target.

root@am335x-evm:~# cat /dev/hwrng | rngtest -c 1000

rngtest 3

Copyright (c) 2004 by Henrique de Moraes Holschuh

This is free software; see the source for copying conditions. There is NO warranty; not even for MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.

rngtest: starting FIPS tests...

rngtest: bits received from input: 20000032

rngtest: FIPS 140-2 successes: 999

rngtest: FIPS 140-2 failures: 1

rngtest: FIPS 140-2(2001-10-10) Monobit: 0

rngtest: FIPS 140-2(2001-10-10) Poker: 0

rngtest: FIPS 140-2(2001-10-10) Runs: 1

rngtest: FIPS 140-2(2001-10-10) Long run: 0

rngtest: FIPS 140-2(2001-10-10) Continuous run: 0

rngtest: input channel speed: (min=788.218; avg=4070.983; max=2790178.571)Kibits/s

rngtest: FIPS tests speed: (min=846.755; avg=15388.376; max=21920.595)Kibits/s

rngtest: Program run time: 6072670 microseconds

Note that the results may be slightly different on your system, since, after all, we’re dealing with a random number generator. Any appreciable number of errors typically indicates a bad random number generator.

If you’re satisfied the random number generator is working correctly, you can use rngd (the random number generator daemon) to feed the /dev/random entropy pool.

AES, DES, SHA Hardware Accelerators using Cryptodev

The device drivers for AES, DES and SHA/MD5 hardware acceleration is configured and built into the kernel by default. No other special setup is needed for OpenSSL to access the crypto modules.

First, the kernel from the SDK must be configured and built according to the SDK User’s Guide.

The General Purpose (GP) EVMs on TI SoCs allows access to built in cryptographic accelerators. Inorder to use these drivers from OpenSSL, the drivers on their own have no contact with userspace. For this, a special driver is available which abstracts the access to these accelerators through Cryprodev module.

The demo application under the crypto menu of Matrix will load and use the Cryptodev driver kernel modules automatically to perform hardware accelerated crypto functions. The process of manually loading the kernel modules and using the driver is explained below.

Cryptodev is itself a special device driver which provides a general interface for higher level applications such as OpenSSL to access hardware accelerators.

The filesystem which comes with the SDK comes built with the Cryptodev kernel modules and the TI driver which directly accesses the hardware accelerators is built into the kernel.

From the target boards perspective the drivers are located in the following directories:

/lib/modules/`uname -r`/extra/cryptodev.ko

To use the drivers they must first be installed. Use the modprobe command to install the drivers. The following log shows the commands used to install the modules and query the system for the state of all system modules.

root@am335x-evm:~# lsmod

Module Size Used by

cryptodev 11962 0

root@am335x-evm:~#

After the modules are installed, OpenSSL commands may be executed which take advantage of the hardware accelerators through the Cryptodev driver. The following example demonstrates the OpenSSL built-in speed test to demonstrate performance. The addition of the parameter -engine cryptodev tells OpenSSL to use the Cryptodev driver if it exists.

root@am335x-evm:~# openssl speed -evp aes-128-cbc -engine cryptodev

engine "cryptodev" set.

Doing aes-128-cbc for 3s on 16 size blocks: 108107 aes-128-cbc's in 0.16s

Doing aes-128-cbc for 3s on 64 size blocks: 103730 aes-128-cbc's in 0.20s

Doing aes-128-cbc for 3s on 256 size blocks: 15181 aes-128-cbc's in 0.03s

Doing aes-128-cbc for 3s on 1024 size blocks: 15879 aes-128-cbc's in 0.03s

Doing aes-128-cbc for 3s on 8192 size blocks: 4879 aes-128-cbc's in 0.02s

OpenSSL 1.0.0b 16 Nov 2010

built on: Thu Jan 20 10:23:44 CST 2011

options:bn(64,32) rc4(ptr,int) des(idx,risc1,2,long) aes(partial) idea(int) blowfish(idx)

compiler: arm-none-linux-gnueabi-gcc -march=armv7-a -mtune=cortex-a8 -mfpu=neon -mfloat-abi=softfp -mthumb-interwork -mno-thumb -fPS

The 'numbers' are in 1000s of bytes per second processed.

type 16 bytes 64 bytes 256 bytes 1024 bytes 8192 bytes

aes-128-cbc 10810.70k 33193.60k 129544.53k 542003.20k 1998438.40k

root@am335x-evm:~#

root@am335x-evm:~#

root@am335x-evm:~#

Using the Linux time -v function gives more information about CPU usage during the test.

root@am335x-evm:~# time -v openssl speed -evp aes-128-cbc -engine cryptodev

engine "cryptodev" set.

Doing aes-128-cbc for 3s on 16 size blocks: 108799 aes-128-cbc's in 0.17s

Doing aes-128-cbc for 3s on 64 size blocks: 102699 aes-128-cbc's in 0.18s

Doing aes-128-cbc for 3s on 256 size blocks: 16166 aes-128-cbc's in 0.03s

Doing aes-128-cbc for 3s on 1024 size blocks: 15080 aes-128-cbc's in 0.03s

Doing aes-128-cbc for 3s on 8192 size blocks: 4838 aes-128-cbc's in 0.03s

OpenSSL 1.0.0b 16 Nov 2010

built on: Thu Jan 20 10:23:44 CST 2011

options:bn(64,32) rc4(ptr,int) des(idx,risc1,2,long) aes(partial) idea(int) blowfish(idx)

compiler: arm-none-linux-gnueabi-gcc -march=armv7-a -mtune=cortex-a8 -mfpu=neon -mfloat-abi=softfp -mthumb-interwork -mno-thumb -fPS

The 'numbers' are in 1000s of bytes per second processed.

type 16 bytes 64 bytes 256 bytes 1024 bytes 8192 bytes

aes-128-cbc 10239.91k 36515.20k 137949.87k 514730.67k 1321096.53k

Command being timed: "openssl speed -evp aes-128-cbc -engine cryptodev"

User time (seconds): 0.46

System time (seconds): 5.89

Percent of CPU this job got: 42%

Elapsed (wall clock) time (h:mm:ss or m:ss): 0m 15.06s

Average shared text size (kbytes): 0

Average unshared data size (kbytes): 0

Average stack size (kbytes): 0

Average total size (kbytes): 0

Maximum resident set size (kbytes): 7104

Average resident set size (kbytes): 0

Major (requiring I/O) page faults: 0

Minor (reclaiming a frame) page faults: 479

Voluntary context switches: 36143

Involuntary context switches: 211570

Swaps: 0

File system inputs: 0

File system outputs: 0

Socket messages sent: 0

Socket messages received: 0

Signals delivered: 0

Page size (bytes): 4096

Exit status: 0

When the cryptodev driver is removed, OpenSSL reverts to the software implementation of the crypto algorithm. The performance using the software only implementation can be compared to the previous test.

root@am335x-evm:~# modprobe -r cryptodev

root@am335x-evm:~# time -v openssl speed -evp aes-128-cbc

Doing aes-128-cbc for 3s on 16 size blocks: 697674 aes-128-cbc's in 2.99s

Doing aes-128-cbc for 3s on 64 size blocks: 187556 aes-128-cbc's in 3.00s

Doing aes-128-cbc for 3s on 256 size blocks: 47922 aes-128-cbc's in 3.00s

Doing aes-128-cbc for 3s on 1024 size blocks: 12049 aes-128-cbc's in 3.00s

Doing aes-128-cbc for 3s on 8192 size blocks: 1509 aes-128-cbc's in 3.00s

OpenSSL 1.0.0b 16 Nov 2010

built on: Thu Jan 20 10:23:44 CST 2011

options:bn(64,32) rc4(ptr,int) des(idx,risc1,2,long) aes(partial) idea(int) blowfish(idx)

compiler: arm-none-linux-gnueabi-gcc -march=armv7-a -mtune=cortex-a8 -mfpu=neon -mfloat-abi=softfp -mthumb-interwork -mno-thumb -fPS

The 'numbers' are in 1000s of bytes per second processed.

type 16 bytes 64 bytes 256 bytes 1024 bytes 8192 bytes

aes-128-cbc 3733.37k 4001.19k 4089.34k 4112.73k 4120.58k

Command being timed: "openssl speed -evp aes-128-cbc"

User time (seconds): 15.03

System time (seconds): 0.00

Percent of CPU this job got: 99%

Elapsed (wall clock) time (h:mm:ss or m:ss): 0m 15.07s

Average shared text size (kbytes): 0

Average unshared data size (kbytes): 0

Average stack size (kbytes): 0

Average total size (kbytes): 0

Maximum resident set size (kbytes): 7216

Average resident set size (kbytes): 0

Major (requiring I/O) page faults: 1

Minor (reclaiming a frame) page faults: 484

Voluntary context switches: 13

Involuntary context switches: 35

Swaps: 0

File system inputs: 0

File system outputs: 0

Socket messages sent: 0

Socket messages received: 0

Signals delivered: 0

Page size (bytes): 4096

Exit status: 0

3.3.4.6. MCAN¶

Introduction

The Controller Area Network is a serial communications protocol which efficiently supports distributed real-time control with a high level of security. The MCAN module supports bitrates up to 5 Mbit/s and is compliant to the ISO 11898-1:2015. The core IP within M_CAN is provided by Bosch.

This wiki page provides usage information of M_CAN Linux driver.

Setup Details

TI board List

| SoC | Board | Number of Instances | Connection Type | Enabled by default |

|---|---|---|---|---|

| Dra76x | EVM | 1 | Header | Yes |

Table: Boards M_CAN Driver is Validated on

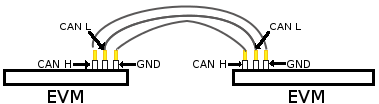

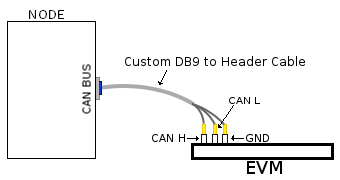

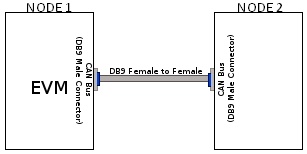

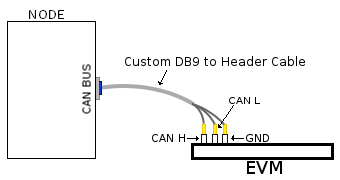

Connection Configuration

|

|

| Header to Header | Header to DB9 |

Table: Various DCAN EVM Connection Configuration

Equipment

Female DB9 Cable

For boards exposing M_CAN using male DB9 connectors, a female connector is required. The other side can be male or female depending on the other CAN device the user connects to.

Jumper Wires

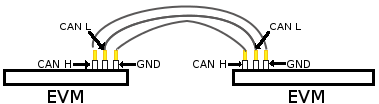

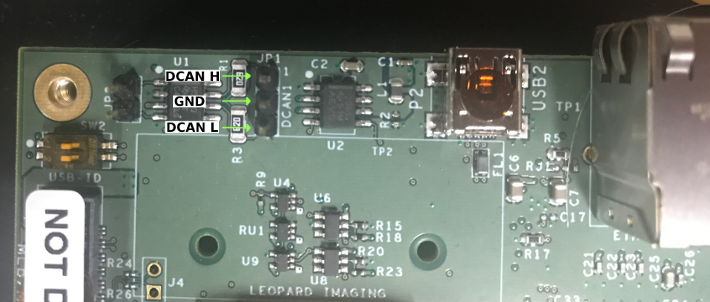

For boards where the CAN pins are broken out via a header, female jumper cables will be ideal for connection. The CAN pins will be CAN H (typically pin 1 of the header), GND (middle pin of the header) and CAN L (lowest pin on the header). The pinout in the header might vary across different boards and users must consult the board’s schematic to verify this.

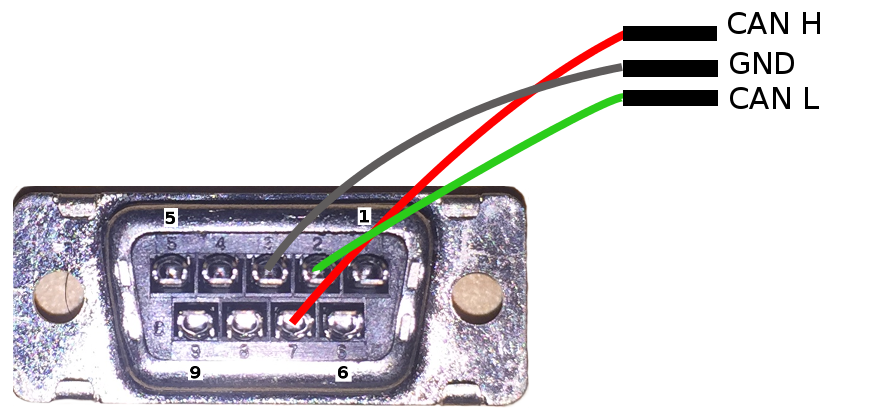

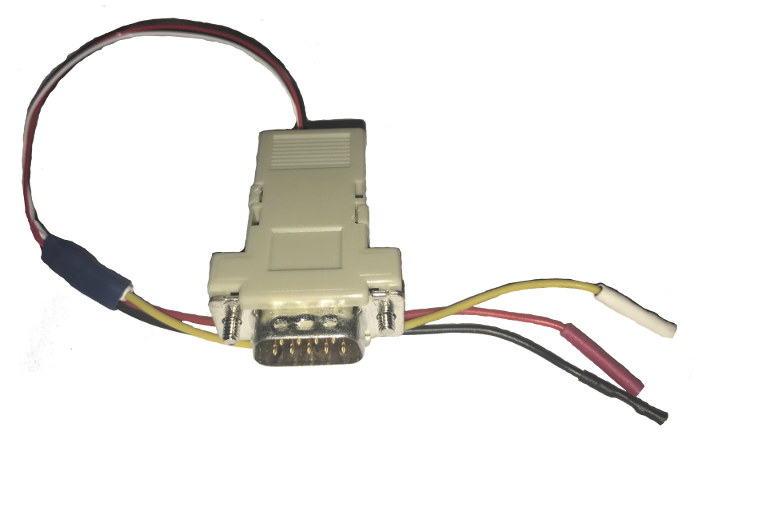

Custom DB9 to Header Cable

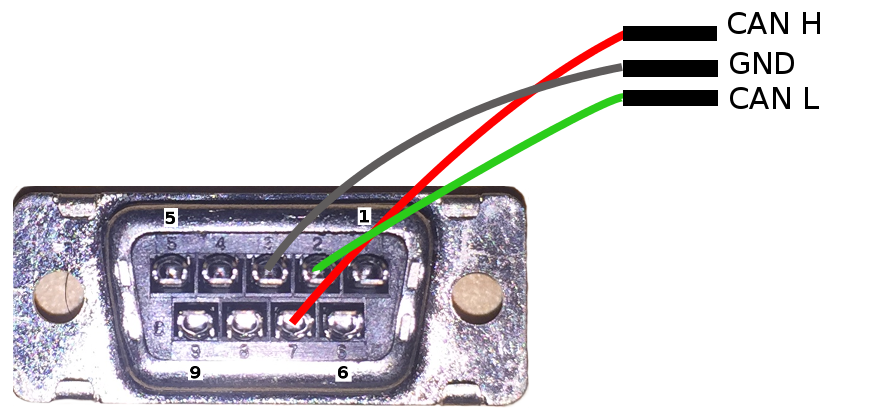

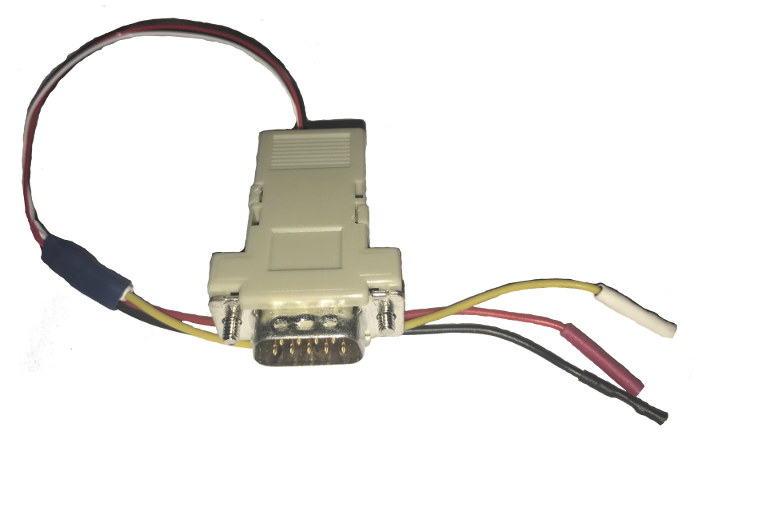

Typically CAN devices use a DB9 connection therefore for boards whose CAN pins are broken out via a header it is helpful to create a header to DB9 connector cable. This custom cable is simple to make. Either a male or female DB9 connector (not cable) must be obtained along with three female jumper wires.

Snip one end of each of the jumper wires and expose some of the wiring. Now solder each of the exposed wires to pin 7 (CAN H), pin 2 (CAN L) and pin 3 (GND). Make sure your soldering on the side of the DB9 that has the metal lip meant to push some of the exposed wire into and soldering to the correct pins correctly. Use the below diagram as a reference.

|

|

| Wiring Diagram | Example of completed cable. |

CAN Utilities

There may be other userspace applications that can be used to interact with the CAN bus but the SDK supports using Canutils which is already included in the sdk filesystem.

Note

These instructions are for can0 (first and perhaps only CAN instance enabled). If the board has multiple CAN instances enabled then they can be referenced by incrementing the CAN instance number. For example 2 CAN instances will have can0 and can1.

Quick Steps

Initialize CAN Bus

- Set bitrate

$ ip link set can0 type can bitrate 1000000

- CAN-FD mode

$ ip link set can0 type can bitrate 1000000 fd on

- CAN-FD mode with bitrate switching

$ ip link set can0 type can bitrate 1000000 dbitrate 4000000 fd on

Start CAN Bus

- Device bring up

Bring up the device using the command:

$ ip link set can0 up

Transfer Packets

Cansend

Used to generate a specific can frame. The syntax for cansend is as follows:

<can_id>#{R|data} for CAN 2.0 frames

<can_id>##<flags>{data} for CAN FD frames

Some examples:

- Send CAN 2.0 frame

$ cansend can0 123#DEADBEEF

- Send CAN FD frame

$ cansend can0 113##2AAAAAAAA

- Send CAN FD frame with BRS

$ cansend can0 143##1AAAAAAAAA

Cangen

Used to generate frames at equal intervals. The syntax for cangen is as follows:

cangen [options] <CAN interface>

Some examples:

- Full load test with polling, 10 ms timeout

$ cangen can0 -g 0 -p 10 -x

b. fixed CAN ID and length, inc. data, canfd frames with bitrate switching

$ cangen vcan0 -g 4 -I 42A -L 1 -D i -v -v -f -b

Candump

Candump is used to display received frames.

candump [options] <CAN interface>

Example:

$ candump can0

Note: Use Ctrl-C to terminate candump

Further options for all canutils commands are available at https://git.pengutronix.de/cgit/tools/canutils

Stop CAN Bus

Stop the can bus by:

$ ip link set can0 down

3.3.4.7. DCAN¶

Introduction

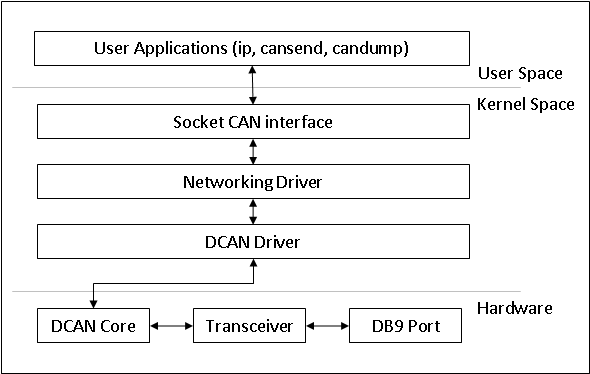

The Controller Area Network is a serial communications protocol which efficiently supports distributed real-time control with a high level of security. The DCAN module supports bitrates up to 1 Mbit/s and is compliant to the CAN 2.0B protocol specification. The core IP within DCAN is provided by Bosch.

This wiki page provides usage information of DCAN Linux driver.

Acronyms & definitions

| Acronym | Definition |

|---|---|

| CAN | Controller Area Network |

| BTL | Bit timing logic |

| DLC | Data Length Code |

| MO | Message Object |

| LEC | Last Error Code |

| FSM | Finite State Machine |

| CRC | Cyclic Redundancy Check |

Table: DCAN Driver: Acronyms

Setup Details

EVM List

| SoC | EVM | Number of Instances | Connection Type | Enabled by default |

|---|---|---|---|---|

| AM335x | General Purpose EVM | 1 | DB9 | No |

| AM437x | General Purpose EVM | 2 | DB9 | Yes |

| 66AK2Gx | General Purpose EVM | 2 | DB9 | Yes |

| AM571x | Industrial Development Kit | 1 | Header | Yes |

| DRA74x | Evaluation Module | 1 | Header | Yes |

| DRA72x | Evaluation Module | 1 | Header | Yes |

Table: EVMs DCAN Driver is Validated on

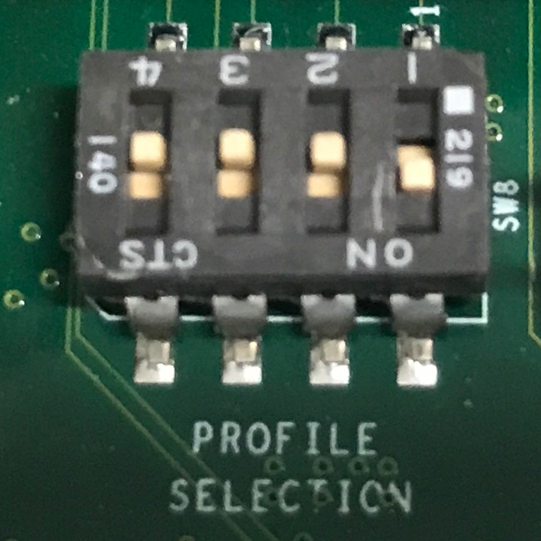

NOTE On AM335x GP EVM CAN does not work by default. The evm must have its “Profile Switch” set to 1 to enable CAN support.

Hardware/Software Changes to Enable CAN Support

AM335x General Purpose EVM