|

|

|

SimpleLink MCU SDK Driver APIs

tidrivers_msp43x_3_01_01_03

|

SPI driver implementation for a EUSCI peripheral on MSP432 using the micro DMA controller.

============================================================================

The SPI header file should be included in an application as follows:

Refer to SPI.h for a complete description of APIs & example of use.

This SPI driver implementation is designed to operate on a EUCSI controller in SPI mode.

The SPIMSP432DMA operates the controller in 3-pin mode; therefore it is not safe to use in a multi-master SPI bus environment. It is the application's responsibility to assert and de-assert a GPIO pin for chip select purposes.

| Chip select type | SPI_MASTER mode | SPI_SLAVE mode |

|---|---|---|

| Hardware chip select | Not available on this peripheral. | |

| Software chip select | The application is responsible to ensure that correct SPI slave is selected before performing a SPI_transfer(). | Up to the application's implementation. |

The MSP432 DMA controller has 4 interrupt vectors to handle all DMA related IRQ. Due to the "shared" nature of the DMA interrupts, this driver implementation requires each SPI instance to explicitly use a single DMA interrupt. It is up to the application to ensure no two peripherals are configured to respond to a given DMA interrupt at any moment.

A uint32_t scratch buffer is used to allow SPI_transfers where txBuf or rxBuf are NULL. Rather than requiring txBuf or rxBuf to have a dummy buffer of size of the transfer count, a single DMA accessible uint32_t scratch buffer is used. When txBuf is NULL, an internal scratch buffer is initialized to the defaultTxBufValue so the DMA will send some known value. Each SPI driver instance should uses its own scratch buffer.

The EUSCI controller only supports 8-bit data frames.

| dataSize | buffer element size |

|---|---|

| 8 bits | uint8_t |

The DMA contoller only supports data transfers of upto 1024 data frames. Each SPI driver instance requires 2 DMA channels (Tx and Rx) to operate.

Ensure that the txBuf and rxBuf (in SPI_Transaction) point to memory that is accessible by the DMA.

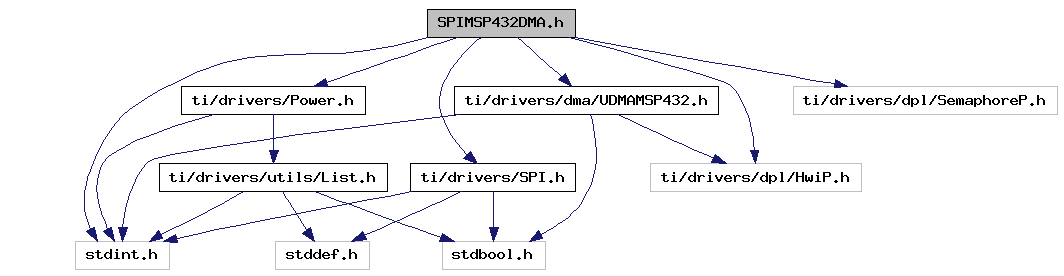

#include <stdint.h>#include <ti/drivers/dpl/HwiP.h>#include <ti/drivers/dpl/SemaphoreP.h>#include <ti/drivers/Power.h>#include <ti/drivers/SPI.h>#include <ti/drivers/dma/UDMAMSP432.h>

Go to the source code of this file.

Data Structures | |

| struct | SPIMSP432DMA_HWAttrsV1 |

| SPIMSP432DMA Hardware attributes These fields, with the exception of intPriority, are used by driverlib APIs and therefore must be populated by driverlib macro definitions. For MSP432 driverlib these definitions are found in: More... | |

| struct | SPIMSP432DMA_Object |

| SPIMSP432DMA Object. More... | |

Macros | |

| #define | SPIMSP432DMA_P1_0_UCA0STE 0x00000110 /* Primary, port 1, pin 0 */ |

| #define | SPIMSP432DMA_P1_1_UCA0CLK 0x00000111 /* Primary, port 1, pin 1 */ |

| #define | SPIMSP432DMA_P1_2_UCA0SOMI 0x00000112 /* Primary, port 1, pin 2 */ |

| #define | SPIMSP432DMA_P1_3_UCA0SIMO 0x00000113 /* Primary, port 1, pin 3 */ |

| #define | SPIMSP432DMA_P1_4_UCB0STE 0x00000114 /* Primary, port 1, pin 4 */ |

| #define | SPIMSP432DMA_P1_5_UCB0CLK 0x00000115 /* Primary, port 1, pin 5 */ |

| #define | SPIMSP432DMA_P1_6_UCB0SIMO 0x00000116 /* Primary, port 1, pin 6 */ |

| #define | SPIMSP432DMA_P1_7_UCB0SOMI 0x00000117 /* Primary, port 1, pin 7 */ |

| #define | SPIMSP432DMA_P2_0_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCA1STE ((PMAP_UCA1STE << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCA2STE ((PMAP_UCA2STE << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_0_UCB2STE ((PMAP_UCB2STE << 10) | 0x20) |

| #define | SPIMSP432DMA_P2_1_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCA1STE ((PMAP_UCA1STE << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCA2STE ((PMAP_UCA2STE << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_1_UCB2STE ((PMAP_UCB2STE << 10) | 0x21) |

| #define | SPIMSP432DMA_P2_2_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCA1STE ((PMAP_UCA1STE << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCA2STE ((PMAP_UCA2STE << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_2_UCB2STE ((PMAP_UCB2STE << 10) | 0x22) |

| #define | SPIMSP432DMA_P2_3_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCA1STE ((PMAP_UCA1STE << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCA2STE ((PMAP_UCA2STE << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_3_UCB2STE ((PMAP_UCB2STE << 10) | 0x23) |

| #define | SPIMSP432DMA_P2_4_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCA1STE ((PMAP_UCA1STE << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCA2STE ((PMAP_UCA2STE << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_4_UCB2STE ((PMAP_UCB2STE << 10) | 0x24) |

| #define | SPIMSP432DMA_P2_5_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCA1STE ((PMAP_UCA1STE << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCA2STE ((PMAP_UCA2STE << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_5_UCB2STE ((PMAP_UCB2STE << 10) | 0x25) |

| #define | SPIMSP432DMA_P2_6_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCA1STE ((PMAP_UCA1STE << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCA2STE ((PMAP_UCA2STE << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_6_UCB2STE ((PMAP_UCB2STE << 10) | 0x26) |

| #define | SPIMSP432DMA_P2_7_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCA1STE ((PMAP_UCA1STE << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCA2STE ((PMAP_UCA2STE << 10) | 0x27) |

| #define | SPIMSP432DMA_P2_7_UCB2STE ((PMAP_UCB2STE << 10) | 0x27) |

| #define | SPIMSP432DMA_P3_0_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCA2STE ((PMAP_UCA2STE << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCA1STE ((PMAP_UCA1STE << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_0_UCB2STE ((PMAP_UCB2STE << 10) | 0x30) |

| #define | SPIMSP432DMA_P3_1_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCA1STE ((PMAP_UCA1STE << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCA2STE ((PMAP_UCA2STE << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_1_UCB2STE ((PMAP_UCB2STE << 10) | 0x31) |

| #define | SPIMSP432DMA_P3_2_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCA1STE ((PMAP_UCA1STE << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCA2STE ((PMAP_UCA2STE << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_2_UCB2STE ((PMAP_UCB2STE << 10) | 0x32) |

| #define | SPIMSP432DMA_P3_3_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCA1STE ((PMAP_UCA1STE << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCA2STE ((PMAP_UCA2STE << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_3_UCB2STE ((PMAP_UCB2STE << 10) | 0x33) |

| #define | SPIMSP432DMA_P3_4_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCB2STE ((PMAP_UCB2STE << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCA1STE ((PMAP_UCA1STE << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_4_UCA2STE ((PMAP_UCA2STE << 10) | 0x34) |

| #define | SPIMSP432DMA_P3_5_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCA1STE ((PMAP_UCA1STE << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCA2STE ((PMAP_UCA2STE << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_5_UCB2STE ((PMAP_UCB2STE << 10) | 0x35) |

| #define | SPIMSP432DMA_P3_6_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCA1STE ((PMAP_UCA1STE << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCA2STE ((PMAP_UCA2STE << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_6_UCB2STE ((PMAP_UCB2STE << 10) | 0x36) |

| #define | SPIMSP432DMA_P3_7_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCA1STE ((PMAP_UCA1STE << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCA2STE ((PMAP_UCA2STE << 10) | 0x37) |

| #define | SPIMSP432DMA_P3_7_UCB2STE ((PMAP_UCB2STE << 10) | 0x37) |

| #define | SPIMSP432DMA_P6_2_UCB1STE 0x00000162 /* Primary, port 6, pin 2 */ |

| #define | SPIMSP432DMA_P6_3_UCB1CLK 0x00000163 /* Primary, port 6, pin 3 */ |

| #define | SPIMSP432DMA_P6_4_UCB1SIMO 0x00000164 /* Primary, port 6, pin 4 */ |

| #define | SPIMSP432DMA_P6_5_UCB1SOMI 0x00000165 /* Primary, port 6, pin 5 */ |

| #define | SPIMSP432DMA_P6_6_UCB3SIMO 0x00000266 /* Secondary, port 6, pin 6 */ |

| #define | SPIMSP432DMA_P6_7_UCB3SOMI 0x00000267 /* Secondary, port 6, pin 7 */ |

| #define | SPIMSP432DMA_P7_0_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCA1STE ((PMAP_UCA1STE << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCA2STE ((PMAP_UCA2STE << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_0_UCB2STE ((PMAP_UCB2STE << 10) | 0x70) |

| #define | SPIMSP432DMA_P7_1_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCA1STE ((PMAP_UCA1STE << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCA2STE ((PMAP_UCA2STE << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_1_UCB2STE ((PMAP_UCB2STE << 10) | 0x71) |

| #define | SPIMSP432DMA_P7_2_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCA1STE ((PMAP_UCA1STE << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCA2STE ((PMAP_UCA2STE << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_2_UCB2STE ((PMAP_UCB2STE << 10) | 0x72) |

| #define | SPIMSP432DMA_P7_3_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCA1STE ((PMAP_UCA1STE << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCA2STE ((PMAP_UCA2STE << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_3_UCB2STE ((PMAP_UCB2STE << 10) | 0x73) |

| #define | SPIMSP432DMA_P7_4_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCA1STE ((PMAP_UCA1STE << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCA2STE ((PMAP_UCA2STE << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_4_UCB2STE ((PMAP_UCB2STE << 10) | 0x74) |

| #define | SPIMSP432DMA_P7_5_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCA1STE ((PMAP_UCA1STE << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCA2STE ((PMAP_UCA2STE << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_5_UCB2STE ((PMAP_UCB2STE << 10) | 0x75) |

| #define | SPIMSP432DMA_P7_6_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCA1STE ((PMAP_UCA1STE << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCA2STE ((PMAP_UCA2STE << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_6_UCB2STE ((PMAP_UCB2STE << 10) | 0x76) |

| #define | SPIMSP432DMA_P7_7_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCA1STE ((PMAP_UCA1STE << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCA2STE ((PMAP_UCA2STE << 10) | 0x77) |

| #define | SPIMSP432DMA_P7_7_UCB2STE ((PMAP_UCB2STE << 10) | 0x77) |

| #define | SPIMSP432DMA_P8_0_UCB3STE 0x00000180 /* Primary, port 8, pin 0 */ |

| #define | SPIMSP432DMA_P8_1_UCB3CLK 0x00000181 /* Primary, port 8, pin 1 */ |

| #define | SPIMSP432DMA_P9_4_UCA3STE 0x00000194 /* Primary, port 9, pin 4 */ |

| #define | SPIMSP432DMA_P9_5_UCA3CLK 0x00000195 /* Primary, port 9, pin 5 */ |

| #define | SPIMSP432DMA_P9_6_UCA3SOMI 0x00000196 /* Primary, port 9, pin 6 */ |

| #define | SPIMSP432DMA_P9_7_UCA3SIMO 0x00000197 /* Primary, port 9, pin 7 */ |

| #define | SPIMSP432DMA_P10_0_UCB3STE 0x000001A0 /* Primary, port 10, pin 0 */ |

| #define | SPIMSP432DMA_P10_1_UCB3CLK 0x000001A1 /* Primary, port 10, pin 1 */ |

| #define | SPIMSP432DMA_P10_2_UCB3SIMO 0x000001A2 /* Primary, port 10, pin 2 */ |

| #define | SPIMSP432DMA_P10_3_UCB3SOMI 0x000001A3 /* Primary, port 10, pin 3 */ |

Typedefs | |

| typedef struct SPIMSP432DMA_HWAttrsV1 | SPIMSP432DMA_HWAttrsV1 |

| SPIMSP432DMA Hardware attributes These fields, with the exception of intPriority, are used by driverlib APIs and therefore must be populated by driverlib macro definitions. For MSP432 driverlib these definitions are found in: More... | |

| typedef struct SPIMSP432DMA_Object | SPIMSP432DMA_Object |

| SPIMSP432DMA Object. More... | |

| typedef struct SPIMSP432DMA_Object * | SPIMSP432DMA_Handle |

Variables | |

| const SPI_FxnTable | SPIMSP432DMA_fxnTable |

| #define SPIMSP432DMA_P1_0_UCA0STE 0x00000110 /* Primary, port 1, pin 0 */ |

| #define SPIMSP432DMA_P1_1_UCA0CLK 0x00000111 /* Primary, port 1, pin 1 */ |

| #define SPIMSP432DMA_P1_2_UCA0SOMI 0x00000112 /* Primary, port 1, pin 2 */ |

| #define SPIMSP432DMA_P1_3_UCA0SIMO 0x00000113 /* Primary, port 1, pin 3 */ |

| #define SPIMSP432DMA_P1_4_UCB0STE 0x00000114 /* Primary, port 1, pin 4 */ |

| #define SPIMSP432DMA_P1_5_UCB0CLK 0x00000115 /* Primary, port 1, pin 5 */ |

| #define SPIMSP432DMA_P1_6_UCB0SIMO 0x00000116 /* Primary, port 1, pin 6 */ |

| #define SPIMSP432DMA_P1_7_UCB0SOMI 0x00000117 /* Primary, port 1, pin 7 */ |

| #define SPIMSP432DMA_P2_0_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCA1STE ((PMAP_UCA1STE << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCA2STE ((PMAP_UCA2STE << 10) | 0x20) |

| #define SPIMSP432DMA_P2_0_UCB2STE ((PMAP_UCB2STE << 10) | 0x20) |

| #define SPIMSP432DMA_P2_1_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCA1STE ((PMAP_UCA1STE << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCA2STE ((PMAP_UCA2STE << 10) | 0x21) |

| #define SPIMSP432DMA_P2_1_UCB2STE ((PMAP_UCB2STE << 10) | 0x21) |

| #define SPIMSP432DMA_P2_2_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCA1STE ((PMAP_UCA1STE << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCA2STE ((PMAP_UCA2STE << 10) | 0x22) |

| #define SPIMSP432DMA_P2_2_UCB2STE ((PMAP_UCB2STE << 10) | 0x22) |

| #define SPIMSP432DMA_P2_3_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCA1STE ((PMAP_UCA1STE << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCA2STE ((PMAP_UCA2STE << 10) | 0x23) |

| #define SPIMSP432DMA_P2_3_UCB2STE ((PMAP_UCB2STE << 10) | 0x23) |

| #define SPIMSP432DMA_P2_4_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCA1STE ((PMAP_UCA1STE << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCA2STE ((PMAP_UCA2STE << 10) | 0x24) |

| #define SPIMSP432DMA_P2_4_UCB2STE ((PMAP_UCB2STE << 10) | 0x24) |

| #define SPIMSP432DMA_P2_5_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCA1STE ((PMAP_UCA1STE << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCA2STE ((PMAP_UCA2STE << 10) | 0x25) |

| #define SPIMSP432DMA_P2_5_UCB2STE ((PMAP_UCB2STE << 10) | 0x25) |

| #define SPIMSP432DMA_P2_6_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCA1STE ((PMAP_UCA1STE << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCA2STE ((PMAP_UCA2STE << 10) | 0x26) |

| #define SPIMSP432DMA_P2_6_UCB2STE ((PMAP_UCB2STE << 10) | 0x26) |

| #define SPIMSP432DMA_P2_7_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCA1STE ((PMAP_UCA1STE << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCA2STE ((PMAP_UCA2STE << 10) | 0x27) |

| #define SPIMSP432DMA_P2_7_UCB2STE ((PMAP_UCB2STE << 10) | 0x27) |

| #define SPIMSP432DMA_P3_0_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCA2STE ((PMAP_UCA2STE << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCA1STE ((PMAP_UCA1STE << 10) | 0x30) |

| #define SPIMSP432DMA_P3_0_UCB2STE ((PMAP_UCB2STE << 10) | 0x30) |

| #define SPIMSP432DMA_P3_1_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCA1STE ((PMAP_UCA1STE << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCA2STE ((PMAP_UCA2STE << 10) | 0x31) |

| #define SPIMSP432DMA_P3_1_UCB2STE ((PMAP_UCB2STE << 10) | 0x31) |

| #define SPIMSP432DMA_P3_2_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCA1STE ((PMAP_UCA1STE << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCA2STE ((PMAP_UCA2STE << 10) | 0x32) |

| #define SPIMSP432DMA_P3_2_UCB2STE ((PMAP_UCB2STE << 10) | 0x32) |

| #define SPIMSP432DMA_P3_3_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCA1STE ((PMAP_UCA1STE << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCA2STE ((PMAP_UCA2STE << 10) | 0x33) |

| #define SPIMSP432DMA_P3_3_UCB2STE ((PMAP_UCB2STE << 10) | 0x33) |

| #define SPIMSP432DMA_P3_4_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCB2STE ((PMAP_UCB2STE << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCA1STE ((PMAP_UCA1STE << 10) | 0x34) |

| #define SPIMSP432DMA_P3_4_UCA2STE ((PMAP_UCA2STE << 10) | 0x34) |

| #define SPIMSP432DMA_P3_5_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCA1STE ((PMAP_UCA1STE << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCA2STE ((PMAP_UCA2STE << 10) | 0x35) |

| #define SPIMSP432DMA_P3_5_UCB2STE ((PMAP_UCB2STE << 10) | 0x35) |

| #define SPIMSP432DMA_P3_6_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCA1STE ((PMAP_UCA1STE << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCA2STE ((PMAP_UCA2STE << 10) | 0x36) |

| #define SPIMSP432DMA_P3_6_UCB2STE ((PMAP_UCB2STE << 10) | 0x36) |

| #define SPIMSP432DMA_P3_7_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCA1STE ((PMAP_UCA1STE << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCA2STE ((PMAP_UCA2STE << 10) | 0x37) |

| #define SPIMSP432DMA_P3_7_UCB2STE ((PMAP_UCB2STE << 10) | 0x37) |

| #define SPIMSP432DMA_P6_2_UCB1STE 0x00000162 /* Primary, port 6, pin 2 */ |

| #define SPIMSP432DMA_P6_3_UCB1CLK 0x00000163 /* Primary, port 6, pin 3 */ |

| #define SPIMSP432DMA_P6_4_UCB1SIMO 0x00000164 /* Primary, port 6, pin 4 */ |

| #define SPIMSP432DMA_P6_5_UCB1SOMI 0x00000165 /* Primary, port 6, pin 5 */ |

| #define SPIMSP432DMA_P6_6_UCB3SIMO 0x00000266 /* Secondary, port 6, pin 6 */ |

| #define SPIMSP432DMA_P6_7_UCB3SOMI 0x00000267 /* Secondary, port 6, pin 7 */ |

| #define SPIMSP432DMA_P7_0_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCA1STE ((PMAP_UCA1STE << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCA2STE ((PMAP_UCA2STE << 10) | 0x70) |

| #define SPIMSP432DMA_P7_0_UCB2STE ((PMAP_UCB2STE << 10) | 0x70) |

| #define SPIMSP432DMA_P7_1_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCA1STE ((PMAP_UCA1STE << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCA2STE ((PMAP_UCA2STE << 10) | 0x71) |

| #define SPIMSP432DMA_P7_1_UCB2STE ((PMAP_UCB2STE << 10) | 0x71) |

| #define SPIMSP432DMA_P7_2_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCA1STE ((PMAP_UCA1STE << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCA2STE ((PMAP_UCA2STE << 10) | 0x72) |

| #define SPIMSP432DMA_P7_2_UCB2STE ((PMAP_UCB2STE << 10) | 0x72) |

| #define SPIMSP432DMA_P7_3_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCA1STE ((PMAP_UCA1STE << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCA2STE ((PMAP_UCA2STE << 10) | 0x73) |

| #define SPIMSP432DMA_P7_3_UCB2STE ((PMAP_UCB2STE << 10) | 0x73) |

| #define SPIMSP432DMA_P7_4_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCA1STE ((PMAP_UCA1STE << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCA2STE ((PMAP_UCA2STE << 10) | 0x74) |

| #define SPIMSP432DMA_P7_4_UCB2STE ((PMAP_UCB2STE << 10) | 0x74) |

| #define SPIMSP432DMA_P7_5_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCA1STE ((PMAP_UCA1STE << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCA2STE ((PMAP_UCA2STE << 10) | 0x75) |

| #define SPIMSP432DMA_P7_5_UCB2STE ((PMAP_UCB2STE << 10) | 0x75) |

| #define SPIMSP432DMA_P7_6_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCA1STE ((PMAP_UCA1STE << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCA2STE ((PMAP_UCA2STE << 10) | 0x76) |

| #define SPIMSP432DMA_P7_6_UCB2STE ((PMAP_UCB2STE << 10) | 0x76) |

| #define SPIMSP432DMA_P7_7_UCA0CLK ((PMAP_UCA0CLK << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCA0SIMO ((PMAP_UCA0SIMO << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCA0SOMI ((PMAP_UCA0SOMI << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCA1CLK ((PMAP_UCA1CLK << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCA1SIMO ((PMAP_UCA1SIMO << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCA1SOMI ((PMAP_UCA1SOMI << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCA2CLK ((PMAP_UCA2CLK << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCA2SIMO ((PMAP_UCA2SIMO << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCA2SOMI ((PMAP_UCA2SOMI << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCB0CLK ((PMAP_UCB0CLK << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCB0SIMO ((PMAP_UCB0SIMO << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCB0SOMI ((PMAP_UCB0SOMI << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCB2CLK ((PMAP_UCB2CLK << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCB2SIMO ((PMAP_UCB2SIMO << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCB2SOMI ((PMAP_UCB2SOMI << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCA1STE ((PMAP_UCA1STE << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCA2STE ((PMAP_UCA2STE << 10) | 0x77) |

| #define SPIMSP432DMA_P7_7_UCB2STE ((PMAP_UCB2STE << 10) | 0x77) |

| #define SPIMSP432DMA_P8_0_UCB3STE 0x00000180 /* Primary, port 8, pin 0 */ |

| #define SPIMSP432DMA_P8_1_UCB3CLK 0x00000181 /* Primary, port 8, pin 1 */ |

| #define SPIMSP432DMA_P9_4_UCA3STE 0x00000194 /* Primary, port 9, pin 4 */ |

| #define SPIMSP432DMA_P9_5_UCA3CLK 0x00000195 /* Primary, port 9, pin 5 */ |

| #define SPIMSP432DMA_P9_6_UCA3SOMI 0x00000196 /* Primary, port 9, pin 6 */ |

| #define SPIMSP432DMA_P9_7_UCA3SIMO 0x00000197 /* Primary, port 9, pin 7 */ |

| #define SPIMSP432DMA_P10_0_UCB3STE 0x000001A0 /* Primary, port 10, pin 0 */ |

| #define SPIMSP432DMA_P10_1_UCB3CLK 0x000001A1 /* Primary, port 10, pin 1 */ |

| #define SPIMSP432DMA_P10_2_UCB3SIMO 0x000001A2 /* Primary, port 10, pin 2 */ |

| #define SPIMSP432DMA_P10_3_UCB3SOMI 0x000001A3 /* Primary, port 10, pin 3 */ |

| typedef struct SPIMSP432DMA_HWAttrsV1 SPIMSP432DMA_HWAttrsV1 |

SPIMSP432DMA Hardware attributes These fields, with the exception of intPriority, are used by driverlib APIs and therefore must be populated by driverlib macro definitions. For MSP432 driverlib these definitions are found in:

intPriority is the SPI peripheral's interrupt priority, as defined by the underlying OS. It is passed unmodified to the underlying OS's interrupt handler creation code, so you need to refer to the OS documentation for usage. For example, for SYS/BIOS applications, refer to the ti.sysbios.family.arm.m3.Hwi documentation for SYS/BIOS usage of interrupt priorities. If the driver uses the ti.dpl interface instead of making OS calls directly, then the HwiP port handles the interrupt priority in an OS specific way. In the case of the SYS/BIOS port, intPriority is passed unmodified to Hwi_create().

A sample structure is shown below:

| typedef struct SPIMSP432DMA_Object SPIMSP432DMA_Object |

SPIMSP432DMA Object.

The application must not access any member variables of this structure!

| typedef struct SPIMSP432DMA_Object * SPIMSP432DMA_Handle |

| const SPI_FxnTable SPIMSP432DMA_fxnTable |