6.1. CSL¶

Overview

The Chip Support Library constitutes a set of well-defined APIs that abstract low-level details of the underlying SoC device so that a user can configure, control (start/stop, etc.) and have read/write access to peripherals without having to worry about register bit-field details. The CSL services are implemented as distinct modules that correspond with the underlying SoC device modules themselves. By design, CSL APIs follow a consistent style, uniformly across Processor Instruction Set Architecture and are independent of the OS. This helps in improving portability of code written using the CSL.

CSL is realized as twin-layer – a basic register-layer and a more abstracted functional-layer. The lower register layer comprises of a very basic set of macros and type definitions. The upper functional layer comprises of “C” functions that provide an increased degree of abstraction, but intended to provide “directed” control of underlying hardware.

It is important to note that CSL does not manage data-movement over underlying h/w devices. Such functionality is considered a prerogative of a device-driver and serious effort is made to not blur the boundary between device-driver and CSL services in this regard.

CSL does not model the device state machine. However, should there exist a mandatory (hardware dictated) sequence (possibly atomically executed) of register reads/writes to setup the device in chosen “operating modes” as per the device data sheet, then CSL does indeed support services for such operations.

The CSL services are decomposed into modules, each following the twin-layer of abstraction described above. The APIs of each such module are completely orthogonal (one module’s API does not internally call API of another module) and do not allocate memory dynamically from within. This is key to keeping CSL scalable to fit the specific usage scenarios and ease the effort to ROM a CSL based application.

In general for application recommended interfaces to be used will be driver API. CSL Functional layer APIs could be used for low-level access when required. CSL Register layer memory map is available for being used under rare cases in application when required.

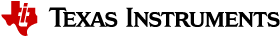

The source code of the CSL is located under $(TI_PDK_INSTALL_DIR)\packages\ti\csl directory.

AM335x/AM437x

The CSL component of AM335x/AM437x Processor SDK is referred as StarterWare in the legacy baseline releases.To maintain backward compatibility for existing applications on AM335x/AM437x SOCs, StarterWare low level package is retained. Customers are recommended to use driver interfaces for ease of migration of application software across SOCs.

| Chip Support Library/DAL Summary | |

|---|---|

| Component Type | Library |

| Install Package | PDK |

| Install Directory | pdk_AMX_<version>\packages\ti\starterware |

| Endian Support | Little |

| Linker Path | PDK_INSTALL_DIR\packages\ti\starterware\binary |

| Include Paths | PDK_INSTALL_DIR\packages\ti\starterware\include |

6.1.1. AM57x/K2x/C66x/C674x¶

6.1.1.1. Application Integration¶

CSL is common package supporting multiple devices.Software layer using CSL source would need to pass compile time define -DSOC_XXX. Refer ticslsoc.h for list of devices/SOC’s

Refer list of APIs/interfaces available under <PDK_INSTALL_DIR\packages\ti\csl> directory.

| Chip Support Library Summary | |

|---|---|

| Component Type | Library |

| Install Package | PDK |

| Install Directory | PDK_INSTALL_DIR\packages\ti\csl |

| Endian Support | Little |

| Linker Path | PDK_INSTALL_DIR\packages\ti\csl |

| Include Paths | $(TI_PDK_INSTALL_DIR)\packages\ |

| Reference Guides | See docs under Install Directory |

6.1.2. CSL-FL EXAMPLES¶

These are example projects to test the functionality of API in CSL-FL layers. The following is the list of CSL-FL test examples which are supported with the CSL library:

- DCAN

- EDMA

- GPIO

- MAILBOX

- I2C

- QSPI

- WDTIMER

- MMCSD

- MMU

- SPINLOCK

- UART

- ECC : Limited to applicable SOC’s/Boards:idkAM574x

In order build the projects:

- Navigate to pdk_[soc]_[version]\packages

- Run pdksetupenv.bat (windows) OR pdksetupenv.sh (linux).

- Navigate to pdk_[soc]_[version]\packages\ti\csl

All CSL-FL examples can be cleaned and rebuilt with the following commands on windows:

C:\ti\pdk_[soc]_[version]\packages\ti\csl>gmake app_clean

C:\ti\pdk_[soc]_[version]\packages\ti\csl>gmake apps

All CSL-FL examples can be cleaned and rebuilt with the following commands on linux:

~/ti/pdk_[soc]_[version]/packages/ti/csl$ make app_clean

~/ti/pdk_[soc]_[version]/packages/ti/csl$ make apps

- All the output binary files will be generated in common location i.e. pdk_[soc]_[version]\packages\ti\binary\[EXAMPLE]\bin\[BOARD]\

- DCAN RTOS example

TI RTOS support is available for CSL DCAN example on AM572x platform. Refer to the readme document at below path for more details.

<PDK Root>/packages/ti/csl/example/dcan/dcanLoopback

6.2. UART¶

6.2.1. Overview¶

6.2.1.1. Introduction¶

Driver enables UART’s available on SOC for reading and writing to any peripherals on board. Additionally it supports simple APIs for Console/STDIO operations.

Modes of Operation

Following modes of operations are supported

UART_MODE_BLOCKING: In this mode, read and write APIs, blocks on semaphore until required operation is complete. By default, UART driver operates in blocking mode. In this mode, code execution of a task blocks until UART transaction is complete. While transaction is in progress additional tasks pending requests will remain in blocked state waiting for semaphore.

UART_MODE_CALLBACK: In this mode, read and write operation returns immediately. On trigger of hardware Interrupt (hwi) callback function gets triggered.

6.2.2. User Interface¶

6.2.2.1. Driver Configuration¶

Board Specific Configuration

All board specific configurations eg:enabling clock and pin-mux for UART pins are required before calling any driver APIs.By default Board_Init() API supports all initialization sequence for TI supported EVMs. In addition it initializes UART instance for Console/STDIO.Refer Processor SDK RTOS Board Support for additional details.Once board specific configuration is complete UART_init() API can be called to initialize driver.

UART Configuration Structure

The UART_soc.c file binds driver with hardware attributes on the board through UART_config structure. This structure must be provided to UART driver. It must be initialized before the UART_init() function is called and cannot be changed afterwards. For details about individual fields of this structure, see the Doxygen help by opening PDK_INSTALL_DIRpackagestidrvuartdocsdoxygenhtmlindex.html.

6.2.2.2. APIs¶

API reference for application:

#include <ti/drv/uart/UART.h>

STDIO API reference for application:

#include <ti/drv/uart/UART_stdio.h>

Open UART

There are three ways to open a UART instance:

- UART_open()

...

Board_init(boardCfg);

...

UART_socGetInitCfg(UART_INSTANCE, &uart_cfg);

...

UART_socSetInitCfg(UART_INSTANCE, &uart_cfg);

...

UART_Params_init(¶ms);

...

handle = UART_open(UART_INSTANCE, ¶ms);

At this point UART driver is ready for data transfer on specific instance identified by handle. Application can call UART_read/write API for read/write operation

- UART_stdioInit() using the default UART parameters

...

Board_init(boardCfg);

...

UART_socGetInitCfg(UART_INSTANCE, &uart_cfg);

...

UART_socSetInitCfg(UART_INSTANCE, &uart_cfg);

...

UART_stdioInit(UART_INSTANCE);

At this point UART driver is ready for data transfer on specific instance. Application can call UART_printf/scanFmt API for read/write operation

- UART_stdioInit2() using Application specified UART parameters

...

Board_init(boardCfg);

...

UART_socGetInitCfg(UART_INSTANCE, &uart_cfg);

...

UART_socSetInitCfg(UART_INSTANCE, &uart_cfg);

...

UART_Params_init(¶ms);

...

UART_stdioInit2(UART_INSTANCE, ¶ms);

At this point UART driver is ready for data transfer on specific instance. Application can call UART_printf/scanFmt API for read/write operation

Read/Write APIs

Interrupt:

UART_read(handle,scanPrompt, sizeof(scanPrompt));/* Read API */

...

UART_write(handle, bufferPrompt, sizeof(bufferPrompt));/* Write API */

Or

UART_transactionInit(&transaction);

transaction.buf = (void *)scanPrompt;

transaction.count = sizeof(scanPrompt);

UART_read2(uart, &transaction);

...

UART_transactionInit(&transaction);

transaction.buf = (void *)bufferPrompt;

transaction.count = sizeof(bufferPrompt);

UART_write2(uart, &transaction);

Polling:

UART_readPolling(handle,scanPrompt, sizeof(scanPrompt));/* Read Polling mode API */

...

UART_writePolling(handle, bufferPrompt, sizeof(bufferPrompt));/* Write Polling API */

DMA Usage :

UART driver supports DMA operations to transfer data between

- Memory and RX FIFO for read transfer

- Memory and TX FIFO for write transfer.

DMA Driver is DMA family IP (EDMA and UDMA) and UART IP (V0 and V1) specific. Refer soc/dma/v#/UART_dma.c for these operations. Application need to create DMA handle and update the configuration before UART_init() API.

uartInitCfg[UART_INSTANCE].edmaHandle = UartApp_edmaInit();/* For AM/K1/K2 devices */

or

uartInitCfg[UART_INSTANCE].udmaHandle = UartApp_udmaInit();/* For K3 devices */

UART_init();

Refer “UART_BasicExample_[SOC]_[cpu]DMATestproject” or “UART_DMA_[evm]_[cpu]TestApp” for additional reference. Refer SDK Release Note for supported EVMs.

6.2.3. Application¶

6.2.3.1. Examples¶

| Name | Description | Expected Results | SoC Supported | Build Type |

|---|---|---|---|---|

| UART_Example application | Example demonstrating simple UART use case. Reference example for developers | Application prompts user to enter input data in console. User can enter up to 16 characters or terminate with enter key.Application echoes back characters. |

AM335x, AM437x, AM571x, AM572x, AM574x, k2g, k2hk,k2l,k2e,k2l c6657,c6678 omapl137, omapl138, | CCS project |

| UART_TestApplication | Unit Test application to test all APIs | User can enter up to 16 characters using serial console.Application echoes back | AM335x,AM437x,AM571x AM572x,AM574X k2g,k2hk,k2l,k2e,k2l c6657,c6678 omapl137,omapl138 | CCS project |

| am65xx | makefile | |||

| UART_DMATestApplicati on | Unit Test application with DMA mode. | User can enter up to 16 characters using serial console.Application echoes back | AM335x,AM437x,AM571x AM572x,AM574X k2g,k2hk,k2l,k2e,k2l c6657,c6678 omapl137,omapl138 | CCS project |

| am65xx | makefile |

6.2.4. Building UART examples¶

- Makefile based examples and dependent libraries can be built from the top level or module level UART makefile, refer to the Processor SDK RTOS Getting Started Guide for details of how to setup the build environment. Once you have setup the build environment, issue the following commands:

To build and clean libs/apps from top-level makefile:

cd <pdk>/packages

make uart

make uart_clean

To build and clean libs/apps from module-level makefile:

cd <pdk>/packages/ti/drv/uart

make all

make clean

- RTSC CCS project based examples are built from CCS

cd <pdk>/packages

./pdkProjectCreate.sh [soc] [board] [endian] uart [project type] [processor] [SECUREMODE=<yes/no>]

Import and build CCS Project from <pdk>/packages/MyExampleProjects/

6.2.5. Additional References¶

| Document | Location |

| API Reference Manual | $(TI_PDK_INSTALL_DIR)/packages/ti /drv/gpio/docs/doxygen/html/index .html |

| Release Notes | $(TI_PDK_INSTALL_DIR)/packages/ti /drv/gpio/docs/ReleaseNotes_UART _LLD.pdf |

6.3. USB¶

6.3.1. Overview¶

6.3.1.1. Driver Overview¶

PDK USB driver (USB LLD) provides the following USB class/functions while isolating application from the complexity of low level USB and USB class protocols:

- USB device Mass Storage Class

- USB host Mass Storage Class

- USB device Audio Class

- USB generic bulk device class

In rest of the page AM437x EVM is being refered as an example. Please check Release Notes for list of supported EVMs for driver.

Modes of Operation

- USB device Mass Storage Class

- USB device Mass Storage Class with RAM DISK

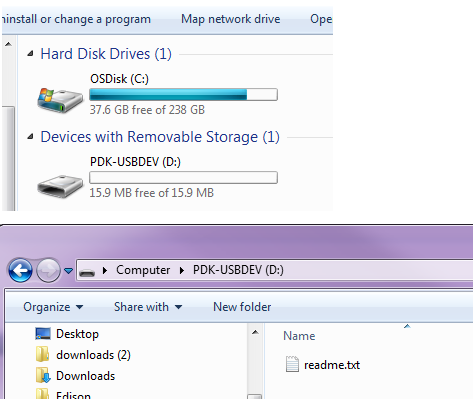

In this mode, a user-selected USB instance of the EVM will be working in device mode and will behave like a USB thumb drive. It uses part of the EVM DDR memory and exposes it as a physical storage for another USB host application. After the host PC enumerates this EVM-thumb drive, the PC will see a USB storage device. This EVM-thumb drive is not yet formatted with any file system and requires user to format it before use.

The following screen shots show what one would expect when running the device mode demo application and plugging in a USB cable from the EVM USB port #0 to a PC running Windows

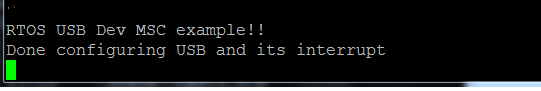

Printout from demo application:

The MSC device is detected in Windows, and a FAT formatted USB drive named “PDK-USBDEV” should be seen in the “Window Explorer”. The content of the drive is just a readme.txt file. This USB drive can be manipulated like any other removable USB drive.

Windows might show a message saying it should be scanned and fixed. We can just ignore it and just continue without scanning.

- USB device Mass Storage Class with MMCSD card

This example acts like a USB - MMCSD card reader. The example exposes the EVM’s MMCSD card to the Host PC via USB MSC. The Host PC can manipulate files on the attached MMCSD card on the EVM. This example is currently supported on AM335GP EVM. This is how it looks. Its code is similar to that of the USB device MSC example but with the call back functions calling MMCSD API’s instead of RamDisk APIs

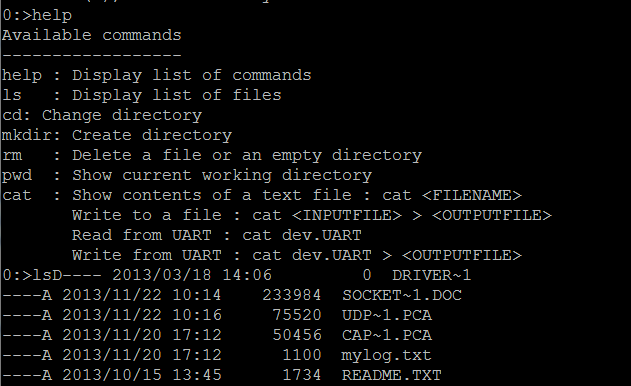

- USB host Mass Storage Class

In this mode, the USB instance will act as a USB host communicating with a USB device that supports Mass Storage Class function (USB thumb drive or a small USB hard drive). The demo example code utilizes a shell interface via the EVM via UART for interaction with the example. The shell provides some basic commands to manipulate the content of the attached USB disk drive.

Screenshot of a MSC host mode example running in RTOS after plugging in a USB thumb drive into USB port #1

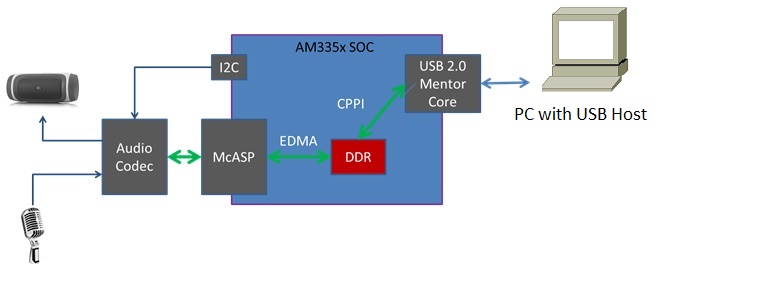

- USB device Audio Class

In this mode, USB instance of the EVM will be working in device mode and will behave like a USB headset with MIC. It uses audio codec on the EVM for running playback and record initiated by the USB host. McASP module will be used to transfer the data between USB device and audio codec on the board. EVM will appear as a new USB audio device on the host PC. Changing the default audio device on the host PC to EVM USB device will allow the playback and record operations between EVM and USB host. This mode of operation is currently supported on AM335X GP EVM, OMAP-L137 EVM and OMAP-L138 LCDK.

- USB generic bulk device class

In this mode, a user-selected USB instance of the EVM will be working in device mode. The mentioned USB device will show up in the host PC as a generic USB bulk device with one single interface containing a bulk IN and a bulk OUT endpoints. The configuration and interface descriptors published by the device contain vendor-specific class identifiers, so an application on the host will have to communicate with the device using either a custom driver or a subsystem such as WinUSB or libusb-win32 on Windows (or just libusb on Linux) to read and write to the device.

- Running USB bulk device demo application

The bulk demo application requires a host PC with USB host plugged to the USB device port on the EVM. Depending on the platform, the USB device port might be USB port #0 or #1.

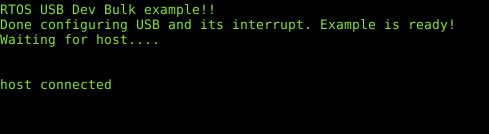

Please refer to PDK user guide for how to generate USB example projects. Once the demo application is loaded and run, the EVM UART console shows the following:

A Python host PC example application is provided in ti/drv/usb/example/usb_dev/bulk/usb_dev_bulk_host_application.py

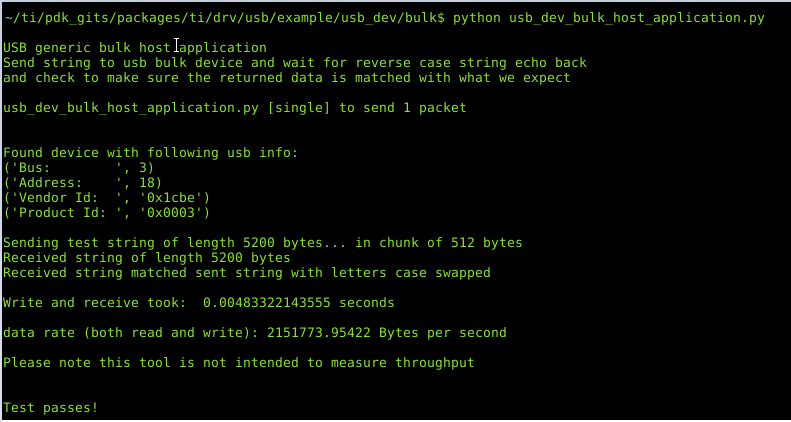

The example Python script requires PyUSB to run. On Linux host, proper UDEV rule is also required in order to access the USB bulk device as non-sudo user. The script itself also lists the requirements to run it as well as what command options available. The example UDEV rule is also placed in the same place where the Python script is located. It does the following:

- The Python script looks for the USB device with the example PID:VID,

- Sends an ASCII text string to the USB bulk demo application running on the EVM

- Expects the same text string with reversed case letter returned back, and also

- Verifies the received data with the data that it has sent and report the test result.

A screen shot of what the Python test script outputs

The USB bulk demo application configures the USB endpoints as high speed endpoints with 512B packet size.

6.3.2. User Interface¶

6.3.2.1. Driver Configuration¶

- Data Structures:

- tUSBDMSCDevice: Defined in usbdmsc.h. It is used in USB device mode application. This structure must be filled with the intended vendor and product ID as well as other product information and also the function pointers to functions that handle the disk functions (open/read/write/close, etc.). These product information will show up in the device and interface USB descriptors that are used during device enumeration. This device MSC class data is then assigned to the field usbClassData of the USB_Params bellow.

- USB params: USB_Params structure is declared in usb_drv.h. This structure must be provided to the USB driver. It must be initialized before the USB_open() function is called.

- USB APIs: main USB LLD and USB MSC API’s are declared in usb_drv.h and usbdmsc.h and usbhmsc.h provided in the root USB LLD directory.

- General USB LLD expectations:

The USB LLD will setup appropriate USB clock and power domains for the particular SOC being in used as part of its “device specific peripheral” functions.

After the USB_open() is called, the driver expects the application code to sets up USB interrupts with the interrupt handler being the USB LLD provided interrupt handler. Then the application have to call the USB LLD provided API USB_irqConfig() which enables USB module’s interrupts. In device mode, both USB core and USB misc interrupts are used in the USB device MSC application. In host mode, the USB host MSC only uses USB core interrupts.

After these steps, application code then can expect to have USB enumeration done and start USB transfer through the provided APIs.

6.3.2.2. API Call Flow¶

- USB Device MSC

The example application code uses the USB library, configures it as a USB device with MSC function. The example also provides functional codes that access a RAM disk (included from the Utils library in the included Starterware). The LLD calls these MSC back-ends functions to access the RAM disk. User can replace these functions with other functions that access other types of media or devices (MMCSD for example). The RAM disk image provided in the example demo application is not currently formatted. Thus the once enumerated, the PC will require the USB disc to be formatted before use.

Below diagram is the sequence of API calls that starts the USB device MSC application. All USB events are handled internally in the LLD and in the interrupt context.

User provided disk functions will be called from the LLD to handle the actual physical disk access. The overview of USB Device MSC example application:

The content of the file: usb_msc_structs.c can be replaced with customer USB device information (PID/VID, device names, etc.)

- USB Host MSC

The LLD also provides a USB host MSC example. The USB LLD is acting as a USB host, waiting for a USB thumb drive/memory stick to be plugged in. A console with a simple shell command is also provided so that the demo example can display and manipulate content of the USB device.

The following is how the USB host MSC example demo is organized:

The following is the sequence of the APIs that were used:

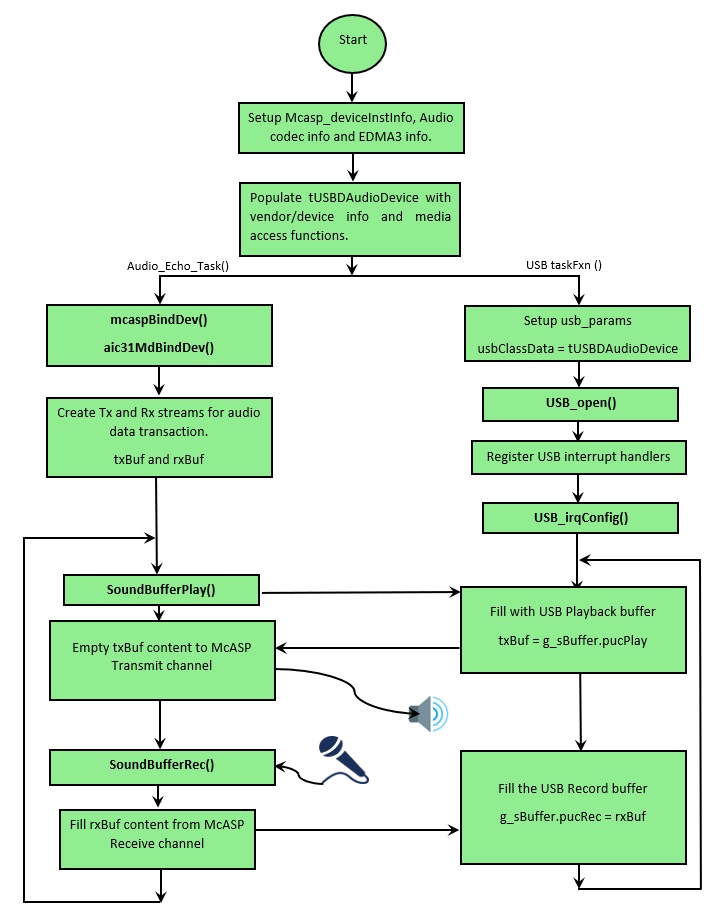

- USB Device Audio

The example application code uses the USB library, configures it as a USB device with Audio class function. USB LLD along with the application enumerates as the USB audio class device and allows accessing the audio ports on the EVM from USB host. It supports audio playback and record operations.

Below diagram is the sequence of API calls that starts the USB device audio application. All USB events are handled internally in the LLD and in the interrupt context.

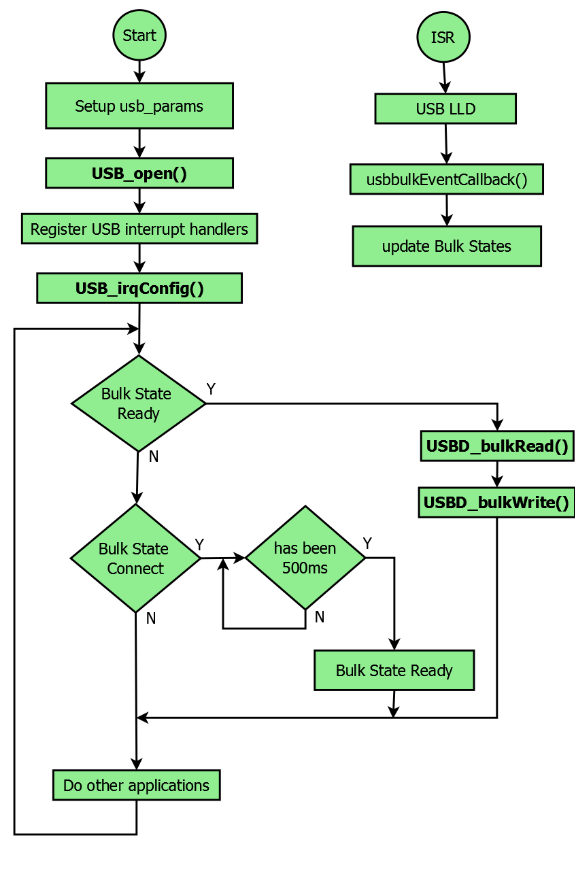

- USB Device Bulk

Sequence of API calls as long as what the example application looks like are described bellow

- Main APIs that are used to read/write from and to the USB bulk device are USBD_bulkRead() and USBD_bulkWrite().

These two functions will block the caller until they finish their operation.

- The main application should wait for about 500ms after the USB host sends the SetConfig request to make sure that the enumeration is completely finished before calling USBD_bulkRead/Write functions

6.3.3. Application¶

6.3.3.1. Examples¶

Examples are CCS projects. Generated with pdkProjectCreate scripts. Please refer Processor SDK RTOS Getting Started Guide for how to create and build examples projects

| Example Name | EVM’s supported | Notes |

|---|---|---|

| USB_DevMsc_mmcsd | AM335GP EVM, BeagleBoneBlack, AM572 EVM | eMMC is used on AM572 and BealgeBoneBlack examples This example can be used to format eMMC, just like any other USB storage device |

| USB_DevMsc | AM335GP, AM437xGP, OMAP137EVM, OMAPL138LCDK, AM57xIDK, AM572 EVM, K2G EVM, DRA7xx EVM, AM65x EVM/IDK | OMAPL13 LCDK host and device examples share the same USB port. |

| USB_HostMsc | AM335GP, AM437xGP, OMAP136EVM, OMAPL137LCDK, AM57xIDK, K2G EVM, DRA7xx EVM, AM65x EVM/IDK | OMAPL13 LCDK host and device examples share the same USB port. Need OTG cable for EVM with OTG port to work in host mode. USB3.0 host supported on AM572IDK. |

| USB_DevAudio | AM335xGP,OMAPL137 EVM,OMAPL138 LCDK | Refer to Hardware Setup and How to Run the Demo sections below |

| USB_DevBulk | AM335xGP, AM437xGP, AM572xIDK, AM571xIDK, AM574xIDK, K2GEVM, OMAPL137EVM, OMAP138LCDK, AM654x EVM/IDK |

6.3.3.2. Test Application¶

USB test applications are built using makefile. Some of the test application are RTOS/BIOS apps, other are bare metal apps. They are replica of the USB examples but built by makefile instead of CCS projects.

Refer to the Processor SDK RTOS Getting Started Guide for details of how to setup the build environment. Once you have setup the build environment, issue the following commands:

- cd <pdk>/packages/

- To build: make usb

- To clean: make usb_clean

- Test applications are then under (TI_PDK_INSTALL_DIR)/packages/ti/binary/

| Test App Name | EVM’s supported | Bare metal | Notes |

|---|---|---|---|

| USB_Baremetal_DevMsc_TestApp | AM65xx EVM/IDK | yes | Equivalent to DevMsc example |

| USB_Baremetal_HostMsc_TestApp | AM654x EVM/IDK | yes | Same function as HostMsc example |

| USB_HostMsc_TestApp | AM654x EVM/IDK | no | Same as HostMsc example |

| USB_DevMsc_TestApp | AM654x EVM/IDK | no | Same as DevMsc example |

| USB_DevBulk_TestApp | AM654x EVM/IDK | no | Same as DevBulk example |

| usb_d_msc_<platform> | AM335xGP,AM437xEVM OMAPL137 EVM OMAPL138 LCDK | yes | Same as USB DevMsc example. Build by going to example/usb_dev/msc/ build/<platform> |

| usb_h_msc_<platform> | AM335xGP,AM437xEVM OMAPL137 EVM OMAPL138 LCDK | yes | Same as USB HostMsc example Build by going to example/usb_dev/msc/ build/<platform> |

- Both examples and test applications can be loaded and run on their intended EVM via

- CCS JTAG connector, or

- Via SBL: the “app” file under CCS project’s debug directory (<PDK_INSTALL_PATH/MyExampleProjects/<ExampleProjectDirectory>/Debug>) is SBL loadable file of the built project.

– Project Memory layout must be considered and following SBL guideline so that examples can run safely via SBL. Please refer to SBL Component for more detail

6.3.4. Benchmark tool¶

6.3.4.1. USB host MSC¶

- To measure the USB host MSC throughput, a new command (bm) is added into the USB host mode example (or test application).

- This command is to run with a good known fast USB thumb drive attached to the USB host port.

- The throughput measurement result varies greatly depends on which USB device is plugged in and which filesystem is used

- The USB drive needs to be formated as FAT32 (since the USB host example only supports FAT filesystem) and has at least 100MB free space. Fast blank USB thumb drive is recomended.

- The command, when run, writes a 100MB file into the thumb drive and measures the time it takes to do so. It then reads back this 100MB file with time measurement to find the read throughput.

- The write and read are done in block size of 100KB, 256KB, 1MB, and 5MB. It prints throughput measurements for each of these blocks.

- This command is only supported in AM65xx at the moment.

- Syntax:

bm <test_file_name>

6.3.4.2. USB device MSC¶

- To measure USB device MSC throughtput a simple linux shell script usb_dev_msc_perf.sh is provided in PDK/packages/ti/drv/usb/example/usb_dev/msc/

- This script assumes the USB Dev MSC drive (PDK-USBDEV) is already mounted on the Linux host PC (under /media/$USER/PDK-USBDEV) when it runs

- It uses “dd” command to report the thoughput

- Tested on Ubuntu 16.04. Different version of Linux might mount the MSC drive at different place. Please adjust the script accordingly.

- The script writes a file to the PDK-USBDEV drive with a number of blocksize. By default it creates a 15MB test file by writing 150 blocks of 100K each (which would fit inside the 16MB RAM disk provided by the USB Dev MSC.)

- User is free to change the block size and number of blocks for the test. However it doens’t check if the end result file would fit the PDK-USBDEV drive or not.

- Syntax:

usb_dev_msc_perf.sh [<blocksize> <count>]

6.3.5. Hardware Setup¶

This section provides the specific HW setup required to run the USB examples.

- USB Device Audio

USB audio class demo requires additional setup for running playback and record operations. Below sections provide the setup details for each platform supported.

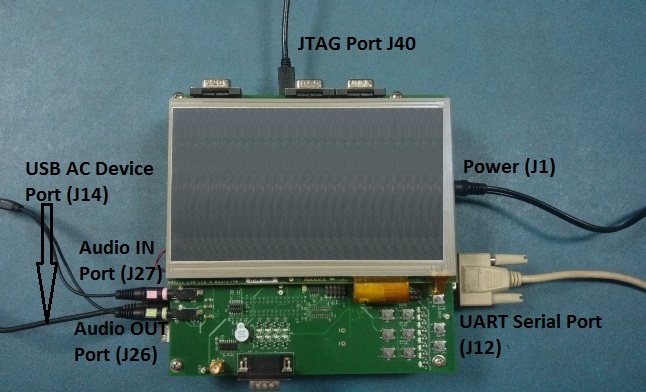

AM335x GP EVM

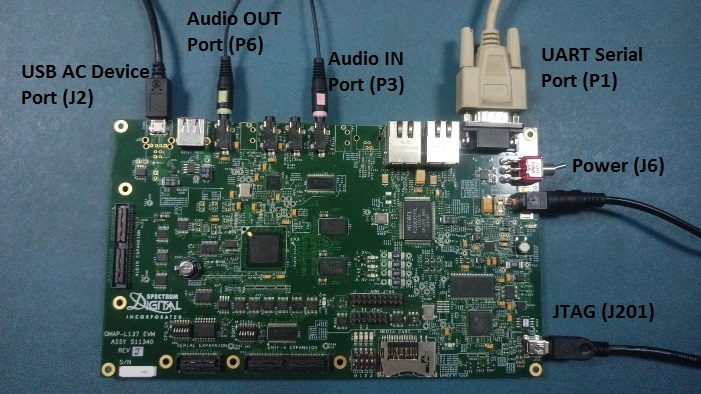

OMAPL137 EVM

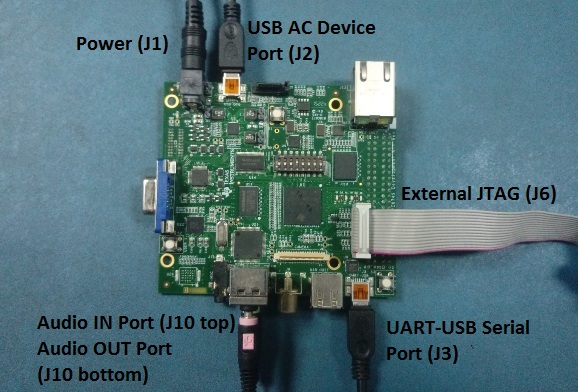

OMAPL138 LCDK

How to Run the Demo

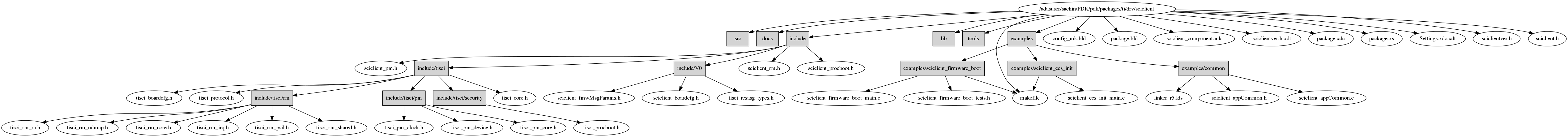

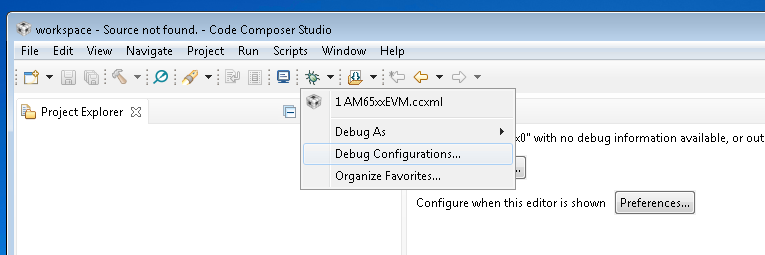

- Follow this link Processor SDK RTOS Setup CCS to get target configuration setup correctly.

- Use CCS to import the USB_DevAudio_<board>_<core>ExampleProject under pdk_<platform>_<version>/packages/MyExampleProjects.

- Build the imported project. the OUT file will be at pdk_<platform>_<version>/packages/MyExampleProjects/USB_DevAudio_<board>_<core>ExampleProject/Debug.

- Make the HW connections as shown in Hardware Setup section

- Launch the target configuration for the EVM from CCS 7.x.

- Connect to ARM or DSP core as applicable.

- Load the pdk_<platform>_<version>/packages/MyExampleProjects/USB_DevAudio_<board>_<core>ExampleProject/Debug/USB_DevAudio_<board>_armExampleProject.out.

- Run the program (loaded previously) by pressing F8

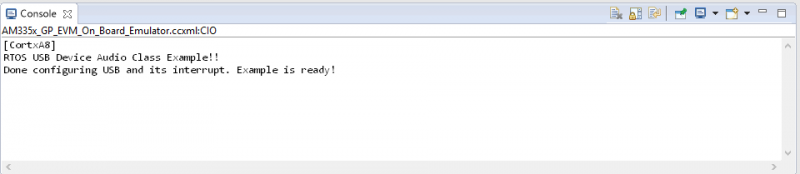

- The CCS ConsoleIO will display the following:

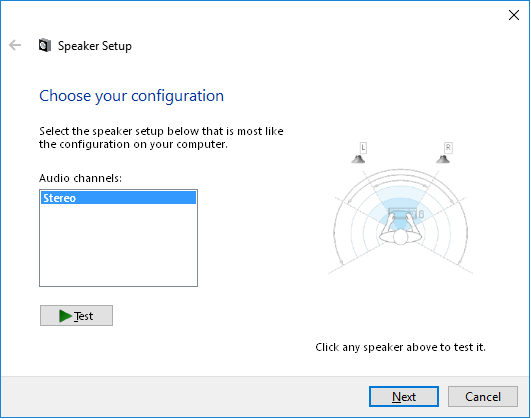

- Right click on the “Speaker Icon” on the USB Host (right side of the toolbar), then select “Playback devices”

- Wait until the “Speakers USB Audio Device” shows up in the “Sound” dialog

- Select the “Speakers USB Audio Device” in the “Sound” dialog, then click the “Configure”

- Click the “Test” in “Speaker Setup”, you should hear the testing tone in the headphone connected to the EVM

Note

‘board’ can be evmAM335x, evmOMAPL137 or lcdkOMAPL138

‘core’ can be arm or c674x

6.4. PCIe¶

6.4.1. Overview¶

PCIe module supports dual operation mode: End Point (EP or Type0) or Root Complex (RC or Type1). This driver focuses on EP mode but it also provides access to some basic RC configuration/functionality. For RC this is the lowest level; additional software is needed to perform generic enumeration of third party devices.

The PCIe subsystem has two address spaces. The first (Address Space 0) is dedicated for local application registers, local configuration accesses and remote configuration accesses. The second (Address Space 1) is dedicated for data transfer. This PCIe driver focuses on configuration of the interface and sending/receiving interrupts via Address Space 0. Data is transferred outside the scope of the LLD using CPU or EDMA through the data area.

There are three revisions of the pcie hardware. The first, v0, in KeyStone devices (C66x, K2x). The second, v1, is in AM57xx devices. The third, v2, is in AM65xx devices. The LLD abstacts the configuration of standards-based PCIe registers (Type 0, Type 1 and Capabilities registers) so same user code can be used on both device types. However, there are different interfaces for the registers not based on PCIe standards (port logic and ti-conf which generally covers interrupts and address translation). That portion of user code needs to differ between C66x/K2x, AM57xx, and AM65xx devices.

The example includes configuration of one SoC as EP and a second as RC. It then performs a simple CPU-based memory transfer (EDMA can be used via the same addresses used by the CPU), and interrupt generation (from EP) and reception (to RC). It also shows differences in user code required to support both C66x/K2x, AM57xx and AM65xx devices.

Differences in Operation between C66x/K2x and AM57xx devices

C66x/K2x, AM57xx, and AM65xx are functionally identical, except that interrupts are handled by example and lld only on AM57xx. Also older devices only support gen 1/2, while AM65xx supports gen 3.

Modes of Operation

The LLD is intended to bring up the PCIe peripheral, open memory mappings, and send/receive interrupts.

Root Complex (RC)

The PCIe peripheral can be used as a root complex. One or more other endpoints can be connected (more than one requires a PCIe switch on the board). The LLD configures the peripheral in RC mode. It doesn’t attempt to emulate the full enumeration capability of a Linux driver. Instead the user will need to supply code specific to each endpoint they intend to support.

Endpoint (EP)

The PCIe peripheral can be used as an endpoint. This is the more intended usecase for the LLD. Once the link is initialized, the LLD can provide data addresses and send interrupts to the RC.

Interrupts

The example for AM57XX provides code to send interrupts from an endpoint, and the LLD/example together contain code to receive/demux the interrupts (both MSI and Legacy) on an RC.

6.4.2. User Interface¶

6.4.2.1. Driver Configuration¶

Board-specific configuration

PCIe’s board specific configuration is in the example in PDK_INSTALL_DIR/packages/ti/drv/pcie/example/sample/am57x/src/pcie_sample_board.c. Calling sequence is in example and repeated below.

PCIe configuration structure

The pcie_soc.c binds the driver to the hardware on the board. It is passed into the driver via the call to Pcie_init().

6.4.2.2. API Call Flow¶

The API call flow is covered in pcie_sample.c.

The overall components are:

- Initialize the driver

- Initialize the SERDES and Power the peripheral (see example code for order for each device)

- Configure RC or EP symmetrically to talk to another similar device

- Perform data IO and interrupt.

6.4.3. Application¶

6.4.3.1. Examples¶

| Name | Description | EVM Configuration | Expected Results |

|---|---|---|---|

| PCIE_idkAM57[124]x*ExampleProject | 2-device PCIe connection | IMPORTANT: Cable must be MODIFIED in order to avoid damaging the clock drivers in the SoC! Connect two like AM57xx IDK EVMs J22 MODIFIED male-male crossover PCIe x1 or x4 cable and optional straight-through extender. For AM572x/AM574x we used a one-lane cross cable; for AM571x we used a 4-lane cross cable. | Projects available for C66, A15, and M4. |

AM572x/AM574x or AM571x EVM : One board is EP/other is RC; link is established and data/interrupts exchanged. All printed output goes to the serial console. |

PCIE_sample_ExampleProject (for AM65xx IDK) |

2-device PCIe connection | IMPORTANT: Cable must be MODIFIED in order to avoid damaging the clock drivers in the SoC! Connect two like AM65xx IDK EVMs PCIe using a MODIFIED male-male crossover PCIe x1 or x4 cable and optional straight-through extender. We used a one-lane cross cable. Executables for A53 (mpu) and R5 (mcu) available. Note: this is

NOT a CCS

project. It

is built from

running

|

AM65xx IDK One board is EP/ other is RC; link is established and data exchanged. All printed output goes to the serial console. |

| PCIE_evmK2G*ExampleProject | 2-device PCIe connection | IMPORTANT: Cable must be MODIFIED in order to avoid damaging the clock drivers in the SoC! Connect two K2G EVMs J5 using a MODIFIED male-male crossover PCIe x1 cable and optional straight-through extender. We used a one-lane cross cable. Ensure that jumper J15 is positioned to the left hand two pins as viewed with “J15” silkscreen right side up (pin 0 isn’t clearly marked). In the right hand position, the PCIe PLL will NOT get clock. Projects available for C66 and A15. |

K2G EVM : One board is EP/other is RC; link is established and data is exchanged. All printed output goes to serial console. |

| PCIE_idkAM571x_*armEdmaPktExampleProject (Available starting in Processor-SDK 3.1) | Packet Exchange over PCIe Benchmark | IMPORTANT: Cable must be MODIFIED in order to avoid damaging the clock drivers in the SoC! Connect two like >=REV1.3A AM571x IDK EVMs J22 using a MODIFIED male-male crossover PCIe x4 cable and optional straight-through extender. We used a 4-lane cross cable. Projects available for A15 only. >=REV1.3A EVM required (for x4 PCIe connectors). |

AM571X >=REV1.3A IDK : One board is EP/other is RC; link is established and data is exchanged. Produces same output as standard ExampleProject, except EP also prints packet exchange benchmark results. |

| Remaining PCIE_*ExampleProject | 2-device PCIe connection | Connect two like C66x/K2x (except K2G, see previous row) EVMs using an AMC breakout card. For K2L, it is necessary to configure the mux via the BMC console with “interface_muxs el pcie” command. Projects available for A15 and/or C66 as present in each device. | 6678, 6657, K2E, K2H, K2L : One board is EP/other is RC; link is established and data exchanged. For A15 projects, all printed output goes to serial console. For C66 projects, all printed output goes to CCS console. |

Quick setup of xds100 for two EVMs

- create new target configuration using XDS100v2 and AM572x (or AM571x) from the basic tab.

- Select Advanced tab.

- Highlight the XDS100v2, and click the “new” button and add second XDS100v2.

- Highlight the newly added XDS100v2, click the “add” button and select a second Am572x.

- open command prompt, and run ticcs_basecommonuscifxds100serial to get your serial numbers

- Highlight first XDS100v2, select “Debug Probe Selection” to “Select by Serial number” and enter one of the 2 serial numbers

- Repeat second XDS100v2, setting to to the second serial number.

General instructions for configuring multiple EVMs with any emulator type are available in Debugging with Multiple Debug Probes

Detailed instructions to run example

Ensure 2 Like EVMs are connected with a x1 PCIe male/male cross cable (for AM5XX) or a breakout card (for C667x, C665x, K2x)

Build project(s) appropriate for your EVM. Projects for A15 and C66 are provided based on core types available on each device.

Load via jtag either the ARM or DSP projects (but don’t mix and match) onto the first arm or dsp core of each the 2 EVMs. Same .out file supports both RC and EP. Use an “expressions” window to set PcieModeGbl to PCIE_RC_MODE on one EVM (it makes that EVM RC). Leave the second EVM alone (pcie_EP_MODE). Run the loaded cores. See table above to determine whether output is expected on serial console or CCS console.

Sample example output

Note that output will vary slightly based on device type. The following is from A57XX. The output from the RC and EP are interleaved since this is run from a 2*XDS1000 double config as described in Quick setup of xds100 for two EVMs

**********************************************

* PCIe Test Start *

* RC mode *

**********************************************

Version #: 0x02020003; string PCIE LLD Revision: 02.02.00.03:Dec 24 2015:17:38:37

PCIe Power Up.

PLL configured.

Successfully configured Inbound Translation!

Successfully configured Outbound Translation!

Starting link training...

**********************************************

* PCIe Test Start *

* EP mode *

**********************************************

Version #: 0x02020003; string PCIE LLD Revision: 02.02.00.03:Dec 24 2015:17:38:37

PCIe Power Up.

PLL configured.

Successfully configured Inbound Translation!

Successfully configured Outbound Translation!

Starting link training...

Link is up.

Link is up.

End Point received data.

End Point sent data to Root Complex, completing the loopback.

EP sending interrupts to RC

Root Complex received data.

RC waiting for 10 of each of 2 types of interrupts

RC got all 20 interrupts

Test passed.

End of Test.

6.4.4. Debug FAQ¶

If example fails to get link up

Confirm that male/male cross cable or breakout board is correctly connected.

If running from ARM cores, confirm that immediately after reset/reload that both devices have PcieModeGbl=PCIE_EP_MODE. If the PCIE_RC_MODE seems to survive reset/reload, it seems to mean watch window failed to refresh. Click the “Refresh” button for the watch window and it should flip back to EP, where you can reset it to RC. Simply running will cause both sides to run as EP, which leads to test failure.

Confirm that one side of the example has PcieModeGbl=PCIE_RC_MODE and the other is PCIE_EP_MODE.

Note

When changing to RC you must click somewhere outside the expression value to make the modification for RC to “take effect”. Simply pressing F8 after modifying the value will run without actually modifying the variable! The modification will be done when the ARM or DSP is stopped, so everything looks right, except that the log will show “PCIe test start EP mode” twice instead of “PCIe test start EP mode” once and “PCIe test start RC mode” once.

How to debug common PCIe issues

Please refer to PCI Express (PCIe) FAQ for Keystone devices.

6.4.5. Additional References¶

Additional documentation can be found in:

| Document | Location |

| Hardware Peripheral Users Guide |

|

| API Reference Manual | $(TI_PDK_INSTALL_DIR)/packages/ti /drv/pcie/docs/doxygen/html/index .html |

| Release Notes | $(TI_PDK_INSTALL_DIR)/packages/ti /drv/pcie/docs/ReleaseNotes_PCIE_LLD.pdf |

6.5. GPIO¶

6.5.1. Overview¶

6.5.1.1. Introduction¶

GPIO module allows application to manage General Purpose I/O instances and pins via simple portable APIs. Because of its simplicity, APIs are pin based and does not follow model of other drivers inside PDK which requires handle abstraction.

Modes of Operation

Following modes of operations are supported Input or Output Each gpio pin can be configured as either input: GPIO_CFG_INPUT or output: GPIO_CFG_OUTPUT. If it is configured as an output then pin level can be additionally configured

Interrupt support Each gpio pin can be configured to generate interrupts based on event type GPIO_CFG_IN_INT_XXX configuration. To generate interrupt, gpio pin has to be configured as input pin.

Driver Configuration

Board Specific Configuration

All board specific configurations like enabling clock and pin-mux are required before calling any driver APIs. By default Board_Init() API available under board module supports all initialization sequence for TI supported EVMs. In addition it initializes UART instance for Console/STDIO. Refer Processor SDK RTOS Board Support for additional details.

GPIO Configuration Structure

GPIO_soc.c binds driver with hardware attributes on the board. Hardware attributes includes base address, interrupt number etc. GPIO pin behavior can be configured statically, or alternatively dynamically during runtime.

GPIO_init () API triggers all static configuration information available through hardware attributes. Once initialization is complete additional APIs can be used to configure and access pins.

6.5.1.2. APIs¶

API reference for Application:

#include <ti/drv/gpio/GPIO.h>

Below sequence indicates API calling sequence for a simple use case of LED toggling

...

Board_init(boardCfg);

GPIO_init();

While(1)

{

GPIO_write(Board_LED1, GPIO_PIN_VAL_HIGH);

Delay();

GPIO_write(Board_LED1, GPIO_PIN_VAL_LOW);

Delay();

}

6.5.2. Application¶

6.5.2.1. Examples¶

Refer SDK Release Note for GPIO support across different EVMs.

| Name | Description | Expected Results

|

SoC Supported | Build Type |

|---|---|---|---|---|

| GPIO_LedBlink | Simple example demonstrating LED Toggling | Following LED

blinks based on EVM

being used.

AM335x

ICEv2:

USER LED 1

AM437x

EVM:

USER LED 1

AM572x IDK :

STATUS LED 1 Yellow

AM572x GP

EVM : USER LED1

AM574x IDK :

STATUS LED 1 Yellow

AM572x GP

EVM : USER LED1

AM571x IDK :

Industrial LED 3

Red

K2H EVM:

USER LED 2 Blue

K2E EVM:

USER LED 1 Blue

K2G EVM:

USER LED 1 Yellow

AM65xx EVM:

USER LD16, LD17

|

AM335x, AM437x, AM571x, AM572x, AM574x, k2g, k2hk, k2l, k2e, c6657, c6678, omapl137, | CCS project |

| am65xx | makefile |

Note

There are no user mode LEDs directly connected to GPIO pins on K2L, C6678 and C6657 EVMs.

6.5.3. Building GPIO examples¶

- Makefile based examples and dependent libraries can be built from the top level or module level GPIO makefile, refer to the Processor SDK RTOS Getting Started Guide for details of how to setup the build environment. Once you have setup the build environment, issue the following commands:

To build and clean libs/apps from top-level makefile:

cd <pdk>/packages

make gpio

make gpio_clean

To build and clean libs/apps from module-level makefile:

cd <pdk>/packages/ti/drv/gpio

make all

make clean

- RTSC CCS project based examples are built from CCS

cd <pdk>/packages

./pdkProjectCreate.sh [soc] [board] [endian] gpio [project type] [processor] [SECUREMODE=<yes/no>]

Import and build CCS Project from <pdk>/packages/MyExampleProjects/

6.5.4. Additional References¶

| Document | Location |

| API Reference Manual | $(TI_PDK_INSTALL_DIR)/packages/ti /drv/gpio/docs/doxygen/html/index .html |

| Release Notes | $(TI_PDK_INSTALL_DIR)/packages/ti /drv/gpio/docs/ReleaseNotes_GPIO _LLD.pdf |

6.6. I2C¶

6.6.1. Overview¶

6.6.1.1. Introduction¶

I2C module provides an interface to any I2C-bus-compatible device accessible via I2C serial bus. External components attached to I2C bus can serially transmit/receive data to/from the CPU through two-wire interface. Driver supports three types of transfers in both I2C master mode and slave mode

- Read

- Write

- Write followed by read

In addition driver supports following modes of operation:

- I2C_MODE_BLOCKING: By default, driver operates in blocking mode. In blocking mode, a Task’s code execution is blocked until transaction is complete. This ensures only one transaction operates at a given time. Driver supports both interrupt or non-interrupt based blocking modes.

- I2C_MODE_CALLBACK In callback mode, an I2C transaction functions asynchronously, which means that it does not block a Task’s code execution. After an I2C transaction is complete, I2C driver calls a user-provided hook function. Only interrupt based callback is supported.

Note

If I2C peripheral is in reset during a transfer, it can cause the I2C bus to hang. I2C V0 IP (Keystone SoCs) does not have hardware support to recover the I2C bus from hanging, user needs to power cycle the board as a workaround. For I2C V1 IP (AM3/4/5 SoCs), the application can call I2C_control() API and use I2C_CMD_RECOVER_BUS to recover the I2C bus.

Firmware

TI PRU-ICSS cores (Programmable Real-Time Unit Industrial Communication Subsystem) is firmware programmable and can take on various personalities. Processor SDK package includes I2C Firmware support. Refer I2C FW for additional details.

6.6.2. User Interface¶

6.6.2.1. Driver Configuration¶

Board Specific Configuration

All the board specific configurations eg:enabling and pin-mux of I2C pins should be performed before calling any driver APIs.By default Board_Init() API supports all initialization sequence for TI supported EVMs.Refer Processor SDK RTOS Board Support for additional details.

Once the board specific configuration is complete driver API I2C_init() can be called to initialize driver

I2C Configuration Structure

I2C_soc.c file binds driver with hardware attributes on the board through I2C_config structure. This structure must be provided to I2C driver. It must be initialized before the I2C_init() function is called and cannot be changed afterwards. For details about the individual fields of this structure, see the Doxygen help by opening PDK_INSTALL_DIR\packages\ti\drv\i2c\docs\doxygen\html\index.html.

6.6.2.2. APIs¶

API reference for application:

#include <ti/drv/i2c/I2C.h>

Sample code for initiating I2C transaction:

...

Board_init(boardCfg);

...

I2C_socGetInitCfg(peripheralNum, &i2c_cfg);

...

I2C_socSetInitCfg(peripheralNum, &i2c_cfg);

...

i2c = I2C_open(peripheralNum, &i2cParams);

...

...

/* Initiate I2C transfers. Refer Example for details

*/

I2C_transactionInit(&i2cTransaction);

transaction.masterMode = true;

...

...

transferOK = I2C_transfer(i2c, &i2cTransaction);

if (transferOK != I2C_STS_SUCCESS) {

/* I2C transaction failed */

}

6.6.3. Application¶

6.6.3.1. Examples¶

Refer Release Note for I2C support across different EVMs

Name

|

Description

|

Expected Results

|

SoC Supported | Build Type |

|---|---|---|---|---|

| I2C_EepromRead Example application | Simple example to

read fixed number

of bytes from

EEPROM on board and

compares it with

expected data.

|

Following prints will

come on console based

on pass/fail

criteria:

Pass criteria:

EEPROM data matched

All tests have

passed.

|

AM335x, AM437x, AM571x, AM572x, AM574x, k2g, k2hk,k2l,k2e,k2l c6657,c6678 omapl137, | CCS project |

| I2C_TestApplication | Driver Unit Test

application for

additional I2C

speed and other tests

|

Following prints will

come on console based

on pass/fail

criteria:

Pass criteria:

I2C Test: 100Kbps:

PASS

I2C Test: 400Kbps:

PASS

I2C Test: timeout

test passed

All tests have

passed.

|

AM335x, AM437x, AM571x, AM572x, AM574x, k2g, k2hk, k2l, k2e, c6657, c6678, omapl137, | CCS project |

| am65xx | makefile | |||

| I2C_TemperatureSensor | Example to get the

temperature value

from the temperature

sensor and displays

on the serial

console.

|

Following prints will

come on console based

on pass/fail

criteria:

Pass criteria:

Temperature =

“value in

centigrades” C

All tests have

passed.

|

AM572x, | CCS project |

| I2C_master/slave | Application

demonstrates

master/slave

transfer of I2C.

Application use

case requires two

EVMs. One acts as

Master and the

other as slave. I2C

connections

information and

addtional details

are as follows:

AM57xx boards I2C bus

connection on J9

(master board <–>

slave board)

pin22 (SCL)<–>

pin22 (SCL)

pin24 (SDA)<–> pin24

(SDA)

pin21 (GND)<–> pin21

(GND)

K2G boards I2C bus

connection on J12

(master board <–>

slave board)

pin28 (SCL)<–>

pin28 (SCL)

pin30 (SDA)<–>

pin30 (SDA)

pin50 (GND)<–>

pin50 (GND)

OMAPL138/C6748

boards I2C bus

connection on J15

(master board <–>

slave board)

pin13 (SCL)<–>

pin13 (SCL)

pin15 (SDA)<–>

pin15 (SDA)

pin35 (GND)<–>

pin35 (GND)

Run

“I2C_Slave_<BoardTy

pe>_<arm/c66x/m4>Test

Project”

first on Slave EVM

and then

“I2C_Master_<BoardT

ype>_<arm/c66x/m4>Tes

tProject”

on Master EVM.

|

Following prints will

come on console based

on pass/fail

criteria:

Pass criteria:

All tests have

passed.

|

AM572x, AM574x, k2g, omapl138, | CCS project |

Note

I2C_Test Application supports write test on Keystone II EVMs, by default write test is disabled, user can enable the write test by defining I2C_EEPROM_WRITE_ENABLE in test/eeprom_read/src/I2C_board.h. I2C_TemperatureSensor Application is supported only on AM572x GP EVM.

6.6.4. Building I2C examples¶

- Makefile based examples and dependent libraries can be built from the top level or module level I2C makefile, refer to the Processor SDK RTOS Getting Started Guide for details of how to setup the build environment. Once you have setup the build environment, issue the following commands:

To build and clean libs/apps from top-level makefile:

cd <pdk>/packages

make i2c

make i2c_clean

To build and clean libs/apps from module-level makefile:

cd <pdk>/packages/ti/drv/i2c

make all

make clean

- RTSC CCS project based examples are built from CCS

cd <pdk>/packages

./pdkProjectCreate.sh [soc] [board] [endian] i2c [project type] [processor] [SECUREMODE=<yes/no>]

Import and build CCS Project from <pdk>/packages/MyExampleProjects/

6.6.5. Additional References¶

| Document | Location |

| API Reference Manual | $(TI_PDK_INSTALL_DIR)\packages\ti \drv\i2c\docs\doxygen\html\index. html |

| Release Notes | $(TI_PDK_INSTALL_DIR)\packages\ti \drv\i2c\docs\ReleaseNotes_I2C_LL D.pdf |

6.7. McSPI-QSPI-OSPI¶

6.7.1. Introduction¶

SPI driver enables communication for general SPI, MCSPI (Multichannel SPI), QSPI (Quad SPI) and OSPI (Octal SPI) based peripherals on board through common API to application. MCSPI is a generic full-duplex interface supporting transmit and receive of data over SPI bus. QSPI/OSPI is a variant of SPI supports four receive data lanes. Driver supports configuration for either single, dual, quad or octal data lines

6.7.2. Modes of Operation¶

Following modes of operations are supported:

SPI_MODE_BLOCKING SPI_transfer() API blocks code execution until transaction has completed. By default, SPI driver operates in blocking mode. This ensures only one SPI transaction operates at a given time. This mode is supported in both interrupt or non-interrupt configurations.

SPI_MODE_CALLBACK SPI_transfer() API returns without waiting for completion of transaction in this case. Callback function registered by application is invoked once transaction is complete.This mode is supported only in interrupt configuration.

6.7.3. Driver Configuration¶

6.7.3.1. Board Specific Configuration¶

All board specific configurations eg:enabling clock and pin-mux for SPI pins are required before calling any driver APIs.By default Board_Init() API supports all initialization sequence for TI supported EVMs. In addition it initializes UART instance for Console/STDIO.Refer Processor SDK RTOS Board Support for additional details.Once board specific configuration is complete SPI_init() API should be called to initialize driver.

6.7.3.2. SoC Specific Configuration¶

All SoC specific configurations (eg: SPI module registers base address, interrupt configurations, etc.) can be set using SPI_socSetInitCfg() SoC driver API before calling any SPI driver APIs. The default SoC specific configurations can be retrieved using SPI_socGetInitCfg() SoC driver API.

6.7.3.3. SPI Configuration Structure¶

The SPI_soc.c file binds driver with hardware attributes on the board through SPI_config[] structure. This structure must be provided to the SPI driver. It must be initialized before the SPI_init() function is called and cannot be changed afterwards. For details about individual fields of this structure, see Doxygen help by opening PDK_INSTALL_DIRpackagestidrvspidocsdoxygenhtmlindex.html.

Driver requires common SPI_config[] to configure hardware attributes of MCSPI and QSPI/OSPI peripherals on SOC and board. First all MCSPI related hardware attributes is defined followed by QSPI/OSPI hardware attributes. Application will need to include appropriate offset to instance while invoking SPI_open() API..

6.7.4. APIs¶

API Reference for application:

#include <ti/drv/spi/SPI.h>

SPI IP V1 driver also supports multi-channel API’s:

#include <ti/drv/spi/MCSPI.h>

6.7.4.1. Open SPI¶

...

Board_init(boardCfg);

...

SPI_socGetInitCfg(peripheralNum, &spi_cfg);

...

SPI_socSetInitCfg(peripheralNum, &spi_cfg);

SPI_Params_init(&spiParams);

spiParams.transferMode = SPI_MODE_BLOCKING;

spiParams.transferCallbackFxn = NULL;

handle = SPI_open(peripheralNum, &spiParams);

SPI IP V1 driver also supports multi-channel open API’s:

...

Board_init(boardCfg);

...

MCSPI_Params_init(&spiParams);

spiParams.transferMode = SPI_MODE_BLOCKING;

spiParams.transferCallbackFxn = NULL;

handle = MCSPI_open(peripheralNum, channel, &spiParams);

At this point SPI driver is ready for data transfer in blocking mode on specific instance identified by handle. Pseudo/Sample code for SPI read/write transaction is included below. Refer example for additional details

...

spiTransaction.count = n; /* Transfer Length */

spiTransaction. txBuf = transmitBuffer; /* Buffer to be written */

spiTransaction.rxBuf = NULL; /* Buffer holding the received data */

transferOK = SPI_transfer(spi, &spiTransaction); /* Perform SPI transfer */

if (!transferOK) {

/* SPI transaction failed */

}

SPI IP V1 driver also supports multi-channel transfer API’s:

...

spiTransaction.count = n; /* Transfer Length */

spiTransaction. txBuf = transmitBuffer; /* Buffer to be written */

spiTransaction.rxBuf = NULL; /* Buffer holding the received data */

transferOK = MCSPI_transfer(spi, &spiTransaction); /* Perform SPI transfer */

if (!transferOK) {

/* SPI transaction failed */

}

Note

SPI_open API supports configuration of data word length in the SPI_Params. Currently IP V1 driver (for AM3/4/5 devices) supports 8/16/32-bit word length, IP V0 driver (for Keystone devices) supports 8/16-bit word length.

6.7.5. Examples¶

6.7.5.1. SPI¶

| Name | Description | Expected Results | SoC Supported | Build Type |

|---|---|---|---|---|

SPI_FlashReadWrite Example application |

Sample application demonstrating read and write of data to a NOR flash device connected over SPI interface. By default, write test is disabled, user can enable write test by defining TEST_SPI_NOR_WRITE in test/src/SPI_board.h If write test is enabled, write transaction is verified for correctness by reading contents back. |

Following prints on console expected: Pass criteria: All tests have passed. |

k2g, k2hk, k2l, k2e, c6657, c6678, omapl137, | CCS project |

| SPI_TestApplication | Driver unit test application to validate features and interfaces for SPI driver | Following prints on console expected: Pass criteria: All tests have passed. | am335x AM437x, AM571x, AM572x, AM574x, | CCS project |

| spiLoopback example | Example application to validate features and interfaces for SPI driver in loopback mode. Configures the SPI in loopback mode, transmits a test pattern and receives it back from SPI. Note: This example is intended to demonstrate the SPI LLD API usage on the HW platforms where SPI memory is not available. Currently this example is supported on OMAPL138/C6748 platforms. |

Following prints on console expected: Pass criteria: All tests have passed. | k2g, k2l, k2e, omapl138, AM335x, AM437x, AM571x, AM572x, AM574x, | CCS project |

6.7.5.2. QSPI¶

| Name | Description | Expected Results | SoC Supported | Build Type |

|---|---|---|---|---|

QSPI_FlashReadWrite Example application |

Sample application demonstrating read and write of data to a flash device connected over QSPI interface. Write transaction is verified for correctness by reading contents back. | Following prints on console expected: Pass criteria: All tests have passed. |

AM437x, AM571x, AM572x, AM574x, k2g, | CCS project |

| QSPI_TestApplication | Driver unit test application to validate features and interfaces for QSPI driver | Following prints on console expected: Pass criteria: All tests have passed. | AM437x, AM571x, AM572x, AM574x, k2g, | CCS project |

6.7.5.3. OSPI¶

| Name | Description | Expected Results | SoC Supported | Build Type |

|---|---|---|---|---|

| OSPI_TestApplication | Driver unit test application to validate features and interfaces for OSPI driver | Following prints on console expected: Pass criteria: All tests have passed. | am65xx | makefile |

6.7.5.4. MCSPI¶

| Name | Description | Additional EVM Configuration | Expected Results | SoC Supported | Build Type |

|---|---|---|---|---|---|

| MCSPI_Serialize r Example application | Sample Application demonstrating reading data generated from industrial input module. Application uses GPIO pins to assert load signal in order to generate date from industrial input module. | AM57x IDK EVM: Short pins 1 and 2 on header J37(Industrial I/O) AM335x ICE v2: Short pins 1 and 2 on header J14(Industrial I/O) AM437x IDK EVM: Short pins 1 and 2 on header J1(Industrial I/O) |

Following prints on console expected: Pass criteria: All tests have passed. |

AM335x, AM437x, AM571x, AM572x, AM574x, | CCS project |

| MCSPI_Dma_Seria lizer Example application | Sample Application demonstrating reading data generated from industrial input module through EDMA. Application uses GPIO pins to assert load signal in order to generate date from industrial input module. | AM57x IDK EVM: Short pins 1 and 2 on header J37(Industrial I/O) | AM437x IDK EVM: Short pins 1 and 2 on header J1(Industrial I/O) | Following prints on console expected: Pass criteria: All tests have passed. |

AM437x, AM571x, AM572x, AM574x, | CCS project |

| MCSPI_SerialFla sh | Sample Application demonstrating writing and reading data from the serial flash through MCSPI EDMA interface. | AM335x GP EVM: Set the EVM in profile 2 (SW8[1] = OFF,

|

Following prints on console expected: Pass criteria: All tests have passed. |

AM335x, | CCS project |

| MCSPI_slavemode example application | Application demonstrates slave recieve and transmit features of McSPI. Application use case requires two EVMs. One acts as Master and Another as slave. McSPI connections information and addtional details are as follows. No of Boards Required: 2 Connection requirements: Consider EVM1

as Master and

EVM2 as

slave.

MasterSPI_CLK

——-SlaveS

PI_CLK | MasterSPI_D0- ———SlaveS PI_D1 | MasterSPI_D1- ———Slave

MasterSPI_CS0

——–SlaveSP I_CS0 | DGND——— ————-DG ND Additional Requirements: Run “MCSPI_SlaveMod e_SlaveExample_ <BoardType><arm /c66x/m4>Exampl eProject” first on Slave EVM and then “MCSPI_SlaveMode _MasterExample <BoardType>_<ar m/c66x/m4>Examp leProject” on Master EVM. Note:

A DGND connection may be required from expansion connector on each board to make sure the data transfer is proper. |

Pin Connections: IDK AM571x,

IDK AM572x or IDK AM574x:

EVM1(master) ==== EVM2(slave)

J21-Pin24(CLK)—J21-Pin24(CLK)

J21-Pin26(MISO)—J21-Pin28(MISO)

J21-Pin28(MOSI)—J21-Pin26(MOSI)

J21-Pin30(CS)——J21-Pin30(CS)

J21-Pin22(DGND)–J21-Pin22(DGND)

IDK AM437x:

EVM1(master) ==== EVM2(slave)

J16-Pin24(CLK)—–J16-Pin24(CLK)

J16-Pin26(MISO)—J16-Pin28(MISO)

J16-Pin28(MOSI)—J16-Pin26(MOSI)

J16-Pin30(CS)——J16-Pin30(CS)

J16-Pin22(DGND)–J16-Pin22(DGND)

ICEv2AM335x:

EVM1(master) ========= EVM2(slave)

J3-Pin12(CLK)———J3-Pin12(CLK)

J3-Pin14(MIS0)——-J3-Pin16(MISO)

J3-Pin16(MOSI)——-J3-Pin14(MOSI)

J3-Pin18(CS)———–J3-Pin18(CS)

J3-Pin2(DGND)——–J3-Pin2(DGND)

BBB AM335x:

EVM1(master) ===== EVM2(slave)

P9-Pin31(CLK)——-P9-Pin31(CLK)

P9-Pin29(MISO)——P9-Pin30(MISO)

P9-Pin30(MOSI)——P9-Pin29(MOSI)

P9-Pin28(CS)———P9-Pin28(CS)

P9-Pin1(DGND)——-P9-Pin1(DGND)

K2G EVM:

EVM1(master) ======= EVM2(slave)

J12-Pin9(MISO)——-J12-Pin9(MISO)

J12-Pin11(MOSI)—-J12-Pin11(MOSI)

J12-Pin13(CLK)——J12-Pin13(CLK)

J12-Pin15(CS0)——J12-Pin15(CS0)

J12-Pin49(DGND)–J12-Pin49(DGND)

icev2AMIC110 EVM:

EVM1(master) ======= EVM2(slave)

J5-Pin12(MISO)——-J5-Pin14(MISO)

J5-Pin14(MOSI)——J5-Pin12(MOSI)

J4-Pin13(CLK)——J4-Pin13(CLK)

J5-Pin4(CS)———J5-Pin4(CS)

J5-Pin2(DGND)——-J5-Pin2(DGND)

|

**On Master

EVM console:

Master: PASS:

Txd from

slave SPI

Done

|

AM335x, AM437x, AM571x, AM572x, AM574x, k2g, | CCS project |

| am65xx | makefile |

6.7.6. Building SPI examples¶

- Makefile based examples and dependent libraries can be built from the top level or module level SPI makefile, refer to the Processor SDK RTOS Getting Started Guide for details of how to setup the build environment. Once you have setup the build environment, issue the following commands:

To build and clean libs/apps from top-level makefile:

cd <pdk>/packages

make spi

make spi_clean

To build and clean libs/apps from module-level makefile:

cd <pdk>/packages/ti/drv/spi

make all

make clean

- RTSC CCS project based examples are built from CCS

cd <pdk>/packages

./pdkProjectCreate.sh [soc] [board] [endian] spi [project type] [processor] [SECUREMODE=<yes/no>]

Import and build CCS Project from <pdk>/packages/MyExampleProjects/

6.7.7. Support for Benchmark Testing¶

| Name | Description | Expected Results | SOC/Core Suppported | Build Type |

|---|---|---|---|---|

| OSPI flash Test App | Test application used for performance benchmarking | Test application will print on the UART console: Board_flashWrite ### bytes at transfer rate #### Kbps Board_flashRead ### bytes at transfer rate #### Mbps Board_flashWrite CPU Load %## Board_flashRead CPU Load %## |

am65xx/A53 am65xx/R5 | make |

Note

- Data transfer between DDR and OSPI flash memory, performance measurement does not include time to invalidate/write back cache

- GTC counter (200MHz) used for throughput measurement on A53, and PMU cycle counter (400MHz) on R5

- sysbios load moduel used for load measurement

- Pipeline PHY enabled, DDR mode enabled in DAC mode

- Pipeline PHY disabled, DDR mode disabled in INDAC mode with ospi clock divider of 32

- Read/write transfer size of 1M bytes

- Write transfer size 1M bytes with DMA chunk size of 16 bytes in DAC DMA mode

6.7.8. Additional References¶

6.8. EDMA3¶

6.8.1. Overview¶

6.8.1.1. Introduction¶

EDMA3 Low Level Driver is targeted to device drivers and applications for submitting and synchronizing EDMA3-based DMA transfers.

EDMA3 is a peripheral that supports data transfers between two memory mapped devices. It supports EDMA as well as QDMA channels for data transfer.

The EDMA3 LLD consists of an EDMA3 Driver and EDMA3 Resource Manager. The EDMA3 Driver provides functionality that allows device drivers and applications for submitting and synchronizing with EDMA3 based DMA transfers. In order to simplify the usage, this component internally uses the services of the EDMA3 Resource Manager and provides one consistent interface for applications or device drivers.

6.8.2. User Interface¶

6.8.2.1. Driver Configuration¶

EDMA3 peripheral IP is re-used in different SoCs with only a few configuration changes:

- Number of DMA and QDMA channels supported

- Number of PARAM sets available

- Number of event queues and transfer controllers etc.

The EDMA3 peripheral is used by other peripherals for their DMA needs thus the EDMA3 Driver needs to cater to the requirements of device drivers of these peripherals as well as other application software that may need to use DMA services. Resources for EDMA driver is managed through RM sub module within driver.

6.8.2.2. APIs¶

API reference for EDMA3 driver

#include <ti/sdo/edma3/drv/edma3_drv.h>

API reference for EDMA3 Resource Management layer

#include <ti/sdo/edma3/rm/edma3_rm.h>

6.8.4. Additional References¶

| EDMA3 Driver Summary | |

|---|---|

| Component Type | Library |

| Install Package | EDMA3 Low level drivers |

| Install Directory | <root_install_dir>/edma3_lld_xx_xx_xx_xx |

| Project Type | N/A |

| Endian Support | Little and Big |

| Library Name | edma3_lld_drv.ae66 (little endian), edma3_lld_drv.ae66e (big endian), edma3_lld_drv.aa15fg (A15), edma3_lld_drv.aem4 (M4) |

| Linker Path | <ti/sdo/edma3/drv/lib/[cpu]> <ti/sdo/edma3/rm/lib/[soc-evm]> |

| Include Paths | <ti/sdo/edma3/drv> <ti/sdo/edma3/rm> |

| Reference Guides | See docs under install directory |

| Additional Resources | Programming the EDMA3 using the Low-Level Driver (LLD) |

| License | BSD |

EDMA3 sample libs

| EDMA3 Driver Sample Summary | |

|---|---|

| Component Type | Library |

| Install Package | EDMA3 Low level drivers |

| Install Directory | <root_install_dir>/edma3_lld_xx_xx_xx_xx |

| Project Type | N/A |

| Endian Support | Little and Big |

| Library Name | edma3_lld_drv_sample.ae66 (little endian), edma3_lld_drv_sample.ae66e (big endian), edma3_lld_drv_sample.aa15fg (A15), edma3_lld_drv_sample.aem4 (M4) edma3_lld_rm_sample.ae66 (little endian), edma3_lld_rm_sample.ae66e (big endian), edma3_lld_rm_sample.aa15fg (A15), edma3_lld_rm_sample.aem4 (M4) |

| Linker Path | <ti/sdo/edma3/drv/sample/lib/[soc-evm]/[cpu]> <ti/sdo/edma3/rm/sample/lib/[soc-evm]/[cpu]> |

| Include Paths | <ti/sdo/edma3/drv> <ti/sdo/edma3/rm> |

| Reference Guides | See docs under install directory |

| Additional Resources | Programming the EDMA3 using the Low-Level Driver (LLD) |

| License | BSD |

6.9. ICSS-EMAC¶

6.9.1. Introduction¶

The ICSS_EMAC (industrial communications subsystem Ethernet Media Access Controller) driver provide APIs to transmit and receive packets with a firmware based Ethernet switch that has been implemented on TI’s PRU-ICSS (Programmable Real-Time Unit Subsystem and Industrial Communication SubSystem) 32-bit RISC cores.

Software Architecture

The ICSS EMAC low level driver can be partitioned into the following:

- Driver software running on the host processor, provides a well defined set of APIs to configure the driver, send packets to the firmware and receive packet from the firmware.

- Firmware which implements a 2 port ethernet switch supporting 802.1d @100 Mbps. This runs on the TI-PRU-ICSS cores.

Driver Features

ICSS_EMAC LLD implements following:

- Rx - Copying packet received from firmware and providing it to TCP/IP stack

- Tx - Providing packet from TCP/IP stack to firmware

- Learning/Forwarding Data Base

- Storm Prevention implementation

- Host Statistics implementation

- TCP/IP stack related initialization

- Configuring IP address

- ARM interrupt management

- For details of the driver, please refer to

- [1]

6.9.2. User Interface¶

6.9.2.1. Driver Configuration¶

6.9.2.2. APIs¶

API reference for application:

#include <ti/drv/icss_emac/icss_emacDrv.h>

API Call Flow

The below sequence indicates the calling sequence of ICSS_EMAC driver APIs for a use case of an EMAC example which implements single Ethernet MAC using PRU-ICSS Instance 2, ETH0. For additional details refer example inside package

...

Board_init(cfg);

/* Perform MDIO init */

ICSS_EMAC_testMdioInit(CSL_MPU_PRUSS2_U_MII_MDIO_REGS);

/* Create handle for PRUICSS instance*/

ICSS_EMAC_testPruIcssHandle2= PRUICSS_create(pruss_config,2);

/* Setup crossbar configuration to receive PRU-ICSS interrupts and map them to A15 (illustration for PRU2ETH0) */

CSL_xbarDspIrqConfigure(..); /* Link ISR */

CSL_xbarDspIrqConfigure(..); /* RX PKT ISR */

CSL_xbarDspIrqConfigure(..); /* TX PKT ISR */

/*Initialize driver */

...

ICSS_EmacInit(..);

/* Register callbacks for RX/TX, Link Interrupts, these are called in context of ISR */

ICSS_EmacRegisterPort0ISRCallback(..);

ICSS_EmacRegisterHwIntRx(..);

ICSS_EmacRegisterHwIntTx(..);

/* Enable interrupts for RX/TX/Link*/

ICSS_EMAC_testInterruptInit(ICSS_EMAC_testHandle2);

/* Enable Link Interrupt in MDIO sub-system */

ICSS_EMAC_testMdioEnableLinkInterrupt(..);

/* At this point, ICSS_EMAC LLD APIs can be called */

</syntaxhighlight>

Firmware

TI PRU-ICSS cores (Programmable Real-Time Unit Industrial Communication Subsystem) is firmware programmable and can take on various personalities. Examples include an SORTE, ethernet Switch, Industrial protocol switch. Please refer to ICSS-EMAC Firmwares for further explanation.

6.9.3. Application¶

6.9.3.1. Examples¶

Refer “ICSS_EMAC_<Basic/Switch>Example_<SOC>_<CPU>Testproject” for additional reference. Refer Release Note for ICSS_EMAC supported on different EVMs.

Name

|

Description

|

EVM

Configuration

|

Expected

Results

|

|---|---|---|---|

| ICSS_EMAC_Basic Example | EMAC Loopback test at PRU-ICSS EMAC PHY. Example

demonstrates

loopback

capability by

sending dummy

broadcast

packet to

PRU-ICSS

instance 2,

ethernet port

0 (PRU ETH0).

Unit test

registers

receive

packet

callback

routine with

LLD to be

called for RX

packet. Call

back routine

will extract

packet

received,

perform

simple memory

comparison

against

packet sent

for integrity

check. Unit

test will

iterate 10

times for

packet

transmission

and reception

check.

|

10/100 Mb/s loopback cable | Unit Test will print ^All tests have passed^ via UART console. |

| ICSS_EMAC_Switc hExample | Switch Loopback test at PRU-ICSS EMAC PHY. Example

demonstrates

switch

learning

loopback

capability by

sending dummy

broadcast

packet to

PRU-ICSS

instance,

ethernet

port. Unit

test

registers

receive

packet

callback

routine with

LLD to be

called for RX

packet. Call

back routine

will extract

packet

received,

perform

simple memory

comparison

against

packet sent

for integrity

check. As

with switch

for every 1

transmitted

packet,

firmware will

respond back

with 2

recieved

packets. Unit

test will

iterate 10

times for

packet

transmission

and reception

check.

|

100 Mb/s loopback cable | Unit Test will print ^All tests have passed^ via UART console. |

6.9.4. Debug Guide¶

For debugging ICSS EMAC examples or LLD. Please refer to ICSS-EMAC Debug Guide.

6.10. PRUSS¶

6.10.1. Overview¶

6.10.1.1. Introduction¶

Firmware

The PRUSS (Programmable Real-Time Unit Subsystem) is firmware programmable and can take on various personalities. Examples include an ethernet MAC, ethernet Switch, Industrial protocol switch. For a good example, please refer to Simple Open Real Time Ethernet Protocol (SORTE)

Driver Features

- PRU control features i.e enable/disable/reset a PRU

- Helper functions i.e. load and execute firmware in PRU

- Memory mapping of PRU/L3/External memories

- PRU and Host event management (i.e. map sys_evt/channel/hosts in PRU INTC generate interrupts, wait for occurrence of an event, and acknowledge interrupts

- Interrupt management for A15/C66x CPU targets

6.10.2. User Interface¶

6.10.2.1. Driver Configuration¶

Board Specific Configuration

All the board specific configurations like enabling the clock and pin-mux of UART/GPIO/PRUSS ICSS pins should be performed before calling any of the driver APIs.

PRUSS Configuration Structure

The pruicss_device.c file contains the declaration of the PRUICSS config structure. This structure must be provided to the driver at the time when PRUICSS_create() API is called to creat the PRUICSS_Handle. This handle is subsequently required to make any PRUSS LLD API call.

6.10.2.2. APIs¶

Reference API header file:

#include <ti/drv/pruss/pruicss.h>

API Call Flow

Below sequence indicates calling sequence of PRUSS driver APIs for a use case of sending INTC event to the PRU. Refer example code within module for additional details

...

/* Initialize Board */

Board_init(boardCfg);

/* Creates handle for PRUICSS instance */

handle = PRUICSS_create(pruss_config,instance);

/* Disable PRUICSS instance */

PRUICSS_pruDisable(handle,instance );

/* Register an Interrupt Handler for an event */

PRUICSS_registerIrqHandler(handle,pruEvtoutNum,intrNum,eventNum,waitEnable,irqHandler);

/* Sets the buffer pointer for PRU */

PRUICSS_setPRUBuffer(..);

/* API to do Interrupt-Channel-host mapping */

PRUICSS_pruIntcInit(handle,&pruss_intc_initdata);

/* Execute program on PRU */

PRUICSS_pruExecProgram(handle,0);

/* Enable PRU */

PRUICSS_pruEnable(handle,0);

/* Generates INTC event */

PRUICSS_pruSendEvent(handle,ARM_PRU0_EVENT);

6.10.3. Application¶

6.10.3.1. Examples¶

| Name | Description

|

Expected Results

|

|---|---|---|

| PRUSS_TestApplication | Test application is

designed to ping

pong an event

between CPU

target(A15/C66x)

and PRU for a fixed

count.Application

is to test PRU’s

load, control and

Interrupt

controller

functionalities.

|

Following prints

expected on console

based on pass/fail

criteria:

Pass criteria:

Prints related to

sending and

receiving event from

PRU will be printed

on console. Test

program at the end

expected to output:

“All tests have

passed”

|

6.10.4. Additional References¶

| Document | Location |

| API Reference Manual | $(TI_PDK_INSTALL_DIR)\packages\ti \drv\pruss\docs\doxygen\html\inde x.html |

| Release Notes | $(TI_PDK_INSTALL_DIR)\packages\ti \drv\pruss\docs\ReleaseNotes_PRUS S_LLD.pdf |

6.11. FATFS¶

6.11.1. Overview¶

6.11.1.1. Introduction¶

FATFS module provides an interface to configure a driver for FAT file system compatible device that connects via MMCSD, USB, etc. It configures FATFS for disk operations driver disk Initialize, disk read, disk write

6.11.2. Driver Overview¶

PDK FATFS driver provides support for both single and multiple partition on a given SD/MMC card. The driver uses a volume to partition mapping technique to handle multiple storage device with multiple partition. The driver supports file operations such as open, read and wirte on to the SD/MMC card. The FATFS driver access the SD/MMC card through the PDK MMCSD driver which needs to be configured from the application as part of the FATFS_config structure. The FATFS driver is used in other PDK module application such as MMCSD, USB and SBL.

FATFS file operation API’s can be accessed from the application only after FATFS_open function is invoked.

FATFS_init();

FATFS_open(0U, NULL, &fatfsHandle);

6.11.3. User Interface¶

6.11.3.1. Driver Configuration¶

Board Specific Configuration