|

|

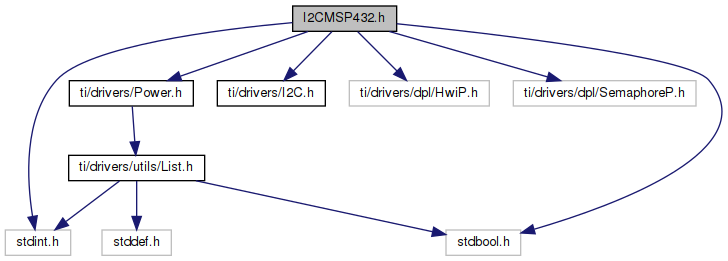

I2C driver implementation for the EUSCI controller on MSP432.

This I2C driver implementation is designed to operate on a EUCSI controller in I2C mode. The I2CMSP432 header file should be included in an application as follows:

Refer to I2C.h for a complete description of APIs & example of use.

#include <stdint.h>#include <stdbool.h>#include <ti/drivers/I2C.h>#include <ti/drivers/dpl/HwiP.h>#include <ti/drivers/dpl/SemaphoreP.h>#include <ti/drivers/Power.h>

Go to the source code of this file.

Data Structures | |

| struct | I2CMSP432_HWAttrsV1 |

| I2CMSP432 Hardware attributes. More... | |

Macros | |

| #define | I2CMSP432_P1_6_UCB0SDA 0x00000116 |

| #define | I2CMSP432_P1_7_UCB0SCL 0x00000117 |

| #define | I2CMSP432_P2_0_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x20) |

| #define | I2CMSP432_P2_0_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x20) |

| #define | I2CMSP432_P2_0_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x20) |

| #define | I2CMSP432_P2_0_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x20) |

| #define | I2CMSP432_P2_1_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x21) |

| #define | I2CMSP432_P2_1_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x21) |

| #define | I2CMSP432_P2_1_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x21) |

| #define | I2CMSP432_P2_1_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x21) |

| #define | I2CMSP432_P2_2_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x22) |

| #define | I2CMSP432_P2_2_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x22) |

| #define | I2CMSP432_P2_2_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x22) |

| #define | I2CMSP432_P2_2_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x22) |

| #define | I2CMSP432_P2_3_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x23) |

| #define | I2CMSP432_P2_3_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x23) |

| #define | I2CMSP432_P2_3_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x23) |

| #define | I2CMSP432_P2_3_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x23) |

| #define | I2CMSP432_P2_4_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x24) |

| #define | I2CMSP432_P2_4_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x24) |

| #define | I2CMSP432_P2_4_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x24) |

| #define | I2CMSP432_P2_4_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x24) |

| #define | I2CMSP432_P2_5_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x25) |

| #define | I2CMSP432_P2_5_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x25) |

| #define | I2CMSP432_P2_5_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x25) |

| #define | I2CMSP432_P2_5_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x25) |

| #define | I2CMSP432_P2_6_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x26) |

| #define | I2CMSP432_P2_6_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x26) |

| #define | I2CMSP432_P2_6_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x26) |

| #define | I2CMSP432_P2_6_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x26) |

| #define | I2CMSP432_P2_7_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x27) |

| #define | I2CMSP432_P2_7_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x27) |

| #define | I2CMSP432_P2_7_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x27) |

| #define | I2CMSP432_P2_7_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x27) |

| #define | I2CMSP432_P3_0_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x30) |

| #define | I2CMSP432_P3_0_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x30) |

| #define | I2CMSP432_P3_0_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x30) |

| #define | I2CMSP432_P3_0_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x30) |

| #define | I2CMSP432_P3_1_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x31) |

| #define | I2CMSP432_P3_1_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x31) |

| #define | I2CMSP432_P3_1_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x31) |

| #define | I2CMSP432_P3_1_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x31) |

| #define | I2CMSP432_P3_2_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x32) |

| #define | I2CMSP432_P3_2_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x32) |

| #define | I2CMSP432_P3_2_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x32) |

| #define | I2CMSP432_P3_2_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x32) |

| #define | I2CMSP432_P3_3_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x33) |

| #define | I2CMSP432_P3_3_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x33) |

| #define | I2CMSP432_P3_3_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x33) |

| #define | I2CMSP432_P3_3_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x33) |

| #define | I2CMSP432_P3_4_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x34) |

| #define | I2CMSP432_P3_4_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x34) |

| #define | I2CMSP432_P3_4_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x34) |

| #define | I2CMSP432_P3_4_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x34) |

| #define | I2CMSP432_P3_5_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x35) |

| #define | I2CMSP432_P3_5_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x35) |

| #define | I2CMSP432_P3_5_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x35) |

| #define | I2CMSP432_P3_5_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x35) |

| #define | I2CMSP432_P3_6_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x36) |

| #define | I2CMSP432_P3_6_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x36) |

| #define | I2CMSP432_P3_6_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x36) |

| #define | I2CMSP432_P3_6_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x36) |

| #define | I2CMSP432_P3_7_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x37) |

| #define | I2CMSP432_P3_7_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x37) |

| #define | I2CMSP432_P3_7_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x37) |

| #define | I2CMSP432_P3_7_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x37) |

| #define | I2CMSP432_P6_4_UCB1SDA 0x00000164 |

| #define | I2CMSP432_P6_5_UCB1SCL 0x00000165 |

| #define | I2CMSP432_P6_6_UCB3SDA 0x00000266 |

| #define | I2CMSP432_P6_7_UCB3SCL 0x00000267 |

| #define | I2CMSP432_P7_0_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x70) |

| #define | I2CMSP432_P7_0_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x70) |

| #define | I2CMSP432_P7_0_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x70) |

| #define | I2CMSP432_P7_0_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x70) |

| #define | I2CMSP432_P7_1_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x71) |

| #define | I2CMSP432_P7_1_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x71) |

| #define | I2CMSP432_P7_1_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x71) |

| #define | I2CMSP432_P7_1_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x71) |

| #define | I2CMSP432_P7_2_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x72) |

| #define | I2CMSP432_P7_2_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x72) |

| #define | I2CMSP432_P7_2_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x72) |

| #define | I2CMSP432_P7_2_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x72) |

| #define | I2CMSP432_P7_3_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x73) |

| #define | I2CMSP432_P7_3_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x73) |

| #define | I2CMSP432_P7_3_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x73) |

| #define | I2CMSP432_P7_3_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x73) |

| #define | I2CMSP432_P7_4_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x74) |

| #define | I2CMSP432_P7_4_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x74) |

| #define | I2CMSP432_P7_4_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x74) |

| #define | I2CMSP432_P7_4_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x74) |

| #define | I2CMSP432_P7_5_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x75) |

| #define | I2CMSP432_P7_5_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x75) |

| #define | I2CMSP432_P7_5_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x75) |

| #define | I2CMSP432_P7_5_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x75) |

| #define | I2CMSP432_P7_6_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x76) |

| #define | I2CMSP432_P7_6_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x76) |

| #define | I2CMSP432_P7_6_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x76) |

| #define | I2CMSP432_P7_6_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x76) |

| #define | I2CMSP432_P7_7_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x77) |

| #define | I2CMSP432_P7_7_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x77) |

| #define | I2CMSP432_P7_7_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x77) |

| #define | I2CMSP432_P7_7_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x77) |

| #define | I2CMSP432_P10_2_UCB3SDA 0x000001A2 |

| #define | I2CMSP432_P10_3_UCB3SCL 0x000001A3 |

Variables | |

| const I2C_FxnTable | I2CMSP432_fxnTable |

| #define I2CMSP432_P1_6_UCB0SDA 0x00000116 |

Port 1 Pin 6 is EUSCI B0 SDA

| #define I2CMSP432_P1_7_UCB0SCL 0x00000117 |

Port 1 Pin 7 is EUSCI B0 SCL

| #define I2CMSP432_P2_0_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x20) |

Port 2 Pin 0 is EUSCI B0 SDA

| #define I2CMSP432_P2_0_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x20) |

Port 2 Pin 0 is EUSCI B0 SCL

| #define I2CMSP432_P2_0_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x20) |

Port 2 Pin 0 is EUSCI B2 SDA

| #define I2CMSP432_P2_0_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x20) |

Port 2 Pin 0 is EUSCI B2 SCL

| #define I2CMSP432_P2_1_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x21) |

Port 2 Pin 1 is EUSCI B0 SDA

| #define I2CMSP432_P2_1_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x21) |

Port 2 Pin 1 is EUSCI B0 SCL

| #define I2CMSP432_P2_1_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x21) |

Port 2 Pin 1 is EUSCI B2 SDA

| #define I2CMSP432_P2_1_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x21) |

Port 2 Pin 1 is EUSCI B2 SCL

| #define I2CMSP432_P2_2_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x22) |

Port 2 Pin 2 is EUSCI B0 SDA

| #define I2CMSP432_P2_2_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x22) |

Port 2 Pin 2 is EUSCI B0 SCL

| #define I2CMSP432_P2_2_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x22) |

Port 2 Pin 2 is EUSCI B2 SDA

| #define I2CMSP432_P2_2_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x22) |

Port 2 Pin 2 is EUSCI B2 SCL

| #define I2CMSP432_P2_3_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x23) |

Port 2 Pin 3 is EUSCI B0 SDA

| #define I2CMSP432_P2_3_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x23) |

Port 2 Pin 3 is EUSCI B0 SCL

| #define I2CMSP432_P2_3_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x23) |

Port 2 Pin 3 is EUSCI B2 SDA

| #define I2CMSP432_P2_3_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x23) |

Port 2 Pin 3 is EUSCI B2 SCL

| #define I2CMSP432_P2_4_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x24) |

Port 2 Pin 4 is EUSCI B0 SDA

| #define I2CMSP432_P2_4_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x24) |

Port 2 Pin 4 is EUSCI B0 SCL

| #define I2CMSP432_P2_4_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x24) |

Port 2 Pin 4 is EUSCI B2 SDA

| #define I2CMSP432_P2_4_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x24) |

Port 2 Pin 4 is EUSCI B2 SCL

| #define I2CMSP432_P2_5_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x25) |

Port 2 Pin 5 is EUSCI B0 SDA

| #define I2CMSP432_P2_5_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x25) |

Port 2 Pin 5 is EUSCI B0 SCL

| #define I2CMSP432_P2_5_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x25) |

Port 2 Pin 5 is EUSCI B2 SDA

| #define I2CMSP432_P2_5_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x25) |

Port 2 Pin 5 is EUSCI B2 SCL

| #define I2CMSP432_P2_6_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x26) |

Port 2 Pin 6 is EUSCI B0 SDA

| #define I2CMSP432_P2_6_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x26) |

Port 2 Pin 6 is EUSCI B0 SCL

| #define I2CMSP432_P2_6_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x26) |

Port 2 Pin 6 is EUSCI B2 SDA

| #define I2CMSP432_P2_6_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x26) |

Port 2 Pin 6 is EUSCI B2 SCL

| #define I2CMSP432_P2_7_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x27) |

Port 2 Pin 7 is EUSCI B0 SDA

| #define I2CMSP432_P2_7_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x27) |

Port 2 Pin 7 is EUSCI B0 SCL

| #define I2CMSP432_P2_7_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x27) |

Port 2 Pin 7 is EUSCI B2 SDA

| #define I2CMSP432_P2_7_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x27) |

Port 2 Pin 7 is EUSCI B2 SCL

| #define I2CMSP432_P3_0_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x30) |

Port 3 Pin 0 is EUSCI B0 SDA

| #define I2CMSP432_P3_0_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x30) |

Port 3 Pin 0 is EUSCI B0 SCL

| #define I2CMSP432_P3_0_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x30) |

Port 3 Pin 0 is EUSCI B2 SDA

| #define I2CMSP432_P3_0_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x30) |

Port 3 Pin 0 is EUSCI B2 SCL

| #define I2CMSP432_P3_1_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x31) |

Port 3 Pin 1 is EUSCI B0 SDA

| #define I2CMSP432_P3_1_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x31) |

Port 3 Pin 1 is EUSCI B0 SCL

| #define I2CMSP432_P3_1_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x31) |

Port 3 Pin 1 is EUSCI B2 SDA

| #define I2CMSP432_P3_1_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x31) |

Port 3 Pin 1 is EUSCI B2 SCL

| #define I2CMSP432_P3_2_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x32) |

Port 3 Pin 2 is EUSCI B0 SDA

| #define I2CMSP432_P3_2_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x32) |

Port 3 Pin 2 is EUSCI B0 SCL

| #define I2CMSP432_P3_2_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x32) |

Port 3 Pin 2 is EUSCI B2 SDA

| #define I2CMSP432_P3_2_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x32) |

Port 3 Pin 2 is EUSCI B2 SCL

| #define I2CMSP432_P3_3_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x33) |

Port 3 Pin 3 is EUSCI B0 SDA

| #define I2CMSP432_P3_3_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x33) |

Port 3 Pin 3 is EUSCI B0 SCL

| #define I2CMSP432_P3_3_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x33) |

Port 3 Pin 3 is EUSCI B2 SDA

| #define I2CMSP432_P3_3_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x33) |

Port 3 Pin 3 is EUSCI B2 SCL

| #define I2CMSP432_P3_4_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x34) |

Port 3 Pin 4 is EUSCI B0 SDA

| #define I2CMSP432_P3_4_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x34) |

Port 3 Pin 4 is EUSCI B0 SCL

| #define I2CMSP432_P3_4_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x34) |

Port 3 Pin 4 is EUSCI B2 SDA

| #define I2CMSP432_P3_4_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x34) |

Port 3 Pin 4 is EUSCI B2 SCL

| #define I2CMSP432_P3_5_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x35) |

Port 3 Pin 5 is EUSCI B0 SDA

| #define I2CMSP432_P3_5_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x35) |

Port 3 Pin 5 is EUSCI B0 SCL

| #define I2CMSP432_P3_5_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x35) |

Port 3 Pin 5 is EUSCI B2 SDA

| #define I2CMSP432_P3_5_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x35) |

Port 3 Pin 5 is EUSCI B2 SCL

| #define I2CMSP432_P3_6_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x36) |

Port 3 Pin 6 is EUSCI B0 SDA

| #define I2CMSP432_P3_6_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x36) |

Port 3 Pin 6 is EUSCI B0 SCL

| #define I2CMSP432_P3_6_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x36) |

Port 3 Pin 6 is EUSCI B2 SDA

| #define I2CMSP432_P3_6_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x36) |

Port 3 Pin 6 is EUSCI B2 SCL

| #define I2CMSP432_P3_7_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x37) |

Port 3 Pin 7 is EUSCI B0 SDA

| #define I2CMSP432_P3_7_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x37) |

Port 3 Pin 7 is EUSCI B0 SCL

| #define I2CMSP432_P3_7_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x37) |

Port 3 Pin 7 is EUSCI B2 SDA

| #define I2CMSP432_P3_7_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x37) |

Port 3 Pin 7 is EUSCI B2 SCL

| #define I2CMSP432_P6_4_UCB1SDA 0x00000164 |

Port 6 Pin 4 is EUSCI B1 SDA

| #define I2CMSP432_P6_5_UCB1SCL 0x00000165 |

Port 6 Pin 5 is EUSCI B1 SCL

| #define I2CMSP432_P6_6_UCB3SDA 0x00000266 |

Port 6 Pin 6 is EUSCI B3 SDA

| #define I2CMSP432_P6_7_UCB3SCL 0x00000267 |

Port 6 Pin 7 is EUSCI B3 SCL

| #define I2CMSP432_P7_0_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x70) |

Port 7 Pin 0 is EUSCI B0 SDA

| #define I2CMSP432_P7_0_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x70) |

Port 7 Pin 0 is EUSCI B0 SCL

| #define I2CMSP432_P7_0_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x70) |

Port 7 Pin 0 is EUSCI B2 SDA

| #define I2CMSP432_P7_0_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x70) |

Port 7 Pin 0 is EUSCI B2 SCL

| #define I2CMSP432_P7_1_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x71) |

Port 7 Pin 1 is EUSCI B0 SDA

| #define I2CMSP432_P7_1_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x71) |

Port 7 Pin 1 is EUSCI B0 SCL

| #define I2CMSP432_P7_1_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x71) |

Port 7 Pin 1 is EUSCI B2 SDA

| #define I2CMSP432_P7_1_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x71) |

Port 7 Pin 1 is EUSCI B2 SCL

| #define I2CMSP432_P7_2_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x72) |

Port 7 Pin 2 is EUSCI B0 SDA

| #define I2CMSP432_P7_2_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x72) |

Port 7 Pin 2 is EUSCI B0 SCL

| #define I2CMSP432_P7_2_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x72) |

Port 7 Pin 2 is EUSCI B2 SDA

| #define I2CMSP432_P7_2_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x72) |

Port 7 Pin 2 is EUSCI B2 SCL

| #define I2CMSP432_P7_3_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x73) |

Port 7 Pin 3 is EUSCI B0 SDA

| #define I2CMSP432_P7_3_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x73) |

Port 7 Pin 3 is EUSCI B0 SCL

| #define I2CMSP432_P7_3_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x73) |

Port 7 Pin 3 is EUSCI B2 SDA

| #define I2CMSP432_P7_3_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x73) |

Port 7 Pin 3 is EUSCI B2 SCL

| #define I2CMSP432_P7_4_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x74) |

Port 7 Pin 4 is EUSCI B0 SDA

| #define I2CMSP432_P7_4_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x74) |

Port 7 Pin 4 is EUSCI B0 SCL

| #define I2CMSP432_P7_4_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x74) |

Port 7 Pin 4 is EUSCI B2 SDA

| #define I2CMSP432_P7_4_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x74) |

Port 7 Pin 4 is EUSCI B2 SCL

| #define I2CMSP432_P7_5_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x75) |

Port 7 Pin 5 is EUSCI B0 SDA

| #define I2CMSP432_P7_5_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x75) |

Port 7 Pin 5 is EUSCI B0 SCL

| #define I2CMSP432_P7_5_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x75) |

Port 7 Pin 5 is EUSCI B2 SDA

| #define I2CMSP432_P7_5_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x75) |

Port 7 Pin 5 is EUSCI B2 SCL

| #define I2CMSP432_P7_6_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x76) |

Port 7 Pin 6 is EUSCI B0 SDA

| #define I2CMSP432_P7_6_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x76) |

Port 7 Pin 6 is EUSCI B0 SCL

| #define I2CMSP432_P7_6_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x76) |

Port 7 Pin 6 is EUSCI B2 SDA

| #define I2CMSP432_P7_6_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x76) |

Port 7 Pin 6 is EUSCI B2 SCL

| #define I2CMSP432_P7_7_UCB0SDA ((PMAP_UCB0SDA << 10) | 0x77) |

Port 7 Pin 7 is EUSCI B0 SDA

| #define I2CMSP432_P7_7_UCB0SCL ((PMAP_UCB0SCL << 10) | 0x77) |

Port 7 Pin 7 is EUSCI B0 SCL

| #define I2CMSP432_P7_7_UCB2SDA ((PMAP_UCB2SDA << 10) | 0x77) |

Port 7 Pin 7 is EUSCI B2 SDA

| #define I2CMSP432_P7_7_UCB2SCL ((PMAP_UCB2SCL << 10) | 0x77) |

Port 7 Pin 7 is EUSCI B2 SCL

| #define I2CMSP432_P10_2_UCB3SDA 0x000001A2 |

Port 10 Pin 2 is EUSCI B3 SDA

| #define I2CMSP432_P10_3_UCB3SCL 0x000001A3 |

Port 10 Pin 3 is EUSCI B3 SCL

| const I2C_FxnTable I2CMSP432_fxnTable |