Functions | |

| void | VIMSConfigure (uint32_t ui32Base, bool bRoundRobin, bool bPrefetch) |

| Configures the VIMS. More... | |

| void | VIMSModeSet (uint32_t ui32Base, uint32_t ui32Mode) |

| Set the operational mode of the VIMS. More... | |

| uint32_t | VIMSModeGet (uint32_t ui32Base) |

| Get the current operational mode of the VIMS. More... | |

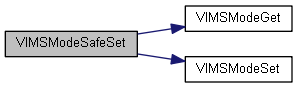

| void | VIMSModeSafeSet (uint32_t ui32Base, uint32_t ui32NewMode, bool blocking) |

| Set the operational mode of the VIMS in a safe sequence. More... | |

| static void | VIMSLineBufDisable (uint32_t ui32Base) |

| Disable VIMS linebuffers. More... | |

| static void | VIMSLineBufEnable (uint32_t ui32Base) |

| Enable VIMS linebuffers. More... | |

| void VIMSConfigure | ( | uint32_t | ui32Base, |

| bool | bRoundRobin, | ||

| bool | bPrefetch | ||

| ) |

Configures the VIMS.

This function sets general control settings of the VIMS system.

| ui32Base | is the base address of the VIMS. |

| bRoundRobin | specifies the arbitration method.

|

| bPrefetch | specifies if prefetching is to be used.

|

|

inlinestatic |

Disable VIMS linebuffers.

Linebuffers should only be disabled when attempting to update the flash, to ensure that the content of the buffers is not stale. As soon as flash is updated the linebuffers should be reenabled. Failing to enable will have a performance impact.

| ui32Base | is the base address of the VIMS. |

|

inlinestatic |

Enable VIMS linebuffers.

Linebuffers should only be disabled when attempting to update the flash, to ensure that the content of the buffers is not stale. As soon as flash is updated the linebuffers should be reenabled. Failing to enable will have a performance impact.

| ui32Base | is the base address of the VIMS. |

| uint32_t VIMSModeGet | ( | uint32_t | ui32Base | ) |

Get the current operational mode of the VIMS.

This function returns the operational mode of the VIMS.

| ui32Base | is the base address of the VIMS. |

Referenced by SysCtrlStandby(), and VIMSModeSafeSet().

| void VIMSModeSafeSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32NewMode, | ||

| bool | blocking | ||

| ) |

Set the operational mode of the VIMS in a safe sequence.

This function sets the operational mode of the VIMS in a safe sequence

Upon reset the VIMS will be in VIMS_MODE_CHANGING mode. In this mode the VIMS will initialize the cache (GP) RAM (to all zeros). The GP RAM will not be operational (read/write will result in bus fault). The Cache will not be operational (read/write to flash will be uncached). After a short delay (approx. 1029 clock cycles) the VIMS will automatically switch mode to VIMS_MODE_DISABLED (GPRAM enabled).

In VIMS_MODE_DISABLED mode, the cache is disabled but the GP RAM is accessible: The GP RAM will be accessible. The Cache will not be operational. Reads from flash will be uncached. From this mode, the VIMS may be put in VIMS_MODE_ENABLED (CACHE mode).

In VIMS_MODE_ENABLED mode, the cache is enabled for USERCODE space. The GP RAM will not be operational (read/write will result in bus fault). The Cache will be operational for SYSCODE space. Reads from flash in USERCODE space will be uncached.

In VIMS_MODE_OFF the cache RAM is off to conserve power.

| ui32Base | is the base address of the VIMS. |

| ui32NewMode | is the new operational mode:

|

| blocking | shall be set to TRUE if further code execution shall be blocked (delayed) until mode change is completed. |

| void VIMSModeSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Mode | ||

| ) |

Set the operational mode of the VIMS.

This function sets the operational mode of the VIMS.

Upon reset the VIMS will be in VIMS_MODE_CHANGING mode. In this mode the VIMS will initialize the cache (GP) RAM (to all zeros). The GP RAM will not be operational (read/write will result in bus fault). The Cache will not be operational. Reads and writes to flash will be uncached. After a short delay (approx. 1029 clock cycles) the VIMS will automatically switch mode to VIMS_MODE_DISABLED (GPRAM enabled).

In VIMS_MODE_DISABLED mode, the cache is disabled but the GP RAM is accessible: The GP RAM will be accessible. The Cache will not be operational. Reads from flash will be uncached. From this mode, the VIMS may be put in VIMS_MODE_ENABLED (CACHE mode).

In VIMS_MODE_ENABLED mode, the cache is enabled for USERCODE space. The GP RAM will not be operational (read/write will result in bus fault). The Cache will be operational for SYSCODE space. Reads from flash in USERCODE space will be uncached.

In VIMS_MODE_OFF the cache RAM is off to conserve power.

| ui32Base | is the base address of the VIMS. |

| ui32Mode | is the operational mode.

|

Referenced by SysCtrlStandby(), and VIMSModeSafeSet().

| #define VIMS_MODE_CHANGING 0x4 |

Referenced by SysCtrlStandby(), VIMSModeGet(), and VIMSModeSafeSet().

| #define VIMS_MODE_DISABLED (VIMS_CTL_MODE_GPRAM) |

Referenced by VIMSModeSafeSet(), and VIMSModeSet().

| #define VIMS_MODE_ENABLED (VIMS_CTL_MODE_CACHE) |

Referenced by SysCtrlStandby(), VIMSModeSafeSet(), and VIMSModeSet().

| #define VIMS_MODE_OFF (VIMS_CTL_MODE_OFF) |

Referenced by SysCtrlStandby(), VIMSModeSafeSet(), and VIMSModeSet().