Functions | |

| void | SysCtrlIdle (uint32_t vimsPdMode) |

| Force the system into idle mode. More... | |

| void | SysCtrlShutdownWithAbort (void) |

| Try to enter shutdown but abort if wakeup event happened before shutdown. More... | |

| void | SysCtrlShutdown (void) |

| Enable shutdown of the device. More... | |

| void | SysCtrlStandby (bool retainCache, uint32_t vimsPdMode, uint32_t rechargeMode) |

| Force the system into standby mode. More... | |

| static uint32_t | SysCtrlClockGet (void) |

| Get the CPU core clock frequency. More... | |

| static void | SysCtrlAonSync (void) |

| Sync all accesses to the AON register interface. More... | |

| static void | SysCtrlAonUpdate (void) |

| Update all interfaces to AON. More... | |

| void | SysCtrlSetRechargeBeforePowerDown (uint32_t xoscPowerMode) |

| Set Recharge values before entering Power Down. More... | |

| void | SysCtrlAdjustRechargeAfterPowerDown (uint32_t vddrRechargeMargin) |

| Adjust Recharge calculations to be used next. More... | |

| void | SysCtrl_DCDC_VoltageConditionalControl (void) |

| Turns DCDC on or off depending of what is considered to be optimal usage. More... | |

| uint32_t | SysCtrlResetSourceGet (void) |

| Returns the reset source (including "wakeup from shutdown"). More... | |

| static void | SysCtrlSystemReset (void) |

| Perform a full system reset. More... | |

| static void | SysCtrlClockLossResetEnable (void) |

| Enables reset if OSC clock loss event is asserted. More... | |

| static void | SysCtrlClockLossResetDisable (void) |

| Disables reset due to OSC clock loss event. More... | |

| #define | RSTSRC_PWR_ON (( AON_PMCTL_RESETCTL_RESET_SRC_PWR_ON ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define | RSTSRC_PIN_RESET (( AON_PMCTL_RESETCTL_RESET_SRC_PIN_RESET ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define | RSTSRC_VDDS_LOSS (( AON_PMCTL_RESETCTL_RESET_SRC_VDDS_LOSS ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define | RSTSRC_VDDR_LOSS (( AON_PMCTL_RESETCTL_RESET_SRC_VDDR_LOSS ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define | RSTSRC_CLK_LOSS (( AON_PMCTL_RESETCTL_RESET_SRC_CLK_LOSS ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define | RSTSRC_SYSRESET (( AON_PMCTL_RESETCTL_RESET_SRC_SYSRESET ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define | RSTSRC_WARMRESET (( AON_PMCTL_RESETCTL_RESET_SRC_WARMRESET ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define | RSTSRC_WAKEUP_FROM_SHUTDOWN ((( AON_PMCTL_RESETCTL_RESET_SRC_M ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) + 1 ) |

| #define | RSTSRC_WAKEUP_FROM_TCK_NOISE ((( AON_PMCTL_RESETCTL_RESET_SRC_M ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) + 2 ) |

| void SysCtrl_DCDC_VoltageConditionalControl | ( | void | ) |

Turns DCDC on or off depending of what is considered to be optimal usage.

This function controls the DCDC only if both the following CCFG settings are true:

The DCDC is configured in accordance to the CCFG settings when turned on.

This function should be called periodically.

| void SysCtrlAdjustRechargeAfterPowerDown | ( | uint32_t | vddrRechargeMargin | ) |

|

inlinestatic |

Sync all accesses to the AON register interface.

When this function returns, all writes to the AON register interface are guaranteed to have propagated to hardware. The function will return immediately if no AON writes are pending; otherwise, it will wait for the next AON clock before returning.

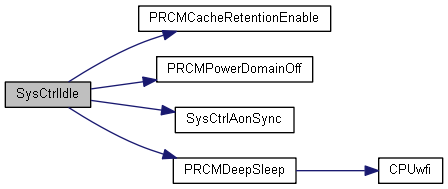

Referenced by SetupAfterColdResetWakeupFromShutDownCfg3(), SysCtrlIdle(), and SysCtrlStandby().

|

inlinestatic |

Update all interfaces to AON.

When this function returns, at least 1 clock cycle has progressed on the AON domain, so that any outstanding updates to and from the AON interface is guaranteed to be in sync.

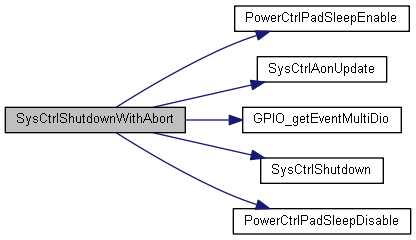

Referenced by SysCtrlShutdownWithAbort().

|

inlinestatic |

Get the CPU core clock frequency.

Use this function to get the current clock frequency for the CPU.

The CPU can run from 48 MHz and down to 750kHz. The frequency is defined by the combined division factor of the SYSBUS and the CPU clock divider.

|

inlinestatic |

Disables reset due to OSC clock loss event.

|

inlinestatic |

Enables reset if OSC clock loss event is asserted.

Clock loss circuit in analog domain must be enabled as well in order to actually enable for a clock loss reset to occur OSCClockLossEventEnable().

| void SysCtrlIdle | ( | uint32_t | vimsPdMode | ) |

Force the system into idle mode.

This function forces the system into IDLE mode by configuring the requested VIMS mode, enabling cache retention and powering off the CPU power domain.

| vimsPdMode | selects the requested VIMS power domain mode The parameter must be one of the following: |

| uint32_t SysCtrlResetSourceGet | ( | void | ) |

Returns the reset source (including "wakeup from shutdown").

In case of RSTSRC_WAKEUP_FROM_SHUTDOWN the application is responsible for unlatching the outputs (disable pad sleep). See PowerCtrlPadSleepDisable() for more information.

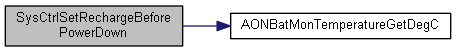

| void SysCtrlSetRechargeBeforePowerDown | ( | uint32_t | xoscPowerMode | ) |

Set Recharge values before entering Power Down.

This function shall be called just before entering Power Down. This function typically does nothing (default setting), but if temperature compensated recharge level are enabled (by setting CCFG_MODE_CONF_VDDR_TRIM_SLEEP_TC = 0) it adds temperature compensation to the recharge level.

| xoscPowerMode | (typically running in XOSC_IN_HIGH_POWER_MODE all the time).

|

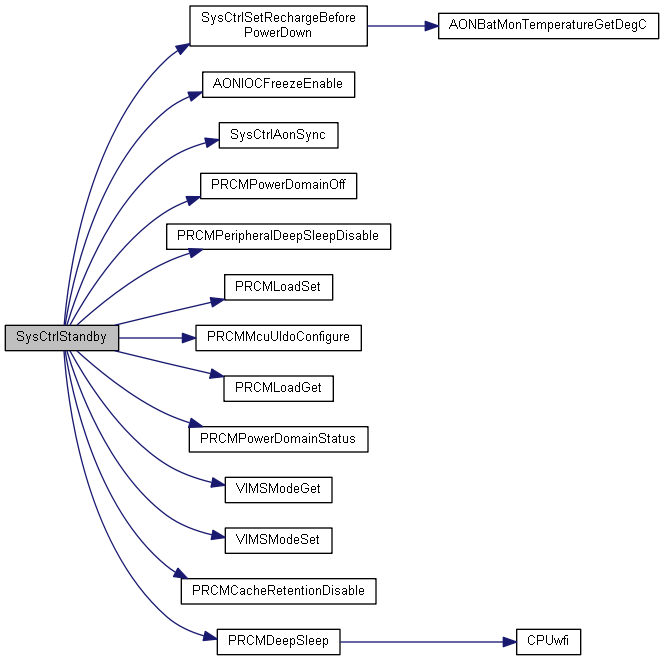

Referenced by SysCtrlStandby().

| void SysCtrlShutdown | ( | void | ) |

Enable shutdown of the device.

This function puts the device in shutdown state. The device automatically latches all outputs (pads in sleep) before it turns off all internal power supplies.

JTAG must be disconnected and JTAG power domain must be off before device can enter shutdown. This function waits until the device satisfies all shutdown conditions before it enters shutdown.

See PowerCtrlPadSleepDisable() for information about how to unlatch outputs (disable pad sleep) after wakeup from shutdown.

See IOCIOShutdownSet() for information about how to enable wakeup from shutdown.

See SysCtrlResetSourceGet() for information about how to detect wakeup from shutdown.

It is recommended to disable interrupts before calling this function. Shutdown happens immediately when the device satisfies all shutdown conditions thus interrupt routines triggered after this function is called might be aborted.

Referenced by SysCtrlShutdownWithAbort().

| void SysCtrlShutdownWithAbort | ( | void | ) |

Try to enter shutdown but abort if wakeup event happened before shutdown.

This function puts the device in shutdown state if no wakeup events are detected before shutdown.

Compared to the basic SysCtrlShutdown() function this function makes sure that wakeup events that happen before actual shutdown are also detected. This function either enters shutdown with a guaranteed wakeup detection or returns to the caller function due to a pre-shutdown wakeup event.

See SysCtrlShutdown() for basic information about how to configure the device before shutdown and how to wakeup from shutdown.

This function uses IO edge detection in addition to the mandatory wakeup configuration. Additional requirements to the application for this function are:

Useful functions related to shutdown:

It is recommended to disable interrupts before calling this function because:

| void SysCtrlStandby | ( | bool | retainCache, |

| uint32_t | vimsPdMode, | ||

| uint32_t | rechargeMode | ||

| ) |

Force the system into standby mode.

This function forces all power domains (RFCORE, SERIAL, PERIPHERAL) off. The VIMS and CPU power domains are turned off by the HW when the PRCMDeepSleep() function is called. The IOs are latched (frozen) before the power domains are turned off to avoid glitches. The VIMS retention (cache) and VIMS module are turned off if requested. The deep-sleep clock for the crypto and DMA modules are turned off, as they must be off in order to enter standby. This function assumes that the LF clock has already been switched to and that the LF clock qualifiers must have been disabled/bypassed.

In internal regulator mode the adaptive recharge functionality is enabled with fixed parameter values. In external regulator mode the recharge functionality is disabled.

| retainCache | selects if VIMS cache shall be retained or not.

|

| vimsPdMode | selects the VIMS power domain mode. The parameter must be one of the following: |

| rechargeMode | specifies the requested recharge mode. The parameter must be one of the following:

|

|

inlinestatic |

Perform a full system reset.

| #define CPU_DEEP_SLEEP 0x00000002 |

| #define CPU_RUN 0x00000000 |

| #define CPU_SLEEP 0x00000001 |

| #define RSTSRC_CLK_LOSS (( AON_PMCTL_RESETCTL_RESET_SRC_CLK_LOSS ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define RSTSRC_PIN_RESET (( AON_PMCTL_RESETCTL_RESET_SRC_PIN_RESET ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define RSTSRC_PWR_ON (( AON_PMCTL_RESETCTL_RESET_SRC_PWR_ON ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define RSTSRC_SYSRESET (( AON_PMCTL_RESETCTL_RESET_SRC_SYSRESET ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define RSTSRC_VDDR_LOSS (( AON_PMCTL_RESETCTL_RESET_SRC_VDDR_LOSS ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define RSTSRC_VDDS_LOSS (( AON_PMCTL_RESETCTL_RESET_SRC_VDDS_LOSS ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define RSTSRC_WAKEUP_FROM_SHUTDOWN ((( AON_PMCTL_RESETCTL_RESET_SRC_M ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) + 1 ) |

Referenced by SysCtrlResetSourceGet().

| #define RSTSRC_WAKEUP_FROM_TCK_NOISE ((( AON_PMCTL_RESETCTL_RESET_SRC_M ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) + 2 ) |

Referenced by SysCtrlResetSourceGet().

| #define RSTSRC_WARMRESET (( AON_PMCTL_RESETCTL_RESET_SRC_WARMRESET ) >> ( AON_PMCTL_RESETCTL_RESET_SRC_S )) |

| #define SYSCTRL_PREFERRED_RECHARGE_MODE 0xFFFFFFFF |

Referenced by SysCtrlStandby().

| #define SYSCTRL_SYSBUS_OFF 0x00000000 |

| #define SYSCTRL_SYSBUS_ON 0x00000001 |

| #define VIMS_NO_PWR_UP_MODE 2 |

| #define VIMS_ON_BUS_ON_MODE 1 |

| #define VIMS_ON_CPU_ON_MODE 0 |

| #define XOSC_IN_HIGH_POWER_MODE 0 |

Referenced by SysCtrlStandby().

| #define XOSC_IN_LOW_POWER_MODE 1 |