4.3. FC¶

4.4. IPC¶

Inter-Processor Communication (IPC) provides a processor-agnostic API which can be used for communication between processors in a multi-processor environment (inter-core), communication to other threads on same processor (inter-process), and communication to peripherals (inter-device). The API supports message passing, streams, and linked lists. IPC can be used to communicate with the following:

- Other threads on the same processor

- Threads on other processors running SYS/BIOS

- Threads on other processors running an HLOS (e.g., Linux, QNX, Android)

4.4.1. IPC User’s Guide¶

This user’s guide is the new home of the Inter-Processor Communication (IPC) User’s Guide (SPRUGO6). That PDF-based document will no longer be updated.

This user’s guide contains the topics in the following list. It also

links to API reference documentation for static configuration ( )

and run-time C processing (

)

and run-time C processing ( ) for each module.

) for each module.

- Use Cases for IPC

- The ti.sdo.ipc Package describes the modules in the ti.sdo.ipc package.

- The ti.sdo.utils Package describes the modules in the ti.sdo.utils package.

- Porting IPC provides an overview of the steps required to port IPC to new devices or systems.

- Optimizing IPC Applications provides hints for improving the runtime performance and shared memory usage of applications that use IPC.

- Rebuilding IPC explains how to rebuild the IPC libraries if you modify the source files.

- Examples explains how to build and generate the IPC examples.

- Tests explains details of unit tests part of IPC

- RTOS IPC Transports explains details of the additional RTOS IPC transports provided via the Processor SDK PDK component.

4.4.1.2. Other TI IPC useful links¶

- IPC 3.x Provides details of IPC 3.x releases

- IPC 3.x Migration Guide Provides details of migrating to IPC 3.x from previous releases

- IPC 3.x FAQ Frequently asked question on IPC 3.x

- IPC Benchmarking IPC Benchmarking with IPC 3.x

4.4.1.3. IPC Install Guides¶

Note

Please see the release notes in your IPC installation before starting to use IPC. The release notes contain important information about feature support, issues, and compatibility information for a particular release.

4.4.2. IPC Install Guides¶

4.4.2.1. BIOS Install Guide¶

4.4.2.1.1. Introduction¶

Inter/Intra Processor Communication (IPC) is a product designed to enable communication between processors in a multi-processor environment. Features of IPC include message passing, multi-processor gates, shared memory primitives, and more.

IPC is designed for use with processors running SYS/BIOS applications. This is typically an ARM or DSP. IPC includes support for High Level Operating Systems (HLOS) like Linux, as well as the SYS/BIOS RTOS. The breadth of IPC features supported in an HLOS environment is reduced in an effort to simplify the product.

4.4.2.1.2. Install¶

IPC is often distributed and installed within a larger SDK. In those cases, no installation is required.

Outside of an SDK, IPC can be downloaded here, and is released as a zip file. To install, simply extract the file.

buildhost$ unzip ipc_<version>.zip

This will extract the IPC product in a directory with its product name and version information (e.g. c:/ti/ipc_<version>)

Note

- This document assumes the IPC install path to be the user’s home directory on a Linux host machine (/home/<user>) or the user’s main drive on a Windows host machine (C:\). The variable IPC_INSTALL_DIR will be used throughout the document. If IPC was installed at a different location, make appropriate changes to commands.

- Some customers find value in archiving the released sources in a configuration management system. This can help in identifying any changes made to the original sources - often useful when updating to newer releases.

4.4.2.1.3. Build¶

The IPC product often comes with prebuilt libraries, so rebuilding them isn’t necessary. The IPC product downloads contain prebuilt libraries, and when provided with an SDK, IPC is typically rebuilt to contain only libraries appropriate for the SDK.

However, if you want to rebuild its libraries, IPC provides GNU makefile(s) at the base of the product. This section describes the steps required to rebuild the IPC libraries.

Note

GNU make version 3.81 or greater is required. The XDC tools (provided with most SDKs and CCS distributions) includes a pre-compiled version of GNU make 3.81 in $(XDC_INSTALL_DIR)/gmake.

4.4.2.1.3.1. products.mak¶

IPC contains a products.mak file at the root of the product that specifies the necessary paths and options to build IPC for the various OS support.

Edit products.mak and set the following variables:

Note

Please make sure the complete path is specified. (e.g) Don’t use ~ in the path specified.

- XDC_INSTALL_DIR - Path to TI’s XDCTools installation

- BIOS_INSTALL_DIR - Path to TI’s SYS/BIOS installation

- ti.targets.<device target and file format> - Path to TI toolchain

for the device.

- Set only the variables to the targets your device supports to minimize build time.

- gnu.targets.arm.<device target and file format> - Path to GNU

toolchain for the device.

- Set only the variables to the targets your device supports to minimize build time.

- PLATFORM - (Optional) platform for which to build executables

- Introduced in IPC 3.10. Prior releases build executables for all platforms based on that targets/toolchains set above

- If not set, only libraries will be built (not executables)

Note

The versions used during validation can be found in the IPC Release Notes provided in the product.

4.4.2.1.3.2. ipc-bios.mak¶

IPC is built with a GNU makefile. After editing products.mak, issue the following command:

<buildhost> make -f ipc-bios.mak all

Based on the number of targets you’re building for, this may take some time.

4.4.2.1.4. Examples¶

The IPC product contains an examples/archive directory with device-specific examples. Once identifying your device, the examples can be unzipped anywhere on your build host. Typically once unzipped, the user edits the example’s individual products.mak file and simply invokes make.

Note

A common place to unzip the examples is into the IPC_INSTALL_DIR/examples/ directory. Each example’s products.mak file is smart enough to look up two directories (in this case, into IPC_INSTALL_DIR) for a master products.mak file, and if found it uses those variables. This technique enables users to set the dependency variables in one place, namely IPC_INSTALL_DIR/products.mak.

Each example contains a readme.txt with example-specific details.

4.4.2.1.5. See Also¶

4.4.2.2. Linux Install Guide¶

4.4.2.2.1. Introduction¶

Inter/Intra Processor Communication (IPC) is a product designed to enable communication between processors in a multi-processor environment. Features of IPC include message passing, multi-processor gates, shared memory primitives, and more.

IPC is designed for use with processors running SYS/BIOS applications. This is typically an ARM or DSP. IPC includes support for High Level Operating Systems (HLOS) like Linux, as well as the SYS/BIOS RTOS. The breadth of IPC features supported in an HLOS environment is reduced in an effort to simplify the product.

4.4.2.2.2. Install¶

IPC is often distributed and installed within a larger SDK. In those cases, no installation is required.

Outside of an SDK, IPC can be downloaded here, and is released as a zip file. To install, simply extract the file.

buildhost$ unzip ipc_<version>.zip

This will extract the IPC product in a directory with its product name and version information (e.g. c:/ti/ipc_<version>)

Note

- This document assumes the IPC install path to be the user’s home directory on a Linux host machine (/home/<user>) or the user’s main drive on a Windows host machine (C:\). The variable IPC_INSTALL_DIR will be used throughout the document. If IPC was installed at a different location, make appropriate changes to commands.

- Some customers find value in archiving the released sources in a configuration management system. This can help in identifying any changes made to the original sources - often useful when updating to newer releases.

4.4.2.2.3. Build¶

The IPC product often comes with prebuilt SYS/BIOS-side libraries, so rebuilding them isn’t necessary. The Linux-side user libraries may also be provided prebuilt, but customers often want to change the configuration (e.g. static, dynamic).

IPC provides GNU makefile(s) to rebuild all its libraries at the base of the product, details are below.

Note

GNU make version 3.81 or greater is required. The XDC tools (provided with most SDKs and CCS distributions) includes a pre-compiled version of GNU make 3.81 in $(XDC_INSTALL_DIR)/gmake.

4.4.2.2.3.1. products.mak¶

IPC contains a products.mak file at the root of the product that specifies the necessary paths and options to build IPC for the various OS support.

Edit products.mak and set the following variables:

- Variables used by both Linux-side and BIOS-side build scripts

- PLATFORM - (Optional) Device to build for

- To find the supported list of platforms, run: ./configure –help

- If not set, Linux libraries and executables for all supported platforms will be built.

- If not set, BIOS libraries for all toolchains specified (see

below) will be built, but no BIOS-side executables will be

built.

- BIOS-side builds started leveraging this variable in IPC 3.10. Prior releases built BIOS-side executables for all supported platforms based on that targets/toolchains set above (which can take a while!)

- PLATFORM - (Optional) Device to build for

- Variables used by Linux-side build scripts

- TOOLCHAIN_INSTALL_DIR - Path to the devices ARM Linux cross-compiler toolchain

- TOOLCHAIN_LONGNAME - Long name of the devices toolchain (e.g. arm-none-linux-gnueabi)

- KERNEL_INSTALL_DIR - Location of your Linux kernel

installation

- In old releases, this variable was optional, and only needed for platforms that support the MmRpc API (e.g. OMAP5, DRA7XX). In IPC 3.00.04, 3.10.02, and 3.20+, all platforms began requiring this variable to interrogate your kernel’s version (via KERNEL_INSTALL_DIR/linux/version.h) and accommodate different kernels.

- DRM_PREFIX - (Optional) Location of your libdrm installation,

used by some MmRpc tests

- This is only used by MmRpc tests, and therefore only should be set for platforms that support the MmRpc API

- If set, additional MmRpc tests may be built.

- CMEM_INSTALL_DIR - (Optional) Path to TI Linux Utils package

to locate the pre-built

CMEM

libraries used by some MessageQ tests

- If set, additional test applications for select platforms may be built.

- Variables used by BIOS-side build scripts

- XDC_INSTALL_DIR - Path to TI’s XDCTools installation (e.g. c:/ti/xdctools_<version>)

- BIOS_INSTALL_DIR - Path to TI’s SYS/BIOS installation (e.g. c:/ti/bios_<version>)

- ti.targets.<device target and file format> - Path to TI

toolchain for the device. (e.g.

c:/ti/CCS/ccsbase/tools/compiler/c6000_<version>)

- Set only the variables to the targets your device supports to minimize build time.

Note

The specific versions of dependent components can be found in the IPC Release Notes, provided in the product.

4.4.2.2.3.2. ipc-linux.mak¶

The Linux-side build is provided as a GNU Autotools (Autoconf, Automake, Libtool) project. If you are familiar with Autoconf GNU projects, you can proceed with using the ./configure script directly to cross-compile the Linux user libraries and tests.

For those that require some assistance, the IPC package provides a GNU makefile (ipc-linux.mak) to configure the Linux-side build, using the options and component paths set in the products.mak file. To configure the build using these files, issue the following command:

<buildhost> make -f ipc-linux.mak config

There are few additional target goals provided in the ipc-linux.mak file for commonly used configurations. These goals include:

- config - (Default) Configure both static and shared (dynamic) Linux IPC user libraries. Executables (e.g. lad and tests) link against the shared libraries.

- config-static - Configure static only libraries and executables.

- config-shared - Configure shared (dynamic) only libraries and executables.

Once the ‘config’ is complete, and the autotools-generated Makefile has been created, you can build the Linux side of IPC by issuing the following:

<buildhost> make

You can also specify a PLATFORM to (re)configure for on the command line which overrides any options set in the products.mak file as follows:

<buildhost> make -f ipc-linux.mak config PLATFORM=omapl138

<buildhost> make

Note that before reconfiguring for a new Linux toolchain or platform, the autotools-generated files should be clean(ed):

<buildhost> make distclean

4.4.2.2.3.3. ipc-bios.mak¶

The SYS/BIOS-side IPC is built with a GNU makefile. After editing products.mak, issue the following command:

<buildhost> make -f ipc-bios.mak all

Based on the number of targets you’re building for, this may take some time.

Note

The BIOS-side libraries often come pre-built, so in many cases, rebuilding the BIOS-side is not necessary. Some reasons you may want to rebuild:

- Your distribution of IPC didn’t come with the necessary pre-built libraries

- You intend to run the ‘test’ executables (which often don’t come pre-built)

- You want to use a specific toolchain or dependency version

- You want to tune some of the compile options

4.4.2.2.4. Run¶

The IPC product provides a way to install (copy) the necessary IPC executables and libraries onto the device’s target file-system to simplify the execution of the applications.

4.4.2.2.4.1. Configuring Kernel¶

The IPC product provides a set of Linux kernel patches that need to be applied to the different device supported kernels to add necessary kernel support. The patches are located in the linux/patches directory of the IPC installation.

4.4.2.2.4.1.1. OMAP-L138¶

The kernel for the OMAP-L138, can be obtained from Gitorious linux-davinci project.

The patches apply to the following commit id: 595ab716fc6e648b7dc79a58a01917ebb67b9508

The specific patches needed for this kernel can be found in the linux/patches/3.8.0 of your IPC installation.

Once the patches are applied, there are a few key config parameters needed for rpmsg and socket driver to build/work.

CONFIG_REMOTEPROC=m CONFIG_DA8XX_REMOTEPROC=m CONFIG_RPMSG=m CONFIG_VIRTIO=m It is also recommended to compile a Linux kernel with the debugfs facility

CONFIG_DEBUG_FS=y Re-build the kernel. For example:

buildhost$ make ARCH=arm CROSS_COMPILE=arm-none-linux-gnueabi- uImage

You will also need to re-build the kernel modules and install them on your target’s file system. For example:

buildhost$ make ARCH=arm CROSS_COMPILE=arm-none-linux-gnueabi- modules

buildhost$ make ARCH=arm CROSS_COMPILE=arm-none-linux-gnueabi- INSTALL_MOD_PATH=<target filesystem> modules_install

4.4.2.2.4.2. Kernel Boot-up Parameters¶

IPC requires an argument to be passed to the Linux kernel during boot up to properly run the tests. The remote processor(s) (rproc) memory location needs to be set.

- For example,

bootargs console=ttyS2,115200n8 root=/dev/nfs nfsroot=HOST:nfs_root,nolock rw ip=dhcp rproc_mem=16M@0xC3000000

This is just an example, bootargs may vary depending on available setup Depending on the memory map used in the final system configuration, the memory to be reserved for rproc usage may differ.

4.4.2.2.4.3. Installing Tests¶

To assemble the IPC test executables and libraries into a directory structure suitable for running on the target’s file-system, issue the following command in the IPC install directory:

buildhost$ make install prefix=<target filesystem>/usr

Depending on you target’s filesystem directory privileges, you may be required to run **sudo make install* to properly install the files *

Note

The test executables and libraries will be installed in the location path set by the prefix variable. If you are installing directly on a host mounted Network Filesystem(NFS), make sure to specify usr at the end of the prefix variable path. As with other variables, you can override this on the command line:

buildhost$ sudo make install prefix=<target filesystem>/usr

The remote processor’s applications will be loaded via the remote_proc kernel module but they need to reside on the devices target filesystem in /lib/firmware directory. The location of the remote core application within the IPC product various based on device.

4.4.2.2.4.3.1. Slave Binaries¶

The slave-side test binaries, once built, are found in your IPC_INSTALL_DIR/packages/ti/ipc/tests/bin/<platform>_<core> directory.

Copy the appropriate slave-side executable onto the devices target filesystem into the /lib/firmware directory. For example, OMAP-L138 developers would do this:

buildhost$ cp IPC_INSTALL_DIR/packages/ti/ipc/tests/bin/ti_platforms_evmOMAPL138_DSP/ <target filesystem>/lib/firmware/.

4.4.2.2.4.3.2. IPC Daemons and Drivers¶

IPC provides system-wide services across multiple applications, and utilizes low-level system hardware (e.g. interrupts and shared memory). To facilitate these services, IPC uses a user-space daemon (LAD) and several kernel device drivers.

LAD

System-wide IPC state is managed by a user-space daemon (LAD). This daemon is specific to a given device, and is named lad_<device>. It will reside on the target’s filesystem (typically in /usr/bin/) after following the #Installing Tests section. To run LAD, execute:

target# /usr/bin/lad_<device>

This forks the LAD daemon and leaves it running in the background.

LAD takes an optional argument to indicate a filename into which log statements should be emitted. This file will be created in the /tmp/LAD/ directory. How to specify the filename varies based on your IPC release. For example, to instruct LAD to emit log statements into a ‘lad.txt’ file, start LAD like this:

- Releases before IPC 3.21:

target# /usr/bin/lad_<device> lad.txt

- IPC 3.21 and after:

target# /usr/bin/lad_<device> -l lad.txt

Drivers

The kernel drivers/modules added by the Linux patches must be inserted into the kernel for IPC applications to run correctly. Refer to the #Configuring Kernel section. The required modules must be configured, built and loaded onto the target’s filesystem.

Prior to loading the modules, a directory (/debug) must be created at the root of your devices filesystem. This directory will be mounted as a debugfs (debug filesystem) which the kernel modules will use to provide details about the slaves (e.g. running state, trace output, etc). If the /debug directory doesn’t exist, simply create it as follows:

target# mkdir /debug

OMAP-L138

On OMAP-L138, the kernel modules can be loaded with the following command on the target’s file-system:

target# depmod -a

target# mount -t debugfs none /debug

target# modprobe remoteproc

target# modprobe da8xx_remoteproc da8xx_fw_name=messageq_single.xe674

target# modprobe virtio_rpmsg_bus

target# modprobe rpmsg_proto

The kernel modules can be unloaded by issuing the following command on the target’s file-system:

target# umount /debug

target# rmmod rpmsg_proto

target# rmmod virtio_rpmsg_bus

target# rmmod da8xx_remoteproc

target# rmmod remoteproc

OMAP54XX

On OMAP54XX, the kernel modules can be loaded with the following command on the target’s file-system:

target# depmod -a

target# mount -t debugfs none /debug

target# modprobe remoteproc

target# modprobe omap_remoteproc

target# modprobe virtio_rpmsg_bus

target# modprobe rpmsg_proto

4.4.2.2.4.3.3. Running Test Applications¶

The test applications are already on the target’s filesystem in /usr/bin assuming the #Installing Tests section has been followed.

To run the test application’s, execute the following on the target’s filesystem:

target# /usr/bin/MessageQApp_<device>

OMAP-L138

The expected output on the Linux-side should be:

Using numLoops: 100; procId : 1

Entered MessageQApp_execute

Local MessageQId: 0x1

Remote queueId [0x10000]

Exchanging 100 messages with remote processor DSP...

MessageQ_get #0 Msg = 0x15328

Exchanged 1 messages with remote processor DSP

MessageQ_get #1 Msg = 0x15328

...

...

Exchanged 99 messages with remote processor DSP

MessageQ_get #99 Msg = 0x15328

Exchanged 100 messages with remote processor DSP

Sample application successfully completed!

Leaving MessageQApp_execute

The output on the remote processor, can be obtained by running the following on the target filesystem:

target# cat /debug/remoteproc/remoteproc0/trace0

The expected output on the remote processor should be:

3 Resource entries at 0xc3100000

messageq_single.c:main: MultiProc id = 1

registering rpmsg-proto service on 61 with HOST

tsk1Fxn: created MessageQ: SLAVE_DSP; QueueID: 0x10000

Awaiting sync message from host...

[t=0x00000001:67984156] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: no object for endpoint: 53

[t=0x00000001:67f626ed] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: no object for endpoint: 53

Received msg from (procId:remoteQueueId): 0x0:0x1

payload: 8 bytes; loops: 100 with printing.

Got msg #0 (40 bytes) from procId 0

Sending msg Id #0 to procId 0

Got msg #1 (40 bytes) from procId 0

Sending msg Id #1 to procId 0

...

...

Got msg #98 (40 bytes) from procId 0

Sending msg Id #98 to procId 0

Got msg #99 (40 bytes) from procId 0

Sending msg Id #99 to procId 0

Awaiting sync message from host...

[t=0x00000015:7b46c4c2] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: no object for endpoint: 53

[t=0x00000015:7b6315fb] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: no object for endpoint: 53

4.4.2.2.5. See Also¶

4.4.2.3. QNX Install Guide¶

4.4.2.3.1. Introduction¶

Inter/Intra Processor Communication (IPC) is a product designed to enable communication between processors in a multi-processor environment. Features of IPC include message passing, multi-processor gates, shared memory primitives, and more.

IPC is designed for use with processors running SYS/BIOS applications. This is typically an ARM or DSP. IPC includes support for High Level Operating Systems (HLOS) like Linux, as well as the SYS/BIOS RTOS. The breadth of IPC features supported in an HLOS environment is reduced in an effort to simplify the product.

4.4.2.3.2. Install¶

IPC is often distributed and installed within a larger SDK. In those cases, no installation is required.

Outside of an SDK, IPC can be downloaded here, and is released as a zip file. To install, simply extract the file.

buildhost$ unzip ipc_<version>.zip

This will extract the IPC product in a directory with its product name and version information (e.g. c:/ti/ipc_<version>)

Note

- This document assumes the IPC install path to be the user’s home directory on a Linux host machine (/home/<user>) or the user’s main drive on a Windows host machine (C:\). The variable IPC_INSTALL_DIR will be used throughout the document. If IPC was installed at a different location, make appropriate changes to commands.

- Some customers find value in archiving the released sources in a configuration management system. This can help in identifying any changes made to the original sources - often useful when updating to newer releases.

4.4.2.3.3. Build¶

The IPC product often comes with prebuilt SYS/BIOS-side libraries, so rebuilding them isn’t necessary. The QNX-side libraries/binaries may also be provided prebuilt by SDK programs, but the standalone IPC release does not currently pre-build them.

IPC provides GNU makefile(s) to rebuild all its libraries at the base of the product, details are below.

Note

GNU make version 3.81 or greater is required. The XDC tools (provided with most SDKs and CCS distributions) includes a pre-compiled version of GNU make 3.81 in $(XDC_INSTALL_DIR)/gmake.

4.4.2.3.3.1. products.mak¶

IPC contains a products.mak file at the root of the product that specifies the necessary paths and options to build IPC for the various OS support.

Edit products.mak and set the following variables:

- Variables used by both QNX and BIOS

- PLATFORM - Device to build for

- QNX started using this variable in IPC 3.20. Prior releases required setting “DEVICE” for QNX and “PLATFORM” for BIOS. The two variables were consolidated in IPC 3.20.

- BIOS started leveraging this variable in IPC 3.10. Prior releases built BIOS-side executables for all supported platforms based on that targets/toolchains set above (which can take a while!)

- PLATFORM - Device to build for

- QNX

- QNX_INSTALL_DIR - Path to your QNX installation directory.

- DESTDIR - Path to which target binaries will be exported when running the ‘make install’ goal.

- DEVICE - (only required for releases prior to IPC 3.20) Device to build for

- SYS/BIOS

- XDC_INSTALL_DIR - Path to TI’s XDCTools installation

- BIOS_INSTALL_DIR - Path to TI’s SYS/BIOS installation

- ti.targets.<device target and file format> - Path to TI

toolchain for the device.

- Set only the variables to the targets your device supports to minimize build time.

- gnu.targets.arm.<device target and file format> - Path to GNU

toolchain for the device.

- Set only the variables to the targets your device supports to minimize build time.

Note

The versions used during validation can be found in the IPC Release Notes provided in the product.

ipc-qnx.mak

The QNX-side build is performed using QNX makefiles. To build using the components paths set in the products.mak file, issue the following command:

<buildhost> make -f ipc-qnx.mak all

4.4.2.3.3.2. ipc-bios.mak¶

The SYS/BIOS-side IPC is built with a GNU makefile. After editing products.mak, issue the following command:

<buildhost> make -f ipc-bios.mak all

Based on the number of targets you’re building for, this may take some time.

Note for Windows users: If you are building with a Windows host machine and it has the QNX tools installed, you will instead need to run the following in a separate command prompt window (cmd.exe) to build the SYS/BIOS side outside of the QNX build environment:

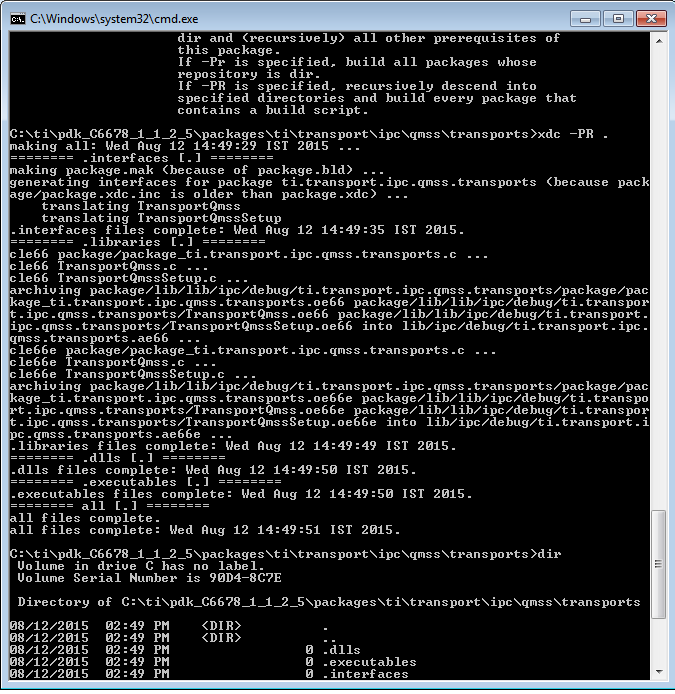

<buildhost> set PATH=C:\Windows\system32;C:\Windows;C:\Windows\System32\Wbem

<buildhost> <XDC_INSTALL_DIR>\gmake -f ipc-bios.mak all

where <XDC_INSTALL_DIR> should be replaced with the installation directory of your XDC tools, same as the path you have used in products.mak.

4.4.2.3.4. Run¶

The IPC product provides a way to install (copy) the necessary IPC executables and libraries onto the device’s target file-system to simplify the execution of the applications. The details can vary across OS’s, so this description has been separated into OS-specific sections.

4.4.2.3.4.1. Configuring the BSP¶

Some of the provided IPC tests that use a utility called SharedMemoryAllocator require a carveout to be created in the QNX-owned memory. To reserve this memory, you must make the following change in the file <QNX BSP installation directory>srchardwarestartupboards<board name>build in the QNX BSP. E.g.

startup-omap5432uevm -r 0xBA300000,0x5A00000 -vvvvv -P2 -W

Save the file, then rebuild the QNX OS image (ifs-*.bin) and replace your existing one with the new one.

4.4.2.3.4.2. Installing Tests in QNX¶

To assemble the IPC resource manager, shared libraries and test executables into a directory structure suitable for running on the device’s file-system, issue the following command in the IPC_INSTALL_DIR directory:

buildhost$ make -f ipc-qnx.mak install

This will install the binaries into the directory specified by DESTDIR in products.mak. It this assumed that DESTDIR is a directory visible to the target filesystem. If not, you should copy its contents to such a location (e.g. onto an SD card that can be accessed by the EVM).

When building in Windows, some users might get build messages that report a version mismatch in cygwin:

C:/QNX650/host/win32/x86/usr/bin/make -j 1 -Cle.v7 -fMakefile install

1 [main] ? (5984) C:\QNX650\host\win32\x86\usr\photon\bin\find.exe: *** fa

tal error - system shared memory version mismatch detected - 0x8A88009C/0x2D1E009C.

This problem is probably due to using incompatible versions of the cygwin DLL.

Search for cygwin1.dll using the Windows Start->Find/Search facility

and delete all but the most recent version. The most recent version *should*

reside in x:\cygwin\bin, where 'x' is the drive on which you have

installed the cygwin distribution. Rebooting is also suggested if you

are unable to find another cygwin DLL.

Based on what we observed the binaries are still exported correctly despite the messages. If you do want to eliminate them, you should replace the file cygwin1.dll in <QNX_INSTALL_DIR>hostwin32x86usrphotonbin with the newest cygwin1.dll you can find on your host machine (do a search on your PC’s filesystem in Windows).

Some of the tests rely on corresponding remote core applications to be run on the slave processor(s). The remote processor’s applications are loaded when launching the resource manager. See section #IPC_resource_manager for details on launching the resource manager.

The location of the remote core applications within the IPC product varies based on device.

4.4.2.3.4.2.1. Installing remote core applications¶

Remote core applications can be found in <IPC_INSTALL_DIR>/packages/ti/ipc/tests/bin/ti_platform_<your platform name>_* directories.

For example, you can copy the messageq_single.xem4 for OMAP54xx uEVM’s IPU onto the device’s target filesystem into the bin directory as follows:

buildhost$ copy <IPC_INSTALL_DIR>/packages/ti/ipc/tests/bin/ti_platform_omap54xx_ipu/messageq_single.xem4 <DESTDIR>/armle-v7/bin

‘ti_platform_omap54xx_ipu’ indicates the platform is ‘omap54xx’ and the remote core name is ‘IPU’. You only need to copy the binaries relevant to your platform.

4.4.2.3.4.3. IPC resource manager¶

Much of the functionality of IPC is provided by the resource manager. It can be launched as follows:

target# cd <target directory corresponding to DESTDIR>/armle-v7/bin

target# export LD_LIBRARY_PATH=$LD_LIBRARY_PATH:<target directory corresponding to DESTDIR>/armle-v7/usr/lib

target# ipc <CORE1> <remote executable 1> <CORE2> <remote executable 2> ...

<CORE> should correspond to the name of the remote core on which you want the remote executable to be loaded. As a rule of thumb, it is the capitalized version of the core name specified by the name of the directory from which the executable was copied in the #Installing remote core applications section. For example, if the executable is copied from “ti_platform_omap54xx_**ipu**/test_omx_ipu_omap5.xem4”, then you should load it as follows:

target# ipc IPU test_omx_ipu_omap5.xem4

The resource manager will register devices in the pathname space for communicating with the IPC. Communication with the IPC is only possible once the needed devices are registered. The following devices are registered by default when the IPC resource manager is launched:

| Device | Description |

|---|---|

| /dev/tiipc | Provides the “ti-ipc” protocol. Needed by MessageQ APIs. |

| /dev/ipc | Provides the HWSpinLock functionality. Needed by GateMP APIs. |

Additionally, more devices may be registered by the remote core firmware if using the “rpmsg-rpc” protocol. In that case, the name that appears in the pathname space is specified by the remote core firmware.

Later, when you are done running applications that use IPC and no longer need the resource manager, it can be terminated as follows:

target# cd <target directory corresponding to DESTDIR>/armle-v7/bin

target# slay ipc

4.4.2.3.4.4. Running Test Applications¶

The QNX-side of the test applications are already on the target’s filesystem in <target directory corresponding to DESTDIR>/armle-v7/bin and <target directory corresponding to DESTDIR>/armle-v7/bin/tests, assuming the #Installing Tests in QNX and #IPC resource manager sections have been followed and that the resource manager has loaded the remote core(s) with the executable corresponding to the test you’d like to run.

To find out the syntax to use for running the test (say MessageQApp), run

target# cd <target directory corresponding to DESTDIR>/armle-v7/bin/tests

target# use MessageQApp

To run a test application, execute it on the target’s filesystem:

target# cd <target directory corresponding to DESTDIR>/armle-v7/bin/tests

target# ./MessageQApp 10

Here is a list of the main tests that are available in the IPC product:

- MessageQApp: Test that creates a single thread that sends messages

from host to remote core using MessageQ

- messageq_single.x* need to be loaded by the resource manager

- MessageQMulti: Test that creates multiple threads which send messages

from host to remote core using MessageQ

- messageq_multi.x* need to be loaded by the resource manager

- mmrpc_test: Test that exercises MMRPC

- test_omx_ipu_<platform>.x* need to be loaded by the resource manager

- Aside from the IPC resource manager, this test also needs the shmemallocator resource manager to be launched beforehand:

target# cd <target directory corresponding to DESTDIR>/armle-v7/bin

target# shmemallocator

target# cd tests

target# mmrpc_test 1

Expected output

To give you an idea, the expected output for MessageQApp on the QNX-side should look similar to this:

Using numLoops: 10; procId : 1

Entered MessageQApp_execute

Local MessageQId: 0x1

Remote queueId [0x10000]

Exchanging 10 messages with remote processor IPU...

MessageQ_get #0 Msg = 0x11c9f0

Exchanged 1 messages with remote processor IPU

MessageQ_get #1 Msg = 0x11c9f0

Exchanged 2 messages with remote processor IPU

MessageQ_get #2 Msg = 0x11c9f0

...

...

Exchanged 9 messages with remote processor IPU

MessageQ_get #9 Msg = 0x11c9f0

Exchanged 10 messages with remote processor IPU

Sample application successfully completed!

Leaving MessageQApp_execute

The output on the remote processor can be obtained by running the following on the target filesystem:

target# cat /dev/ipc-trace/IPU

The expected output on the remote processor should look similar to this:

[0][ 0.000] 16 Resource entries at 0x3000

[0][ 0.000] messageq_single.c:main: MultiProc id = 1

[0][ 0.000] [t=0x006c565d] ti.ipc.transports.TransportVirtioSetup: TransportVirtio

Setup_attach: remoteProcId: 0

[0][ 0.000] registering rpmsg-proto:rpmsg-proto service on 61 with HOST

[0][ 0.000] [t=0x0072625b] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_create: endPt c

reated: 61

[0][ 0.000] [t=0x0073e8d9] ti.ipc.rpmsg.MessageQCopy: callback_availBufReady: virt

Queue_toHost kicked

[0][ 0.000] [t=0x00753771] ti.ipc.rpmsg.MessageQCopy: callback_availBufReady: virt

Queue_fromHost kicked

[0][ 0.000] [t=0x0076cb49] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_swiFxn:

[0][ 0.000] Received msg: from: 0x5a, to: 0x35, dataLen: 72

[0][ 0.000] [t=0x007872e9] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: no object

for endpoint: 53

[0][ 0.000] tsk1Fxn: created MessageQ: SLAVE_CORE0; QueueID: 0x10000

[0][ 0.000] Awaiting sync message from host...

[0][ 51.992] [t=0x0c475268] ti.ipc.rpmsg.MessageQCopy: callback_availBufReady: virt

Queue_fromHost kicked

[0][ 51.992] [t=0x0c48eb28] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_swiFxn:

[0][ 51.993] Received msg: from: 0x400, to: 0x3d, dataLen: 176

[0][ 51.993] [t=0x0c4ad220] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: calling c

allback with data len: 176, from: 1024

[0][ 51.993]

[0][ 52.995] [t=0x0c873ded] ti.ipc.rpmsg.MessageQCopy: callback_availBufReady: virt

Queue_fromHost kicked

[0][ 52.996] [t=0x0c88b029] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_swiFxn:

[0][ 52.996] Received msg: from: 0x406, to: 0x3d, dataLen: 40

[0][ 52.996] [t=0x0c8a8a87] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: calling c

allback with data len: 40, from: 1030

[0][ 52.996]

[0][ 52.996] Received msg from (procId:remoteQueueId): 0x0:0x1

[0][ 52.996] payload: 8 bytes; loops: 10 with printing.

[0][ 52.997] [t=0x0c8eab7e] ti.ipc.rpmsg.MessageQCopy: callback_availBufReady: virt

Queue_fromHost kicked

[0][ 52.997] [t=0x0c9031bc] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_swiFxn:

[0][ 52.997] Received msg: from: 0x406, to: 0x3d, dataLen: 40

[0][ 52.997] [t=0x0c9208fa] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: calling c

allback with data len: 40, from: 1030

[0][ 52.997]

[0][ 52.997] Got msg #0 (40 bytes) from procId 0

[0][ 52.997] Sending msg Id #0 to procId 0

[0][ 52.998] [t=0x0c959f33] ti.ipc.rpmsg.MessageQCopy: callback_availBufReady: virt

Queue_fromHost kicked

[0][ 52.998] [t=0x0c971df7] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_swiFxn:

[0][ 52.998] Received msg: from: 0x406, to: 0x3d, dataLen: 40

[0][ 52.998] [t=0x0c98f3e7] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: calling c

allback with data len: 40, from: 1030

[0][ 52.998]

[0][ 52.999] Got msg #1 (40 bytes) from procId 0

[0][ 52.999] Sending msg Id #1 to procId 0

[0][ 52.999] [t=0x0c9c7a00] ti.ipc.rpmsg.MessageQCopy: callback_availBufReady: virt

Queue_fromHost kicked

[0][ 52.999] [t=0x0c9df7fc] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_swiFxn:

[0][ 52.999] Received msg: from: 0x406, to: 0x3d, dataLen: 40

[0][ 52.999] [t=0x0c9fce5a] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: calling c

allback with data len: 40, from: 1030

[0][ 52.999]

[0][ 53.000] Got msg #2 (40 bytes) from procId 0

[0][ 53.000] Sending msg Id #2 to procId 0

[0][ 53.000] [t=0x0ca36e79] ti.ipc.rpmsg.MessageQCopy: callback_availBufReady: virt

Queue_fromHost kicked

[0][ 53.000] [t=0x0ca4ea95] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_swiFxn:

[0][ 53.000] Received msg: from: 0x406, to: 0x3d, dataLen: 40

[0][ 53.001] [t=0x0ca6c975] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: calling c

allback with data len: 40, from: 1030

[0][ 53.001]

[0][ 53.001] Got msg #3 (40 bytes) from procId 0

[0][ 53.001] Sending msg Id #3 to procId 0

...

...

[0][ 53.007] Got msg #8 (40 bytes) from procId 0

[0][ 53.007] Sending msg Id #8 to procId 0

[0][ 53.007] [t=0x0cccd3d7] ti.ipc.rpmsg.MessageQCopy: callback_availBufReady: virt

Queue_fromHost kicked

[0][ 53.007] [t=0x0cce50ed] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_swiFxn:

[0][ 53.007] Received msg: from: 0x406, to: 0x3d, dataLen: 40

[0][ 53.007] [t=0x0cd027bd] ti.ipc.rpmsg.MessageQCopy: MessageQCopy_send: calling c

allback with data len: 40, from: 1030

[0][ 53.007]

[0][ 53.008] Got msg #9 (40 bytes) from procId 0

[0][ 53.008] Sending msg Id #9 to procId 0

[0][ 53.008] Awaiting sync message from host...

4.4.2.3.4.5. Running standalone examples¶

On some platforms, there are standalone examples provided to illustrate how to use specific features in IPC. These standalone examples are designed to be easily rebuilt outside of the IPC product, and represent a good starting point for development. If available, the examples are located in <IPC_INSTALL_DIR>examplesarchive<platform of your choice>.

To use the examples, unzip the example you want in a working directory of your choice. Update the products.mak file in the example’s directory with the installation locations of the various dependent components. Then build it. E.g.:

buildhost$ unzip ex02_messageq.zip

buildhost$ cd ex02_messageq

buildhost$ make clean

buildhost$ make

buildhost$ make install

This would produce the host and remote core binaries in an ‘install’ subdirectory. Tip: Alternatively, for convenience, you can also extract and rebuild all examples available for your platform at once with this series of commands:

buildhost$ cd <IPC_INSTALL_DIR>/examples

buildhost$ make extract

buildhost$ make

buildhost$ make install

Next step is to copy the content of the ‘install’ subdirectory into a location accessible by your target board (e.g. SD card). Run the example on the target using IPC by loading the remote cores like you would with the test applications, then run the example. E.g.:

target# ipc IPU ex02_messageq/debug/server_ipu.xem4 DSP ex02_messageq/debug/server_dsp.xe64T

target# cd ex02_messageq/debug/

target# app_host IPU

4.4.2.3.4.6. Advanced topics¶

4.4.2.3.4.6.1. Load and unload individual cores while IPC is running (IPC 3.23.01 and above)¶

In some applications, there may be a need to load or unload cores after the IPC resource manager is already up and running – e.g. change the DSP executable while keeping the IPU running.

In order to load and start a core with an executable, you can do the following after having launched the resource manager:

target# echo <slave executable file path> > /dev/ipc-file/<core name>

target# echo 1 > /dev/ipc-state/<core name>

The first command sets the filename of an executable to be loaded, and the second command loads and starts the core with that executable.

To stop and unload a core, use the following command:

target# echo 0 > /dev/ipc-state/<core name>

Keep in mind that this simply puts the core into reset. If there is any on-going communication between the given core and the others, it is the responsibility of the user application to clean up and terminate IPC on the slave before unloading a core, thus to avoid causing any memory leaks or communication errors.

4.4.2.3.4.6.2. Inspect the state of a slave core (IPC 3.23.01 and above)¶

To find out the state of a slave core (whether it is running or in reset), issue the following command:

target# cat /dev/ipc-state/<core name>

4.4.2.3.4.6.3. Tracing¶

When an issue arises, sometimes it is useful to see the output of internal traces from IPC. This section talks about how to view IPC trace from both the host and the slave cores on the QNX command prompt.

Host-side trace output

Trace from IPC user libraries (IPC 3.35 and above)

Trace output from the IPC user libraries is controlled using the environment variable IPC_DEBUG, when launching an application that uses IPC. E.g.:

target# IPC_DEBUG=<level> app_host

where <level> can be set to a value between 1 and 3, with 3 being the most verbose.

Trace from IPC resource manager (IPC 3.35 and above)

To show the trace output of the IPC resource manager in the QNX system log, run the following command:

target# sloginfo -m42

The verbosity of the trace can be controlled using the environment variable IPC_DEBUG_SLOG_LEVEL when launching the IPC resource manager. E.g.:

target# IPC_DEBUG_SLOG_LEVEL=<level> ipc DSP1 ex02_messageq/debug/server_dsp1.xe66

where <level> can be set to a value between 0 and 7, with 7 being the most verbose. The default level is 2.

Slave-side trace output

To show all trace output (including IPC’s) on a given slave core, simply run the following

target# cat /dev/ipc-trace/<core name>

where <core name> corresponds to the name of the slave core which trace output you are interested in (e.g. DSP1, IPU1 or IPU2 for DRA7xx)

Note that older versions of IPC may use a slightly different path that is based on the MultiProc id of the core of interest: /dev/ipc-trace<id>.

4.4.2.3.4.6.4. Building the IPC resource manager in debug mode (IPC 3.35 and above)¶

When debugging an issue, the user may wish to have the ability to step through the source code in the IPC resource manager. For this to happen, the IPC resource manager needs to be built in debug mode with debug symbols. Adding IPC_DEBUG=1 to the file <IPC_INSTALL_DIR>/qnx/Makefile and rebuilding IPC would do the trick:

ipc3x_dev: utils

@cd src/ipc3x_dev; \

make IPC_PLATFORM=$(IPC_PLATFORM) SMP=1 QNX_CFLAGS=$(QNX_CFLAGS) IPC_DEBUG=1

target# make -f ipc-qnx.mak clean

target# make -f ipc-qnx.mak all

4.4.2.3.5. See Also¶

4.4.3. Porting IPC¶

4.4.3.1. Interfaces to Implement¶

When porting IPC to new devices, you may need to create custom implementations of the following interfaces. You may find that the provided implementations of these interfaces meet your needs, so don’t assume that you will need to create custom implementation in all cases.

- “IInterrupt”? for use by Notify. The interface definition is in ti.sdo.ipc.notifyDrivers.IInterrupt.

- “IGateMPSupport”? for use by GateMP. The interface definition is in ti.sdo.ipc.interfaces.IGateMPSupport.

- “IMessageQTransport”? and “ITransportSetup”? for use by MessageQ. Interface definitions are in ti.sdo.ipc.interfaces.IMessageQTransport and ti.sdo.ipc.interfaces.ITransportSetup.

- “INotifyDriver”? for use by Notify. The interface definition is in ti.sdo.ipc.interfaces.INotifyDriver.

- “INotifySetup”? module, which defines interrupt mappings, for use by Notify. The interface definition is in ti.sdo.ipc.interfaces.INotifySetup.

For details about the interfaces, see the IPC online documentation.

4.4.3.2. Other Porting Tasks¶

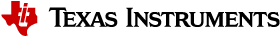

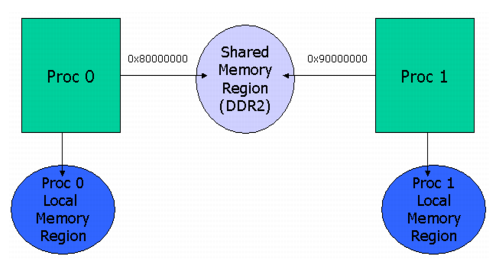

You will likely need to specify custom shared region(s) in your configuration file. For details, see SharedRegion Module.

Optionally, you may implement custom Heaps and hardware-specific versions of other IPC modules.

4.4.4. Optimizing IPC Applications¶

4.4.4.1. Compiler and Linker Optimization¶

You can optimize your application for better performance and code size or to give you more debugging information by selecting different ways of compiling and linking your application. For example, you can do this by linking with versions of the SYS/BIOS and IPC libraries that were compiled differently.

The choices you can make related to compiler and linker optimization are located in the following places:

- RTSC Build-Profile. You see this field when you are creating a new CCS project or modifying the CCS Build settings. We recommend that you use the “release” setting. The “release” option is preferred even when you are creating and debugging an application; the “debug” option is mainly intended for internal use by Texas Instruments. The “release” option results in a somewhat smaller executable that can still be debugged. This build profile primarily affects how Codec Engine and some device drivers are built.

Note

The “whole_program” and “whole_program_debug” options for the RTSC Build-Profile have been deprecated, and are no longer recommended. The option that provides the most similar result is to set the BIOS.libType configuration property to BIOS.LibType_Custom.

- CCS Build Configuration. This setting in the CCS Build settings allows you to choose between and customize multiple build configurations. Each configuration can have the compiler and linker settings you choose.

- BIOS.libType configuration property. You can set this property in XGCONF or by editing the .cfg file in your project. This property lets you select from two pre-compiled versions of the SYS/BIOS and IPC libraries or to have a custom version of the SYS/BIOS and IPC libraries compiled based on the needs of your application. See the table and discussion that follow for more information.

The options for the BIOS.libType configuration property are as follows:

| BIOS.libTyp e | Compile Time | Logging | Code Size | Run-Time Performance |

|---|---|---|---|---|

| Instrumente d (BIOS.LibTy pe_Instrume nted) | Fast | On | Good | Good |

| Non-Instrum ented (BIOS.LibTy pe_NonInstr umented) | Fast | Off | Better | Better |

| Custom (BIOS.LibTy pe_Custom) | Fast (slow first time) | As configured | Best | Best |

| Debug (BIOS.LibTy pe_Debug) | Slower | As configured |

Instrumented. (default) This option links with pre-built SYS/BIOS (and IPC) libraries that have instrumentation available. All Asserts and Diags settings are checked. Your configuration file can enable or disable various Diags and logging related settings. However, note that the checks to see if Diags are enabled before outputting a Log event are always performed, which has an impact on performance even if you use the ALWAYS_ON or ALWAYS_OFF setting. The resulting code size when using this option may be too large to fit on some targets, such as C28x and MSP430. This option is easy to use and debug and provides a fast build time.

Non-Instrumented. This option links with pre-built SYS/BIOS (and IPC) libraries that have instrumentation turned off. No Assert or Diag settings are checked, and logging information is not available at run-time. The checking for Asserts and Diags is compiled out of the libraries, so run-time performance and code size are optimized. Checking of Error_Blocks and handling errors in ways other than logging an event are still supported. This option is easy to use and provides a fast build time.

Custom. This option builds custom versions of the SYS/BIOS (and IPC) libraries that contain the modules and APIs that your application needs to access. If you have not used a particular module in your .cfg file or your C code (and it is not required internally by a SYS/BIOS module that is used), that module is not contained in the custom libraries compiled for your application. This option provides the best run-time performance and best code size given the needs of your application. Instrumentation is available to whatever extent your application configures it.

The first time you build a project with the custom libType, the build will be longer. The custom libraries are stored in the “src” directory of your project. Subsequent builds may be faster; libraries do not need to be rebuilt unless you change one of the few configuration properties that affect the build settings, or you use an additional module that wasn’t already used in the previous configuration.:

Note

If you disable SYS/BIOS Task or Swi scheduling, you must use the “custom” option in order to successfully link your application.

The custom option uses program optimization that removes many initialized constants and small code fragments (often “glue” code) from the final executable image. Such classic optimizations as constant folding and function inlining are used, including across module boundaries. The custom build preserves enough debug information to make it still possible to step through the optimized code in CCS and locate global variables.:

- Debug. This option is not recommended; it is intended for internal use by Texas Instruments developers.

The following example statements set the BIOS.libType configuration property:

var BIOS = xdc.useModule('ti.sysbios.BIOS');

BIOS.libType = BIOS.LibType_Custom;

If you use the custom option for the BIOS.libType, you can also set the BIOS.customCCOpts property to customize the C compiler command-line options used when compiling the SYS/BIOS libraries. If you want to change this property, it is important to first examine and understand the default command-line options used to compile the SYS/BIOS libraries for your target. You can see the default in XGCONF or by placing the following statement in your configuration script and building the project:

print("customCCOpts =", BIOS.customCCOpts);

Be careful not to cause problems for the SYS/BIOS compilation when you modify this property. For example, the –program_level_compile option is required. (Some –define and –include_path options are used on the compiler command line but are not listed in the customCCOpts definition; these also cannot be removed.) For example, to create a debuggable custom library, you can remove the -o3 option from the BIOS.customCCOpts definition by specifying it with the following string for a C64x+ target:

BIOS.customCCOpts = "-mv64p --abi=eabi -q -mi10 -mo -pdr -pden -pds=238 -pds=880

-pds1110 --embed_inline_assembly --program_level_compile -g";

4.4.4.2. Optimizing Runtime Performance¶

You can use one or more of the following techniques to improve the runtime performance of IPC applications:

- After you have finished debugging an application, you can disable asserts and logging with the following configuration statements:

var Diags = xdc.useModule("xdc.runtime.Diags");

var Defaults = xdc.useModule('xdc.runtime.Defaults');

Defaults.common$.diags_ASSERT = Diags.ALWAYS_OFF;

Defaults.common$.logger = null;

- If shared memory has the same address on all processors, you can use the following configuration statement to set the SharedRegion.translate property to false. See SharedRegion Module for more about SharedRegion configuration.

SharedRegion.translate = false;

- Ensure that code, data, and shared data are all placed in cacheable memory. Refer to the SYS/BIOS documentation for information on how to configure a cache. See the TI SYS/BIOS Real-time Operating System v6.x User’s Guide (SPRUEX3) for details.

- You can reduce contention between multiple processors and multiple threads by creating a new gate for use by a new IPC module instance. Leaving the params.gate property set to NULL causes the default system GateMP instance to be used for context protection. However, in some cases it may be optimal to create a new GateMP instance and supply it to the instance creation. See GateMP Module for more information. For example:

GateMP_Params gateParams;

GateMP_Handle gateHandle;

HeapBufMP_Params heapParams;

GateMP_Params_init(&gateParams);

gateHandle = GateMP_create(&gateParams);

HeapBufMP_Params_init(&heapParams);

heapParams.gate = gateHandle;

If a unicache is shared between two cores in shared memory and you expect to share certain IPC instances (such as a GateMP or ListMP) solely between those two cores, you may be able to improve performance by creating a SharedRegion with cache disabled for use between those two cores only. Since region 0 needs to be accessible by all cores on a system, region 1 can be created with a cache line size of 0 and a cacheEnable configuration of FALSE. Any IPC instance created within a SharedRegion inherits the cache settings (the cacheEnabled flag and the cacheLineSize) from this region. Therefore, unnecessary cache operations can be avoided by creating an instance in region 1.

The following configuration statements create a SharedRegion with the cache disabled (on OMAP4430):

SharedRegion.setEntryMeta(1, /* Create shared region 1 */

{ base: 0x86000000,

len: 0x10000,

ownerProcId: 0,

isValid: true,

cacheEnabled: false, /* Cache operations unneeded */

cacheLineSize: 0, /* Cache padding unneeded */

name: "DDR2",

});

The following C code creates a HeapBufMP instance in this

SharedRegion::

HeapBufMP_Params heapParams;

HeapBufMP_Handle heapHandle;

HeapBufMP_Params_init(&heapParams);

heapParams.regionId = 1;

heapHandle = HeapBufMP_create(&heapParams);

This heap can be used by either of the Cortex M3 cores on an

OMAP4430, because they both share a unicache. Do not use this heap

(or anything else belonging to a SharedRegion with caching disabled)

from any other processor if the shared memory belonging to the

SharedRegion is cacheable.

4.4.4.3. Optimizing Notify and MessageQ Latency¶

By default, IPC applications are configured to use the ti.sdo.ipc.notifyDrivers.NotifyDriverShm Notify driver and the ti.sdo.ipc.transports.TransportShm MessageQ transport. These modules are used by default because they offer backward compatibility with older IPC/SysLink releases. In addition, these modules may offer functionality not supported by their newer, lower-latency counterparts.

If your application does not need functionality provided only by the default Notify drivers or MessageQ transport, you can reduce the latency by switching to alternative MessageQ transports and/or Notify drivers.

4.4.4.4. Choosing and Configuring Notify Drivers¶

To switch to a different Notify driver, set the Notify.SetupProxy configuration to the family-specific Notify setup module. For example, the following statements configure an application on the DM6446 to use the NotifyDriverCirc driver for that device:

var Notify = xdc.useModule('ti.sdo.ipc.Notify');

Notify.SetupProxy = xdc.useModule('ti.sdo.ipc.family.dm6446.NotifyCircSetup');

IPC provides the following Notify drivers. Each has a corresponding setup module that should be used as the Notify.SetupProxy module.

| Modules and Description | Supports Disabling and Enabling Events | Latency |

|---|---|---|

ti.sdo.ipc.notifyDrivers.NotifyDriverShm ti.sdo.ipc.family.<family>.NotifySetup This shared-memory Notify driver offers room for a single pending notification in shared memory per event. |

Yes | Default |

ti.sdo.ipc.notifyDrivers.NotifyDriverCirc ti.sdo.ipc.family.<family>.NotifyCircSetup This shared-memory Notify driver uses a circular buffer to store notifications. Unlike NotifyDriverShm, this driver stores all notifications in the same circular buffer (whose size is configurable). |

No | Better than NotifyDriverShm |

ti.sdo.ipc.family.ti8 1xx.NotifyDriverM bx ti.sdo.ipc.family.ti8 1xx.NotifyMbxSetup This TI81xx-only Notify driver uses the hardware mailbox. This driver is not usable by other devices. Notifications are stored in hardware mailbox queues present on TI81xx devices. |

No | Better than NotifyDriverCirc and NotifyDriverShm |

4.4.4.5. Choosing and Configuring MessageQ Transports¶

Similarly, to use an alternative MessageQ transport, configure the MessageQ.SetupTransportProxy property to use the transport’s corresponding Transport Setup proxy. For example, to use the TransportShmNotify module, use the following configuration:

var MessageQ = xdc.module('ti.sdo.ipc.MessageQ');

MessageQ.SetupTransportProxy =

xdc.module('ti.sdo.ipc.transports.TransportShmNotifySetup');

Unlike the Notify setup modules, Transport setup modules are generally not family-specific; most are located in the ti.sdo.ipc.transports package. IPC provides the following transports. Each has a corresponding setup module for use as the MessageQ.SetupTransportProxy module.

| Modules and Description | Transport Speed |

|---|---|

ti.sdo.ipc.transports.Transpo rtShm ti.sdo.ipc.transports.TransportSh mSetup This shared-memory MessageQ transport uses ListMP to temporarily queue messages in shared memory before the messages are moved to the destination queue. This transport is typically slowest because of the overhead of queuing messages using a linked list. This is the default MessageQ transport. |

Slowest |

ti.sdo.ipc.transports.Transpo rtShmCirc ti.sdo.ipc.transports.TransportSh mCircSetup This shared-memory MessageQ transport uses a fixed-length circular buffer to temporarily queue messages in shared memory before the messages are moved to the destination queue. This transport is typically faster than TransportShm because of the efficiencies gained by using a circular buffer instead of a linked list. |

Medium |

ti.sdo.ipc.transports.Transpo rtShmNotify ti.sdo.ipc.transports.TransportSh mNotifySetup This shared-memory MessageQ transport does no buffering before the messages are moved to the destination queue. Because of the lack of buffering, this transport tends to offer lower MessageQ latency than either TransportShm or TransportShm. However, If messages aren’t received quickly enough by the receiver, the sender may spin while waiting for the receiver to move the message to its local queue. |

Fastest, but depends on fast processing of messages by receiver |

4.4.4.7. Optimizing Local Memory Usage¶

If the Custom1 and Custom2 GateMP proxies will never be used, make sure they are both plugged with the ti.sdo.ipc.gates.GateMPSupportNull GateMP delegate. By default, GateMP plugs the Custom1 proxy with the GatePeterson delegate. A considerable amount of local memory is reserved for use by GatePeterson. You can plug the Custom1 proxy with the GateMPSupportNull delegate by adding the following configuration statements to your application:

var GateMP = xdc.useModule('ti.sdo.ipc.GateMP');

GateMP.RemoteCustom1Proxy = xdc.useModule('ti.sdo.ipc.gates.GateMPSupportNull');

4.4.4.8. Optimizing Code Size¶

This section provides tips and suggestions for minimizing the code size of a SYS/BIOS-based application that uses IPC.

- For a number of ways to configure SYS/BIOS that reduce code size by using custom built SYS/BIOS libraries and by disabling various features, see Section E.3 of the TI SYS/BIOS Real-time Operating System v6.x User’s Guide (SPRUEX3). In particular, after you have debugged your code, disabling Asserts as follows helps reduce the size of your code.

- ::

- var Defaults = xdc.useModule(‘xdc.runtime.Defaults’); var Diags = xdc.useModule(‘xdc.runtimg.Diags’); Defaults.common$.diags_ASSERT = Diags.ALWAYS_OFF;

- The NotifyDriverCirc notification driver and the TransportShmNotify or TransportShmCirc MessageQ transports described in Optimizing IPC Applications use less code space than the default Notify driver and MessageQ transport.

- You can reduce code size by not using the HeapBufMP Heap implementation. Since IPC uses the HeapMemMP implementation internally, using HeapMemMP in your application does not increase the code size. However, you should be aware that, depending on how your application uses heaps, HeapMemMP may lead to problems with heap fragmentation. See Heap*MP Modules for more about Heap implementations.

4.4.5. Rebuilding IPC¶

This page describes how to rebuild the IPC source code.

The IPC product includes source files and build scripts that allow you to modify the IPC sources and rebuild its libraries. You can do this in order to modify, update, or add functionality. If you edit the IPC source code and/or corresponding build scripts, you must also rebuild IPC in order to create new libraries containing these modifications.

Note that you can cause the BIOS-side IPC (and BIOS) libraries to be rebuilt as part of the application build - this is called a ‘Custom Build’. The custom-built libraries will be stored with other output from executing your config script, and will contain only modules and APIs that your application needs to access. You can cause such a Custom Build to occur using the BIOS.libType config param as follows.

var BIOS = xdc.useModule('ti.sysbios.BIOS');

BIOS.libType = BIOS.LibType_Custom;

Note

This page provides details about rebuilding the IPC source code. We strongly recommend that you copy the IPC installation to a directory with a different name and rebuild that copy, rather than rebuilding the original installation.

4.4.5.1. Build Procedure¶

The various IPC Install Guides describe the mechanics of rebuilding IPC libraries. Please consult the Install Guide appropriate for your environment.

- IPC Install Guide BIOS - for all-BIOS environments

- IPC Install Guide Linux - for environments with a combination of Linux and BIOS

- IPC Install Guide QNX - for environments with a combination of QNX and BIOS

4.4.5.2. Pointing a CCS Project at a Rebuilt IPC¶

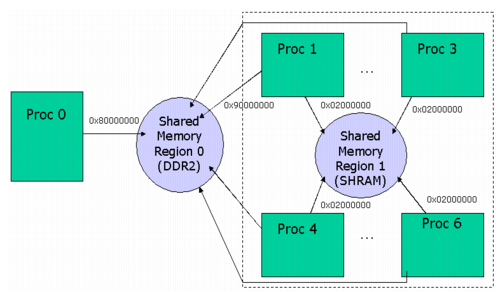

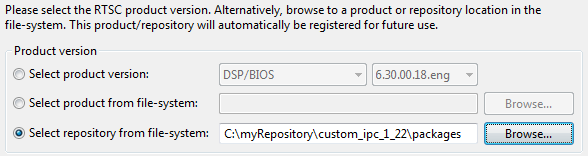

To build your application using the version of IPC you have rebuilt, you must point your project to this rebuilt version by following these steps:

Open CCS and select the application project you want to rebuild.

Right-click on your project and choose Build Properties. If you have a configuration project that is separate from your application project, open the build properties for the configuration project.

In the CCS Build category of the Properties dialog, choose the RTSC tab.

Under the Products and Repositories tab, uncheck all the boxes for IPC. This ensures that no version is selected.

Click the Add button next to the Products and Repositories tab.

Choose Select repository from file-system, and browse to the “packages” directory of the location where you copied and rebuilt IPC. For example, the location may be C:myIpcBuildscustom_ipc_1_22_##-##packages.

Click OK to apply these changes to the project.

You may now rebuild your project using the re-built version of IPC.

4.4.6. TI SDO IPC Package¶

4.4.6.1. Introduction¶

This page introduces the modules in the ti.sdo.ipc package.

Note

This package is not used on HLOS-based cores. Although this is a BIOS-only package, note that the BIOS-side of a HLOS<->BIOS IPC-using application will need to bring in a subset of these packages into the BIOS-side configuration scripts.

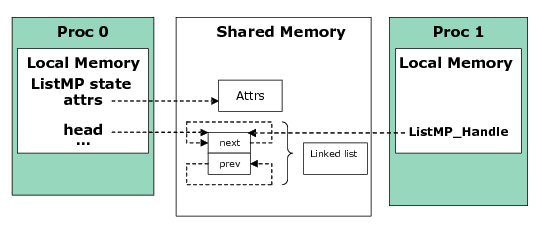

The ti.sdo.ipc package contains the following modules that you may use in your applications:

Module Module Path Description GateMP Module GateMP Manages gates for mutual exclusion of shared resources by multiple processors and threads. See GateMP Module HeapBufMP Module ti.sdo.ipc.heaps.HeapBufMP Fixed-sized shared memory Heaps. Similar to SYS/BIOS’s ti.sysbios.heaps.HeapBuf module, but with some configuration differences. See HeapMP Module HeapMemMP Module ti.sdo.ipc.heaps.HeapMemMP Variable-sized shared memory Heaps. See HeapMP Module HeapMultiBufMP Module ti.sdo.ipc.heaps.HeapMultiBufMP Multiple fixed-sized shared memory Heaps. See HeapMP Module Ipc Module ti.sdo.ipc.Ipc Provides Ipc_start() function and allows startup sequence configuration. See IPC Module ListMP Module ti.sdo.ipc.ListMP Doubly-linked list for shared-memory, multi-processor applications. Very similar to the ti.sdo.utils.List module. See ListMP Module MessageQ Module ti.sdo.ipc.MessageQ Variable size messaging module. See MessageQ Module TransportShm ti.sdo.ipc.transports.TransportShm Transport used by MessageQ for remote communication with other processors via shared memory. See MessageQ Module Notify Module ti.sdo.ipc.Notify Low-level interrupt mux/demuxer module. See Notify Module NotifyDriverShm ti.sdo.ipc.notifyDrivers. NotifyDriverShm Shared memory notification driver used by the Notify module to communicate between a pair of processors. See Notify Module SharedRegion Module ti.sdo.ipc.SharedRegion Maintains shared memory for multiple shared regions. See SharedRegion Module

Additional modules in the subfolders of the ti.sdo.ipc package contain specific implementations of gates, heaps, notify drivers, transports, and various device family-specific modules.

In addition, the ti.sdo.ipc package defines the following interfaces that you may implement as your own custom modules:

Module Module Path IGateMPSupport ti.sdo.ipc.interfaces.IGateMPSupport IInterrupt ti.sdo.ipc.notifyDrivers.IInterrupt IMessageQTransport ti.sdo.ipc.interfaces.IMessageQTransport INotifyDriver ti.sdo.ipc.interfaces.INotifyDriver INotifySetup ti.sdo.ipc.interfaces.INotifySetup

The <ipc_install_dir>/packages/ti/sdo/ipc directory contains the following packages that you may need to know about:

- examples. Contains examples.

- family. Contains device-specific support modules (used internally).

- gates. Contains GateMP implementations (used internally).

- heaps. Contains multiprocessor heaps.

- interfaces. Contains interfaces.

- notifyDrivers. Contains NotifyDriver implementations (used internally).

- transports. Contains MessageQ transport implementations that are used internally.

4.4.6.1.1. Including Header Files¶

BIOS applications that use modules in the ti.sdo.ipc or ti.sdo.utils

package should include the common header files provided in

<ipc_install_dir>/packages/ti/ipc/. These header files offer a

common API for both SYS/BIOS and HLOS users of IPC.

The following example C code includes header files applications may need to use. Depending on the APIs used in your application code, you may need to include different XDC, IPC, and SYS/BIOS header files.

#include <xdc/std.h>

#include <string.h>

/* ---- XDC.RUNTIME module Headers */

#include <xdc/runtime/Memory.h>

#include <xdc/runtime/System.h>

#include <xdc/runtime/IHeap.h>

/* ----- IPC module Headers */

#include <ti/ipc/GateMP.h>

#include <ti/ipc/Ipc.h>

#include <ti/ipc/MessageQ.h>

#include <ti/ipc/HeapBufMP.h>

#include <ti/ipc/MultiProc.h>

/* ---- BIOS6 module Headers */

#include <ti/sysbios/BIOS.h>

#include <ti/sysbios/knl/Task.h>

/* ---- Get globals from .cfg Header */

#include <xdc/cfg/global.h>

Note that the appropriate include file location has changed from

previous versions of IPC. The XDCtools-generated header files are still

available in <ipc_install_dir>/packages/ti/sdo/ipc/, but these

should not directly be included in runtime .c code.

You should search your applications for “ti/sdo/ipc” and “ti/sdo/utils”

and change the header file references found as needed. Additional

changes to API calls will be needed.

Documentation for all common-header APIs is provided in Doxygen format

in your IPC installation at

Documentation for all common-header APIs is provided in Doxygen format

in your IPC installation at

<ipc_install_dir>/docs/doxygen/html/index.html. The latest version

of that documentation is available

online.

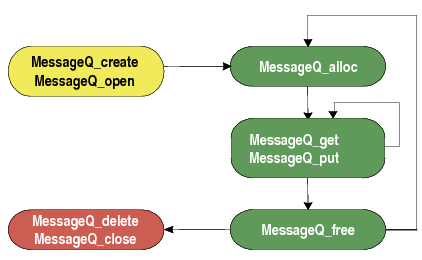

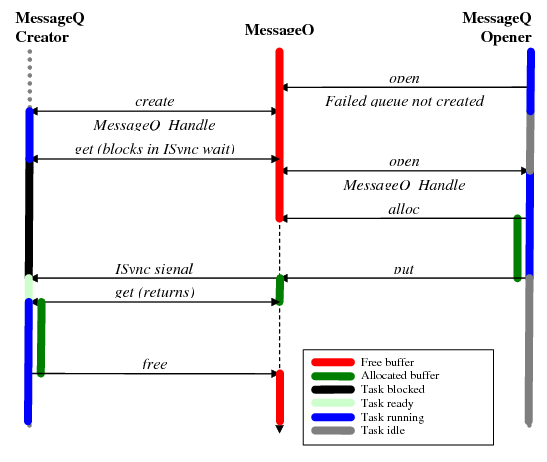

4.4.6.1.2. Standard IPC Function Call Sequence¶

For instance-based modules in IPC, the standard IPC methodology when creating object dynamically (that is, in C code) is to have the creator thread first initialize a MODULE_Params structure to its default values via a MODULE_Params_init() function. The creator thread can then set individual parameter fields in this structure as needed. After setting up the MODULE_Params structure, the creator thread calls the MODULE_create() function to creates the instance and initializes any shared memory used by the instance. If the instance is to be opened remotely, a unique name must be supplied in the parameters.

Other threads can access this instance via the MODULE_open() function, which returns a handle with access to the instance. The name that was used for instance creation must be used in the MODULE_open() function.

In most cases, MODULE_open() functions must be called in the context of a Task. This is because the thread running the MODULE_open() function needs to be able to block (to pend on a Semaphore in this case) while waiting for the remote processor to respond. The response from the remote processor triggers a hardware interrupt, which then posts a Semaphore to allow to Task to resume execution. The exception to this rule is that MODULE_open() functions do not need to be able to block when opening an instance on the local processor.

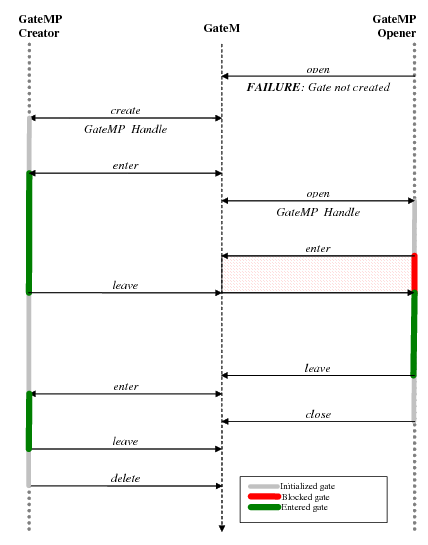

When the threads have finished using an instance, all threads that called MODULE_open() must call MODULE_close(). Then, the thread that called MODULE_create() can call MODULE_delete() to free the memory used by the instance.

Note that all threads that opened an instance must close that instance before the thread that created it can delete it. Also, a thread that calls MODULE_create() cannot call MODULE_close(). Likewise, a thread that calls MODULE_open() cannot call MODULE_delete().

4.4.6.1.3. Error Handling in IPC¶

Many of the APIs provided by IPC return an integer as a status code. Your application can test the status value returned against any of the provided status constants. For example:

MessageQ_Msg msg;

MessageQ_Handle messageQ;

Int status;

...

status = MessageQ_get(messageQ, &msg, MessageQ_FOREVER);

if (status < 0) {

System_abort("Should not happen\n");

}

Status constants have the following format: MODULE_[S|E]_CONDITION.

For example, Ipc_S_SUCCESS, MessageQ_E_FAIL, and SharedRegion_E_MEMORY

are status codes that may be returned by functions in the corresponding

modules.

Success codes always have values greater or equal to zero. For example,

Ipc_S_SUCCESS=0 and Ipc_S_ALREADYSETUP=1; both are success codes.

Failure codes always have values less than zero. Therefore, the presence

of an error can be detected by simply checking whether the return value

is negative.

Other APIs provided by IPC return a handle to a created object. If the handle is NULL, an error occurred when creating the object. For example:

messageQ = MessageQ_create(DSP_MESSAGEQNAME, NULL);

if (messageQ == NULL) {

System_abort("MessageQ_create failed\n");

}

Refer to the Doxygen documentation for status codes returned by IPC functions.

4.4.6.2. IPC Module¶

The main purpose of the Ipc module is to initialize the various subsystems of IPC. All applications that use IPC modules must call the Ipc_start() API, which does the following:

- Initializes a number of objects and modules used by IPC

- Synchronizes multiple processors so they can boot in any order

An application that uses IPC APIs–such as MessageQ–must include the Ipc module header file and call Ipc_start() before any calls to IPC modules. Here is a BIOS-side example:

#include <ti/ipc/Ipc.h>

int main(int argc, char* argv[])

{

Int status;

/* Call Ipc_start() */

status = Ipc_start();

if (status < 0) {

System_abort("Ipc_start failed\n");

}

BIOS_start();

return (0);

}

By default, the BIOS implementation of Ipc_start() internally calls Notify_start() if it has not already been called, then loops through the defined SharedRegions so that it can set up the HeapMemMP and GateMP instances used internally by the IPC modules. It also sets up MessageQ transports to remote processors.

The SharedRegion with an index of 0 (zero) is often used by BIOS-side IPC_start() to create resource management tables for internal use by other IPC modules. Thus SharedRegion “0” must be accessible by all processors. See SharedRegion Module for more about the SharedRegion module.

4.4.6.2.1. Ipc Module Configuration (BIOS-side only)¶

In an XDCtools configuration file, you configure the Ipc module for use as follows:

Ipc = xdc.useModule('ti.sdo.ipc.Ipc');

You can configure what the Ipc_start() API will do–which modules it will start and which objects it will create–by using the Ipc.setEntryMeta method in the configuration file to set the following properties:

- setupNotify. If set to false, the Notify module is not set up. The default is true.

- setupMessageQ. If set to false, the MessageQ transport instances to remote processors are not set up and the MessageQ module does not attach to remote processors. The default is true.

For example, the following statements from the notify example configuration turn off the setup of the MessageQ transports and connections to remote processors:

/* To avoid wasting shared memory for MessageQ transports */

for (var i = 0; i < MultiProc.numProcessors; i++) {

Ipc.setEntryMeta({

remoteProcId: i,

setupMessageQ: false,

});

}

You can configure how the IPC module synchronizes processors by configuring the Ipc.procSync property. For example:

Ipc.procSync = Ipc.ProcSync_ALL;

The options are:

Ipc.ProcSync_ALL. If you use this option, the Ipc_start() API automatically attaches to and synchronizes all remote processors. If you use this option, your application should never call Ipc_attach(). Use this option if all IPC processors on a device start up at the same time and connections should be established between every possible pair of processors.

Ipc.ProcSync_PAIR. (Default) If you use this option, you must explicitly call Ipc_attach() to attach to a specific remote processor.

If you use this option, Ipc_start() performs system-wide IPC initialization, but does not make connections to remote processors. Use this option if any or all of the following are true: - You need to control when synchronization with each remote processor occurs. - Useful work can be done while trying to synchronize with a remote processor by yielding a thread after each attempt to Ipc_attach() to the processor. - Connections to some remote processors are unnecessary and should be made selectively to save memory. - Ipc.ProcSync_NONE. If you use this option, Ipc_start() doesn’t synchronize any processors before setting up the objects needed by other modules.

Use this option with caution. It is intended for use in cases where the application performs its own synchronization and you want to avoid a potential deadlock situation with the IPC synchronization.

If you use the ProcSync_NONE option, Ipc_start() works exactly as it does with ProcSync_PAIR. : However, in this case, Ipc_attach() does not synchronize with the remote processor. As with other ProcSync options, Ipc_attach() still sets up access to GateMP, SharedRegion, Notify, NameServer, and MessageQ transports, so your application must still call Ipc_attach() for each remote processor that will be accessed. Note that an Ipc_attach() call for a remote processor whose ID is less than the local processor’s ID must occur after the corresponding remote processor has called Ipc_attach() to the local processor. For example, processor #2 can call Ipc_attach(1) only after processor #1 has called Ipc_attach(2).: