|

|

Hardware Abstraction Layer for PC-DM648 PCI interface. Defines interfaces to initialize the PCI interface.

============================================================================

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

* Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

* Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

* Neither the name of Texas Instruments Incorporated nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. ============================================================================

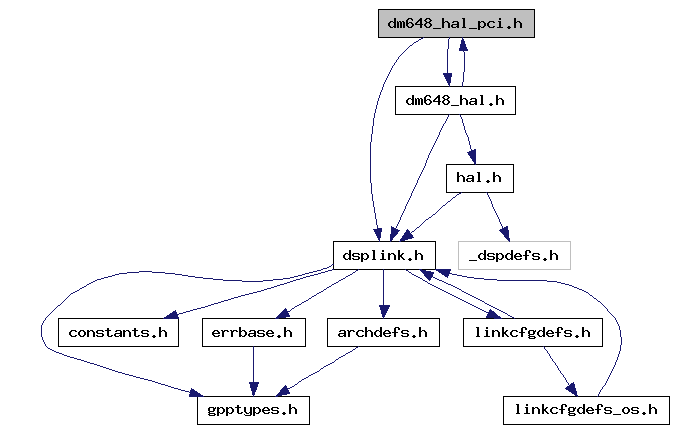

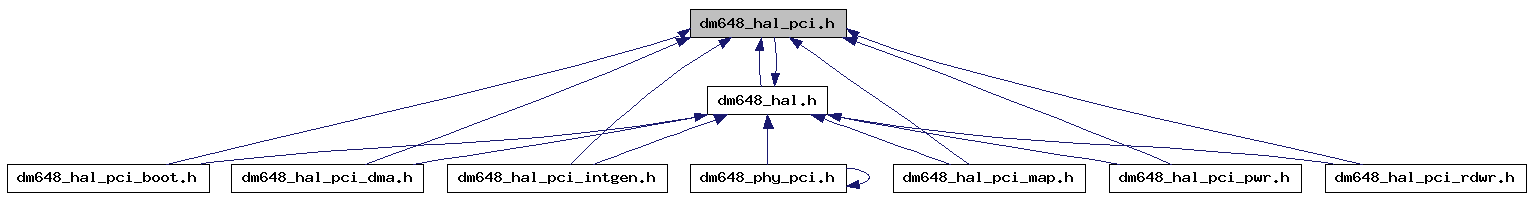

#include <dsplink.h>#include <dm648_hal.h>

Go to the source code of this file.

Data Structures | |

| struct | DM648_devRegs_tag |

| struct | DM648_ddrRegs |

| struct | DM648_paramEntry_tags |

| struct | DM648_edmaRegs_tag |

| struct | DM648_pciRegs_tag |

| struct | DM648_HalPciPhyObj_tag |

Defines | |

| #define | NUM_BARS 6 |

| Number of BAR registers. ============================================================================. | |

| #define | PCI33_DMA_MAXTHROUGHPUT 132u |

| Maximum through put of PCI interface. ============================================================================. | |

| #define | SCRATCH_BAR_NUMBER 0 |

| BAR number for scratch. ============================================================================. | |

| #define | DDR_REGS_BAR_NO 1u |

| Number for the BAR register used for DDR EMIF register access. ============================================================================. | |

| #define | CFG_REGS_BAR_NO 2u |

| Number for the BAR register used for register access. ============================================================================. | |

| #define | RWMEM_BAR_NO 4u |

| Number for the BAR register used for L1DRAM access. ============================================================================. | |

| #define | SHMEM_BAR_NO 5u |

| Number for the BAR register used for shared memory access. ============================================================================. | |

| #define | LPSC_GEM 33u |

| Module number for GEM. ============================================================================. | |

| #define | LPSC_EDMA_TPCC 0u |

| Module number for EDMA TPCC. ============================================================================. | |

| #define | LPSC_DDR 7u |

| Module number for DDR. ============================================================================. | |

| #define | DM648_BAR2_BASE 0x02000000u |

| Default value contained in BAR2. ============================================================================. | |

| #define | DM648_PCIMEM_BASE 0x40000000u |

| PCI memory base in GEM memory space. ============================================================================. | |

| #define | DM648_DEVREG_BASE 0x02049000u |

| Base address of Device config registers. ============================================================================. | |

| #define | DM648_EDMAREG_BASE 0x02A00000u |

| Base address of EDMA registers. ============================================================================. | |

| #define | DM648_DDRREG_BASE 0x78000000u |

| Base address of DDR PHY registers. ============================================================================. | |

| #define | DM648_MDCTL_BASE 0x02046A00 |

| Base address of MDCTL registers. ============================================================================. | |

| #define | DM648_MDSTAT_BASE 0x02046800 |

| Base address of MDSTAT registers. ============================================================================. | |

| #define | DM648_PTCMD_BASE 0x02046120 |

| Base address of MDCTL register. ============================================================================. | |

| #define | DM648_PTSTAT_BASE 0x02046128 |

| Base address of MDCTL registers. ============================================================================. | |

| #define | DM648_PCIREG_BASE 0x02048400u |

| Base address of PCI backend registers. ============================================================================. | |

| #define | DM648_SOFTINT0_MASK 0x01000000u |

| Mask for generating soft int0 (DSP->GPP) ============================================================================. | |

| #define | DM648_SOFTINT1_MASK 0x02000000 |

| Mask for generating soft int1 (GPP->DSP) ============================================================================. | |

| #define | DM648_LRESET_MASK 0x00000100u |

| Mask for reseting/releasing GEM. ============================================================================. | |

| #define | DM648_INTSTATUS_MASK 0x00080000u |

| Bitmask for Interrupt status (DSP->GPP) ============================================================================. | |

| #define | DM648_BOOTCMPLTBC_MASK 0x00000001u |

| Bitmask for Setting BC bit in BOOTCOMPLT register. ============================================================================. | |

| #define | DM648_PCIADLEN 0x00800000u |

| Length each segment of addressable PCI Space.. ============================================================================. | |

| #define | DM648_PCIADWRBITMASK 0xFF800000u |

| Mask indicating writeable bits in PCI Address Window registers. ============================================================================. | |

| #define | DM648_PAGEWRBITMASK 0xFF800000 |

| Mask indicating writeable bits in PCI Base Address Mask Register5. ============================================================================. | |

| #define | HAL_CONFIGURE_MAP 0x1 |

| Value indicating mapping has to be done. ============================================================================. | |

| #define | HAL_CONFIGURE_UNMAP 0x2 |

| Value indicating unmapping has to be done. ============================================================================. | |

| #define | HAL_CONFIGURE_SET 0x3 |

| Value indicating simply set the dsp for the given address. ============================================================================. | |

Typedefs | |

DM648_devRegs | |

Register Overlay Structure for Device config registers. ============================================================================ ============================================================================ | |

| typedef struct DM648_devRegs_tag | DM648_devRegs |

DM648_paramEntry | |

Register Overlay Structure for PARAMENTRY. ============================================================================ ============================================================================ | |

| typedef struct DM648_paramEntry_tags | DM648_paramEntry |

DM648_edmaRegs | |

Register Overlay Structure for EDMA. ============================================================================ ============================================================================ | |

| typedef struct DM648_edmaRegs_tag | DM648_edmaRegs |

DM648_pciRegs | |

PCI Back end register overlay structure. ============================================================================ ============================================================================ | |

| typedef struct DM648_pciRegs_tag | DM648_pciRegs |

| #define NUM_BARS 6 |

Number of BAR registers. ============================================================================.

============================================================================

| #define PCI33_DMA_MAXTHROUGHPUT 132u |

Maximum through put of PCI interface. ============================================================================.

============================================================================

| #define SCRATCH_BAR_NUMBER 0 |

BAR number for scratch. ============================================================================.

============================================================================

| #define DDR_REGS_BAR_NO 1u |

Number for the BAR register used for DDR EMIF register access. ============================================================================.

============================================================================

| #define CFG_REGS_BAR_NO 2u |

Number for the BAR register used for register access. ============================================================================.

============================================================================

| #define RWMEM_BAR_NO 4u |

Number for the BAR register used for L1DRAM access. ============================================================================.

============================================================================

| #define SHMEM_BAR_NO 5u |

Number for the BAR register used for shared memory access. ============================================================================.

============================================================================

| #define LPSC_GEM 33u |

Module number for GEM. ============================================================================.

============================================================================

| #define LPSC_EDMA_TPCC 0u |

Module number for EDMA TPCC. ============================================================================.

============================================================================

| #define LPSC_DDR 7u |

Module number for DDR. ============================================================================.

============================================================================

| #define DM648_BAR2_BASE 0x02000000u |

Default value contained in BAR2. ============================================================================.

============================================================================

| #define DM648_PCIMEM_BASE 0x40000000u |

PCI memory base in GEM memory space. ============================================================================.

============================================================================

| #define DM648_DEVREG_BASE 0x02049000u |

Base address of Device config registers. ============================================================================.

============================================================================

| #define DM648_EDMAREG_BASE 0x02A00000u |

Base address of EDMA registers. ============================================================================.

============================================================================

| #define DM648_DDRREG_BASE 0x78000000u |

Base address of DDR PHY registers. ============================================================================.

============================================================================

| #define DM648_MDCTL_BASE 0x02046A00 |

Base address of MDCTL registers. ============================================================================.

============================================================================

| #define DM648_MDSTAT_BASE 0x02046800 |

Base address of MDSTAT registers. ============================================================================.

============================================================================

| #define DM648_PTCMD_BASE 0x02046120 |

Base address of MDCTL register. ============================================================================.

============================================================================

| #define DM648_PTSTAT_BASE 0x02046128 |

Base address of MDCTL registers. ============================================================================.

============================================================================

| #define DM648_PCIREG_BASE 0x02048400u |

Base address of PCI backend registers. ============================================================================.

============================================================================

| #define DM648_SOFTINT0_MASK 0x01000000u |

Mask for generating soft int0 (DSP->GPP) ============================================================================.

============================================================================

| #define DM648_SOFTINT1_MASK 0x02000000 |

Mask for generating soft int1 (GPP->DSP) ============================================================================.

============================================================================

| #define DM648_LRESET_MASK 0x00000100u |

Mask for reseting/releasing GEM. ============================================================================.

============================================================================

| #define DM648_INTSTATUS_MASK 0x00080000u |

Bitmask for Interrupt status (DSP->GPP) ============================================================================.

============================================================================

| #define DM648_BOOTCMPLTBC_MASK 0x00000001u |

Bitmask for Setting BC bit in BOOTCOMPLT register. ============================================================================.

============================================================================

| #define DM648_PCIADLEN 0x00800000u |

Length each segment of addressable PCI Space.. ============================================================================.

============================================================================

| #define DM648_PCIADWRBITMASK 0xFF800000u |

Mask indicating writeable bits in PCI Address Window registers. ============================================================================.

============================================================================

| #define DM648_PAGEWRBITMASK 0xFF800000 |

Mask indicating writeable bits in PCI Base Address Mask Register5. ============================================================================.

============================================================================

| #define HAL_CONFIGURE_MAP 0x1 |

Value indicating mapping has to be done. ============================================================================.

============================================================================

| #define HAL_CONFIGURE_UNMAP 0x2 |

Value indicating unmapping has to be done. ============================================================================.

============================================================================

| #define HAL_CONFIGURE_SET 0x3 |

Value indicating simply set the dsp for the given address. ============================================================================.

============================================================================

| typedef struct DM648_devRegs_tag DM648_devRegs |

| typedef struct DM648_paramEntry_tags DM648_paramEntry |

| typedef struct DM648_edmaRegs_tag DM648_edmaRegs |

| typedef struct DM648_pciRegs_tag DM648_pciRegs |