|

|

UART driver implementation for a EUSCIA peripheral for MSP432.

============================================================================

This UART driver implementation is designed to operate on a EUSCI controller in UART mode for MSP432 devices.

The UART header file should be included in an application as follows:

Refer to UART.h for a complete description of APIs and example of use.

This header file contains port/pin macros for pin configuration. These macros are used to select the pins used for UART TX and RX in the UARTMSP432_HWAttrsV1 structure. The following is a description of the port/pin macro bit masks.

The port mapping controller on MSP432P401x MCUs allows reconfigurable mapping of digital functions on ports P2, P3, and P7. For these ports, the pin function value is encoded in bits 10-15 of the port/pin macro. This value ranges from 0 to 31. (You can find the port mapping definitions in the device data sheet.)

The pin ranges from 0 - 7 and is encoded in bits 0 - 3 (bit 3 is not actually used). Bits 4 - 7 of the port/pin macro are used to encode the port. For ports P2, P3, and P7, bits 8 and 9 are not used. The table below shows the bit mapping for P2, P3, and P7 port/pin macros.

| 15 - 10 | 9 | 8 | 7 - 4 | 3 - 0 |

|---|---|---|---|---|

| VALUE | X | X | PORT | PIN |

Some pins that are not on ports P2, P3, or P7, can be configured as UART TX or UART RX pins (e.g., P1.2 and P1.3). The macros for these pins will have 0 for bits 20 - 12. Bits 8 and 9 are used to hold the control bits, PnSEL1.x and PnSEL0.x, which determine the module function (PRIMARY, SECONDARY, or TERTIALRY). The table below shows the bit mapping for non port-mapped port/pin macros for pins that can be configured as UART TX or UART RX pins.

| 15 - 10 | 9 | 8 | 7 - 4 | 3 - 0 |

|---|---|---|---|---|

| X | PnSEL1.x | PnSEL0.x | PORT | PIN |

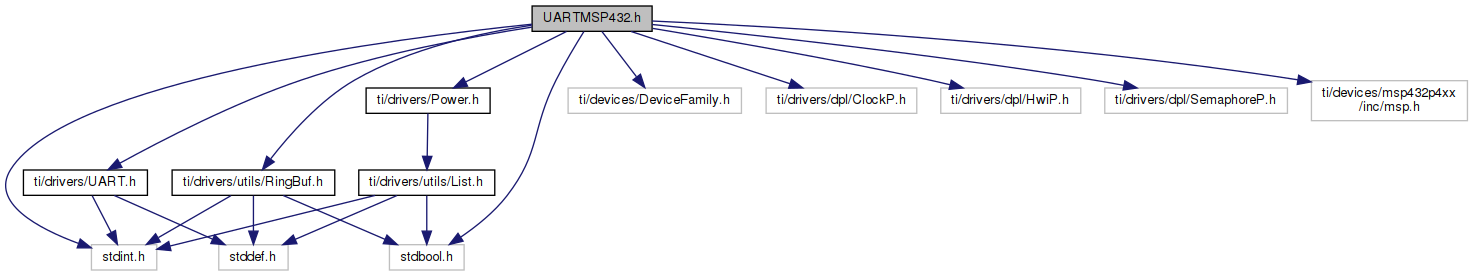

#include <stdint.h>#include <stdbool.h>#include <ti/devices/DeviceFamily.h>#include <ti/drivers/dpl/ClockP.h>#include <ti/drivers/dpl/HwiP.h>#include <ti/drivers/dpl/SemaphoreP.h>#include <ti/drivers/Power.h>#include <ti/drivers/UART.h>#include <ti/drivers/utils/RingBuf.h>#include <ti/devices/msp432p4xx/inc/msp.h>

Go to the source code of this file.

Data Structures | |

| struct | UARTMSP432_FxnSet |

| Complement set of read functions to be used by the UART ISR and UARTMSP432_read(). Internal use only. More... | |

| struct | UARTMSP432_BaudrateConfig |

| UARTMSP432 Baudrate configuration. More... | |

| struct | UARTMSP432_HWAttrsV1 |

| UARTMSP432 Hardware attributes. More... | |

| struct | UARTMSP432_Object |

| UARTMSP432 Object. More... | |

Macros | |

| #define | UARTMSP432_P1_2_UCA0RXD 0x00000112 /* Primary, port 1, pin 2 */ |

| #define | UARTMSP432_P1_3_UCA0TXD 0x00000113 /* Primary, port 1, pin 3 */ |

| #define | UARTMSP432_P2_0_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x20) |

| #define | UARTMSP432_P2_0_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x20) |

| #define | UARTMSP432_P2_0_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x20) |

| #define | UARTMSP432_P2_0_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x20) |

| #define | UARTMSP432_P2_0_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x20) |

| #define | UARTMSP432_P2_0_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x20) |

| #define | UARTMSP432_P2_1_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x21) |

| #define | UARTMSP432_P2_1_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x21) |

| #define | UARTMSP432_P2_1_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x21) |

| #define | UARTMSP432_P2_1_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x21) |

| #define | UARTMSP432_P2_1_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x21) |

| #define | UARTMSP432_P2_1_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x21) |

| #define | UARTMSP432_P2_2_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x22) |

| #define | UARTMSP432_P2_2_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x22) |

| #define | UARTMSP432_P2_2_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x22) |

| #define | UARTMSP432_P2_2_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x22) |

| #define | UARTMSP432_P2_2_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x22) |

| #define | UARTMSP432_P2_2_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x22) |

| #define | UARTMSP432_P2_3_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x23) |

| #define | UARTMSP432_P2_3_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x23) |

| #define | UARTMSP432_P2_3_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x23) |

| #define | UARTMSP432_P2_3_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x23) |

| #define | UARTMSP432_P2_3_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x23) |

| #define | UARTMSP432_P2_3_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x23) |

| #define | UARTMSP432_P2_4_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x24) |

| #define | UARTMSP432_P2_4_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x24) |

| #define | UARTMSP432_P2_4_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x24) |

| #define | UARTMSP432_P2_4_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x24) |

| #define | UARTMSP432_P2_4_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x24) |

| #define | UARTMSP432_P2_4_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x24) |

| #define | UARTMSP432_P2_5_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x25) |

| #define | UARTMSP432_P2_5_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x25) |

| #define | UARTMSP432_P2_5_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x25) |

| #define | UARTMSP432_P2_5_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x25) |

| #define | UARTMSP432_P2_5_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x25) |

| #define | UARTMSP432_P2_5_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x25) |

| #define | UARTMSP432_P2_6_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x26) |

| #define | UARTMSP432_P2_6_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x26) |

| #define | UARTMSP432_P2_6_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x26) |

| #define | UARTMSP432_P2_6_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x26) |

| #define | UARTMSP432_P2_6_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x26) |

| #define | UARTMSP432_P2_6_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x26) |

| #define | UARTMSP432_P2_7_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x27) |

| #define | UARTMSP432_P2_7_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x27) |

| #define | UARTMSP432_P2_7_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x27) |

| #define | UARTMSP432_P2_7_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x27) |

| #define | UARTMSP432_P2_7_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x27) |

| #define | UARTMSP432_P2_7_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x27) |

| #define | UARTMSP432_P3_0_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x30) |

| #define | UARTMSP432_P3_0_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x30) |

| #define | UARTMSP432_P3_0_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x30) |

| #define | UARTMSP432_P3_0_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x30) |

| #define | UARTMSP432_P3_0_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x30) |

| #define | UARTMSP432_P3_0_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x30) |

| #define | UARTMSP432_P3_1_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x31) |

| #define | UARTMSP432_P3_1_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x31) |

| #define | UARTMSP432_P3_1_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x31) |

| #define | UARTMSP432_P3_1_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x31) |

| #define | UARTMSP432_P3_1_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x31) |

| #define | UARTMSP432_P3_1_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x31) |

| #define | UARTMSP432_P3_2_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x32) |

| #define | UARTMSP432_P3_2_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x32) |

| #define | UARTMSP432_P3_2_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x32) |

| #define | UARTMSP432_P3_2_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x32) |

| #define | UARTMSP432_P3_2_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x32) |

| #define | UARTMSP432_P3_2_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x32) |

| #define | UARTMSP432_P3_3_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x33) |

| #define | UARTMSP432_P3_3_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x33) |

| #define | UARTMSP432_P3_3_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x33) |

| #define | UARTMSP432_P3_3_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x33) |

| #define | UARTMSP432_P3_3_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x33) |

| #define | UARTMSP432_P3_3_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x33) |

| #define | UARTMSP432_P3_4_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x34) |

| #define | UARTMSP432_P3_4_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x34) |

| #define | UARTMSP432_P3_4_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x34) |

| #define | UARTMSP432_P3_4_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x34) |

| #define | UARTMSP432_P3_4_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x34) |

| #define | UARTMSP432_P3_4_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x34) |

| #define | UARTMSP432_P3_5_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x35) |

| #define | UARTMSP432_P3_5_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x35) |

| #define | UARTMSP432_P3_5_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x35) |

| #define | UARTMSP432_P3_5_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x35) |

| #define | UARTMSP432_P3_5_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x35) |

| #define | UARTMSP432_P3_5_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x35) |

| #define | UARTMSP432_P3_6_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x36) |

| #define | UARTMSP432_P3_6_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x36) |

| #define | UARTMSP432_P3_6_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x36) |

| #define | UARTMSP432_P3_6_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x36) |

| #define | UARTMSP432_P3_6_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x36) |

| #define | UARTMSP432_P3_6_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x36) |

| #define | UARTMSP432_P3_7_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x37) |

| #define | UARTMSP432_P3_7_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x37) |

| #define | UARTMSP432_P3_7_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x37) |

| #define | UARTMSP432_P3_7_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x37) |

| #define | UARTMSP432_P3_7_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x37) |

| #define | UARTMSP432_P3_7_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x37) |

| #define | UARTMSP432_P7_0_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x70) |

| #define | UARTMSP432_P7_0_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x70) |

| #define | UARTMSP432_P7_0_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x70) |

| #define | UARTMSP432_P7_0_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x70) |

| #define | UARTMSP432_P7_0_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x70) |

| #define | UARTMSP432_P7_0_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x70) |

| #define | UARTMSP432_P7_1_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x71) |

| #define | UARTMSP432_P7_1_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x71) |

| #define | UARTMSP432_P7_1_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x71) |

| #define | UARTMSP432_P7_1_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x71) |

| #define | UARTMSP432_P7_1_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x71) |

| #define | UARTMSP432_P7_1_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x71) |

| #define | UARTMSP432_P7_2_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x72) |

| #define | UARTMSP432_P7_2_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x72) |

| #define | UARTMSP432_P7_2_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x72) |

| #define | UARTMSP432_P7_2_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x72) |

| #define | UARTMSP432_P7_2_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x72) |

| #define | UARTMSP432_P7_2_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x72) |

| #define | UARTMSP432_P7_3_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x73) |

| #define | UARTMSP432_P7_3_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x73) |

| #define | UARTMSP432_P7_3_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x73) |

| #define | UARTMSP432_P7_3_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x73) |

| #define | UARTMSP432_P7_3_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x73) |

| #define | UARTMSP432_P7_3_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x73) |

| #define | UARTMSP432_P7_4_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x74) |

| #define | UARTMSP432_P7_4_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x74) |

| #define | UARTMSP432_P7_4_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x74) |

| #define | UARTMSP432_P7_4_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x74) |

| #define | UARTMSP432_P7_4_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x74) |

| #define | UARTMSP432_P7_4_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x74) |

| #define | UARTMSP432_P7_5_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x75) |

| #define | UARTMSP432_P7_5_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x75) |

| #define | UARTMSP432_P7_5_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x75) |

| #define | UARTMSP432_P7_5_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x75) |

| #define | UARTMSP432_P7_5_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x75) |

| #define | UARTMSP432_P7_5_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x75) |

| #define | UARTMSP432_P7_6_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x76) |

| #define | UARTMSP432_P7_6_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x76) |

| #define | UARTMSP432_P7_6_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x76) |

| #define | UARTMSP432_P7_6_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x76) |

| #define | UARTMSP432_P7_6_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x76) |

| #define | UARTMSP432_P7_6_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x76) |

| #define | UARTMSP432_P7_7_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x77) |

| #define | UARTMSP432_P7_7_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x77) |

| #define | UARTMSP432_P7_7_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x77) |

| #define | UARTMSP432_P7_7_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x77) |

| #define | UARTMSP432_P7_7_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x77) |

| #define | UARTMSP432_P7_7_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x77) |

| #define | UARTMSP432_P9_6_UCA3RXD 0x00000196 /* Primary, port 9, pin 6 */ |

| #define | UARTMSP432_P9_7_UCA3TXD 0x00000197 /* Primeary, port 9, pin 7 */ |

Typedefs | |

| typedef void(* | UARTMSP432_ErrorCallback) (UART_Handle handle, uint32_t error) |

| The definition of an optional callback function used by the UART driver to notify the application when a receive error (FIFO overrun, parity error, etc) occurs. More... | |

| typedef struct UARTMSP432_Object * | UARTMSP432_Handle |

Variables | |

| const UART_FxnTable | UARTMSP432_fxnTable |

| #define UARTMSP432_P1_2_UCA0RXD 0x00000112 /* Primary, port 1, pin 2 */ |

| #define UARTMSP432_P1_3_UCA0TXD 0x00000113 /* Primary, port 1, pin 3 */ |

| #define UARTMSP432_P2_0_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x20) |

| #define UARTMSP432_P2_0_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x20) |

| #define UARTMSP432_P2_0_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x20) |

| #define UARTMSP432_P2_0_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x20) |

| #define UARTMSP432_P2_0_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x20) |

| #define UARTMSP432_P2_0_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x20) |

| #define UARTMSP432_P2_1_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x21) |

| #define UARTMSP432_P2_1_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x21) |

| #define UARTMSP432_P2_1_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x21) |

| #define UARTMSP432_P2_1_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x21) |

| #define UARTMSP432_P2_1_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x21) |

| #define UARTMSP432_P2_1_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x21) |

| #define UARTMSP432_P2_2_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x22) |

| #define UARTMSP432_P2_2_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x22) |

| #define UARTMSP432_P2_2_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x22) |

| #define UARTMSP432_P2_2_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x22) |

| #define UARTMSP432_P2_2_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x22) |

| #define UARTMSP432_P2_2_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x22) |

| #define UARTMSP432_P2_3_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x23) |

| #define UARTMSP432_P2_3_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x23) |

| #define UARTMSP432_P2_3_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x23) |

| #define UARTMSP432_P2_3_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x23) |

| #define UARTMSP432_P2_3_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x23) |

| #define UARTMSP432_P2_3_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x23) |

| #define UARTMSP432_P2_4_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x24) |

| #define UARTMSP432_P2_4_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x24) |

| #define UARTMSP432_P2_4_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x24) |

| #define UARTMSP432_P2_4_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x24) |

| #define UARTMSP432_P2_4_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x24) |

| #define UARTMSP432_P2_4_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x24) |

| #define UARTMSP432_P2_5_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x25) |

| #define UARTMSP432_P2_5_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x25) |

| #define UARTMSP432_P2_5_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x25) |

| #define UARTMSP432_P2_5_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x25) |

| #define UARTMSP432_P2_5_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x25) |

| #define UARTMSP432_P2_5_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x25) |

| #define UARTMSP432_P2_6_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x26) |

| #define UARTMSP432_P2_6_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x26) |

| #define UARTMSP432_P2_6_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x26) |

| #define UARTMSP432_P2_6_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x26) |

| #define UARTMSP432_P2_6_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x26) |

| #define UARTMSP432_P2_6_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x26) |

| #define UARTMSP432_P2_7_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x27) |

| #define UARTMSP432_P2_7_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x27) |

| #define UARTMSP432_P2_7_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x27) |

| #define UARTMSP432_P2_7_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x27) |

| #define UARTMSP432_P2_7_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x27) |

| #define UARTMSP432_P2_7_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x27) |

| #define UARTMSP432_P3_0_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x30) |

| #define UARTMSP432_P3_0_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x30) |

| #define UARTMSP432_P3_0_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x30) |

| #define UARTMSP432_P3_0_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x30) |

| #define UARTMSP432_P3_0_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x30) |

| #define UARTMSP432_P3_0_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x30) |

| #define UARTMSP432_P3_1_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x31) |

| #define UARTMSP432_P3_1_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x31) |

| #define UARTMSP432_P3_1_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x31) |

| #define UARTMSP432_P3_1_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x31) |

| #define UARTMSP432_P3_1_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x31) |

| #define UARTMSP432_P3_1_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x31) |

| #define UARTMSP432_P3_2_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x32) |

| #define UARTMSP432_P3_2_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x32) |

| #define UARTMSP432_P3_2_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x32) |

| #define UARTMSP432_P3_2_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x32) |

| #define UARTMSP432_P3_2_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x32) |

| #define UARTMSP432_P3_2_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x32) |

| #define UARTMSP432_P3_3_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x33) |

| #define UARTMSP432_P3_3_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x33) |

| #define UARTMSP432_P3_3_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x33) |

| #define UARTMSP432_P3_3_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x33) |

| #define UARTMSP432_P3_3_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x33) |

| #define UARTMSP432_P3_3_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x33) |

| #define UARTMSP432_P3_4_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x34) |

| #define UARTMSP432_P3_4_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x34) |

| #define UARTMSP432_P3_4_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x34) |

| #define UARTMSP432_P3_4_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x34) |

| #define UARTMSP432_P3_4_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x34) |

| #define UARTMSP432_P3_4_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x34) |

| #define UARTMSP432_P3_5_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x35) |

| #define UARTMSP432_P3_5_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x35) |

| #define UARTMSP432_P3_5_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x35) |

| #define UARTMSP432_P3_5_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x35) |

| #define UARTMSP432_P3_5_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x35) |

| #define UARTMSP432_P3_5_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x35) |

| #define UARTMSP432_P3_6_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x36) |

| #define UARTMSP432_P3_6_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x36) |

| #define UARTMSP432_P3_6_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x36) |

| #define UARTMSP432_P3_6_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x36) |

| #define UARTMSP432_P3_6_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x36) |

| #define UARTMSP432_P3_6_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x36) |

| #define UARTMSP432_P3_7_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x37) |

| #define UARTMSP432_P3_7_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x37) |

| #define UARTMSP432_P3_7_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x37) |

| #define UARTMSP432_P3_7_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x37) |

| #define UARTMSP432_P3_7_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x37) |

| #define UARTMSP432_P3_7_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x37) |

| #define UARTMSP432_P7_0_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x70) |

| #define UARTMSP432_P7_0_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x70) |

| #define UARTMSP432_P7_0_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x70) |

| #define UARTMSP432_P7_0_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x70) |

| #define UARTMSP432_P7_0_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x70) |

| #define UARTMSP432_P7_0_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x70) |

| #define UARTMSP432_P7_1_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x71) |

| #define UARTMSP432_P7_1_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x71) |

| #define UARTMSP432_P7_1_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x71) |

| #define UARTMSP432_P7_1_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x71) |

| #define UARTMSP432_P7_1_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x71) |

| #define UARTMSP432_P7_1_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x71) |

| #define UARTMSP432_P7_2_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x72) |

| #define UARTMSP432_P7_2_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x72) |

| #define UARTMSP432_P7_2_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x72) |

| #define UARTMSP432_P7_2_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x72) |

| #define UARTMSP432_P7_2_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x72) |

| #define UARTMSP432_P7_2_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x72) |

| #define UARTMSP432_P7_3_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x73) |

| #define UARTMSP432_P7_3_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x73) |

| #define UARTMSP432_P7_3_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x73) |

| #define UARTMSP432_P7_3_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x73) |

| #define UARTMSP432_P7_3_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x73) |

| #define UARTMSP432_P7_3_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x73) |

| #define UARTMSP432_P7_4_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x74) |

| #define UARTMSP432_P7_4_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x74) |

| #define UARTMSP432_P7_4_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x74) |

| #define UARTMSP432_P7_4_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x74) |

| #define UARTMSP432_P7_4_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x74) |

| #define UARTMSP432_P7_4_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x74) |

| #define UARTMSP432_P7_5_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x75) |

| #define UARTMSP432_P7_5_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x75) |

| #define UARTMSP432_P7_5_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x75) |

| #define UARTMSP432_P7_5_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x75) |

| #define UARTMSP432_P7_5_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x75) |

| #define UARTMSP432_P7_5_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x75) |

| #define UARTMSP432_P7_6_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x76) |

| #define UARTMSP432_P7_6_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x76) |

| #define UARTMSP432_P7_6_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x76) |

| #define UARTMSP432_P7_6_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x76) |

| #define UARTMSP432_P7_6_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x76) |

| #define UARTMSP432_P7_6_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x76) |

| #define UARTMSP432_P7_7_UCA0RXD ((PMAP_UCA0RXD << 10) | 0x77) |

| #define UARTMSP432_P7_7_UCA0TXD ((PMAP_UCA0TXD << 10) | 0x77) |

| #define UARTMSP432_P7_7_UCA1RXD ((PMAP_UCA1RXD << 10) | 0x77) |

| #define UARTMSP432_P7_7_UCA1TXD ((PMAP_UCA1TXD << 10) | 0x77) |

| #define UARTMSP432_P7_7_UCA2RXD ((PMAP_UCA2RXD << 10) | 0x77) |

| #define UARTMSP432_P7_7_UCA2TXD ((PMAP_UCA2TXD << 10) | 0x77) |

| #define UARTMSP432_P9_6_UCA3RXD 0x00000196 /* Primary, port 9, pin 6 */ |

| #define UARTMSP432_P9_7_UCA3TXD 0x00000197 /* Primeary, port 9, pin 7 */ |

| typedef void(* UARTMSP432_ErrorCallback) (UART_Handle handle, uint32_t error) |

The definition of an optional callback function used by the UART driver to notify the application when a receive error (FIFO overrun, parity error, etc) occurs.

| UART_Handle | UART_Handle |

| error | The current value of the receive status register. Please refer to the device data sheet to interpret this value. |

| typedef struct UARTMSP432_Object * UARTMSP432_Handle |

| const UART_FxnTable UARTMSP432_fxnTable |