|

|

Power manager interface for the MSP432.

============================================================================

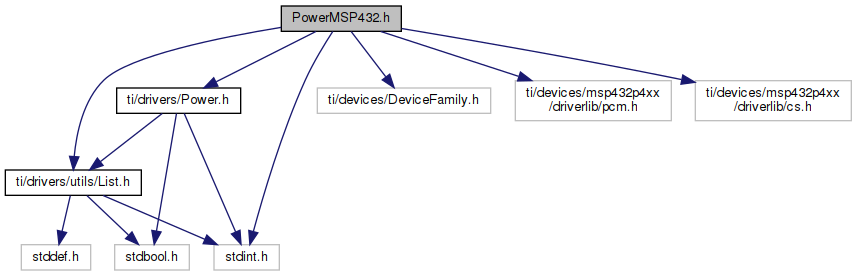

The Power header file should be included in an application as follows:

Refer to Power.h for a complete description of APIs.

#include <stdint.h>#include <ti/devices/DeviceFamily.h>#include <ti/drivers/utils/List.h>#include <ti/drivers/Power.h>#include <ti/devices/msp432p4xx/driverlib/pcm.h>#include <ti/devices/msp432p4xx/driverlib/cs.h>

Go to the source code of this file.

Data Structures | |

| struct | PowerMSP432_PerfLevel |

| Structure defining a performance level. More... | |

| struct | PowerMSP432_Freqs |

| Structure holding device frequencies (in Hz) More... | |

| struct | PowerMSP432_ConfigV1 |

| Power global configuration (MSP432-specific) More... | |

Typedefs | |

| typedef struct PowerMSP432_PerfLevel | PowerMSP432_PerfLevel |

| Structure defining a performance level. More... | |

| typedef struct PowerMSP432_Freqs | PowerMSP432_Freqs |

| Structure holding device frequencies (in Hz) More... | |

| typedef struct PowerMSP432_ConfigV1 | PowerMSP432_ConfigV1 |

| Power global configuration (MSP432-specific) More... | |

Functions | |

| void | PowerMSP432_initPolicy (void) |

| The Power Policy initialization function. More... | |

| void | PowerMSP432_sleepPolicy (void) |

| The SLEEP Power Policy. More... | |

| void | PowerMSP432_deepSleepPolicy (void) |

| The DEEPSLEEP Power Policy. More... | |

| #define PowerMSP432_RESUMETIMESLEEP 32 |

The latency to reserve for resume from SLEEP (usec)

| #define PowerMSP432_TOTALTIMESLEEP 40 |

The total latency to reserve for entry and exit of SLEEP (usec)

| #define PowerMSP432_RESUMETIMEDEEPSLEEP_0 16 |

The latency to reserve for resume from DEEPSLEEP_0 (usec)

| #define PowerMSP432_TOTALTIMEDEEPSLEEP_0 40 |

The total latency to reserve for entry and exit of DEEPSLEEP_0 (usec)

| #define PowerMSP432_RESUMETIMEDEEPSLEEP_1 16 |

The latency to reserve for resume from DEEPSLEEP_1 (usec)

| #define PowerMSP432_TOTALTIMEDEEPSLEEP_1 40 |

The total latency to reserve for entry and exit of DEEPSLEEP_1 (usec)

| #define PowerMSP432_PERIPH_ADC14 0 |

Resource ID: ADC14

| #define PowerMSP432_PERIPH_DMA 1 |

Resource ID: DMA

| #define PowerMSP432_PERIPH_EUSCI_A0 2 |

Resource ID: EUSCI_A0

| #define PowerMSP432_PERIPH_EUSCI_A1 3 |

Resource ID: EUSCI_A1

| #define PowerMSP432_PERIPH_EUSCI_A2 4 |

Resource ID: EUSCI_A2

| #define PowerMSP432_PERIPH_EUSCI_A3 5 |

Resource ID: EUSCI_A3

| #define PowerMSP432_PERIPH_EUSCI_B0 6 |

Resource ID: EUSCI_B0

| #define PowerMSP432_PERIPH_EUSCI_B1 7 |

Resource ID: EUSCI_B1

| #define PowerMSP432_PERIPH_EUSCI_B2 8 |

Resource ID: EUSCI_B2

| #define PowerMSP432_PERIPH_EUSCI_B3 9 |

Resource ID: EUSCI_B3

| #define PowerMSP432_PERIPH_TIMER_A0 10 |

Resource ID: Timer_A0

| #define PowerMSP432_PERIPH_TIMER_A1 11 |

Resource ID: Timer_A1

| #define PowerMSP432_PERIPH_TIMER_A2 12 |

Resource ID: Timer_A2

| #define PowerMSP432_PERIPH_TIMER_A3 13 |

Resource ID: Timer_A3

| #define PowerMSP432_PERIPH_TIMER_T32 14 |

Resource ID: Timer32

| #define PowerMSP432_DISALLOW_SLEEP 0 |

Constraint: Disallow a transition to the SLEEP state

| #define PowerMSP432_DISALLOW_DEEPSLEEP_0 1 |

Constraint: Disallow a transition to the DEEPSLEEP_0 state

| #define PowerMSP432_DISALLOW_DEEPSLEEP_1 2 |

Constraint: Disallow a transition to the DEEPSLEEP_1 state

| #define PowerMSP432_DISALLOW_SHUTDOWN_0 3 |

Constraint: Disallow a transition to the SHUTDOWN_0 state

| #define PowerMSP432_DISALLOW_SHUTDOWN_1 4 |

Constraint: Disallow a transition to the SHUTDOWN_1 state

| #define PowerMSP432_DISALLOW_PERFLEVEL_0 5 |

Constraint: Disallow a transition to PERFLEVEL_0

| #define PowerMSP432_DISALLOW_PERFLEVEL_1 6 |

Constraint: Disallow a transition to PERFLEVEL_1

| #define PowerMSP432_DISALLOW_PERFLEVEL_2 7 |

Constraint: Disallow a transition to PERFLEVEL_2

| #define PowerMSP432_DISALLOW_PERFLEVEL_3 8 |

Constraint: Disallow a transition to PERFLEVEL_3

| #define PowerMSP432_DISALLOW_PERFLEVEL_4 9 |

Constraint: Disallow a transition to PERFLEVEL_4

| #define PowerMSP432_DISALLOW_PERFLEVEL_5 10 |

Constraint: Disallow a transition to PERFLEVEL_5

| #define PowerMSP432_DISALLOW_PERFLEVEL_6 11 |

Constraint: Disallow a transition to PERFLEVEL_6

| #define PowerMSP432_DISALLOW_PERFLEVEL_7 12 |

Constraint: Disallow a transition to PERFLEVEL_7

| #define PowerMSP432_DISALLOW_PERF_CHANGES 13 |

Constraint: Disallow any performance level changes

| #define PowerMSP432_ENTERING_SLEEP 0x1 |

Power event: The device is entering the SLEEP state

| #define PowerMSP432_ENTERING_DEEPSLEEP 0x2 |

Power event: The device is entering a DEEPSLEEP state

| #define PowerMSP432_ENTERING_SHUTDOWN 0x4 |

Power event: The device is entering a SHUTDOWN state

| #define PowerMSP432_AWAKE_SLEEP 0x8 |

Power event: The device is waking from the SLEEP state

| #define PowerMSP432_AWAKE_DEEPSLEEP 0x10 |

Power event: The device is waking from a DEEPSLEEP state

| #define PowerMSP432_START_CHANGE_PERF_LEVEL 0x20 |

Power event: A performance level change has been initiated

| #define PowerMSP432_DONE_CHANGE_PERF_LEVEL 0x40 |

Power event: A performance level change has completed

| #define PowerMSP432_SLEEP 0x1 |

Device state of LPM0

| #define PowerMSP432_DEEPSLEEP_0 0x2 |

Device state of LPM3

| #define PowerMSP432_DEEPSLEEP_1 0x4 |

Device state of LPM4

| #define PowerMSP432_SHUTDOWN_0 0x0 |

Device state of LPM3.5

| #define PowerMSP432_SHUTDOWN_1 0x1 |

Device state of LPM4.5

| typedef struct PowerMSP432_PerfLevel PowerMSP432_PerfLevel |

Structure defining a performance level.

The MCU performance level can be set with Power_setPerformanceLevel(). A performance level is defined by this PowerMSP432_PerfLevel structure.

The Power driver currently supports four pre-defined performance levels:

Up to four optional 'custom' performance levels can be defined by the user. Performance levels are designated by an index, starting with zero. Any custom performance levels will be indexed following the last pre-defined level. For example, if there are 4 pre-defined levels, they will have indices from '0' to '3'. If there are custom levels defined, they will be indexed starting with '4'.

Eight performance level constraints are supported, one for each of the four pre-defined levels:

plus four for the optional custom performance levels:

The parameters that are used to define a performance level are shown below.

To define custom performance levels the user must add an array of PowerMSP432_PerfLevel structures to their board file, and then reference this array in the PowerMSP432_config structure. An example is shown below.

First, if not already included in the board file, add the includes of cs.h and pcm.h

Next, add an array with two new performance levels:

Then, update the PowerMSP432_config structure to 1) reference the new custom levels, and 2) as appropriate, enable extended performance scaling support, and define the relevant extended configuration parameters. In the first custom perf level shown above the HFXT and LFXT crystals are used as clock sources, so for this example the extended support parameters need to be specfied.

The code below shows additions to the PowerMSP432_config structure for this example. The first two additions to PowerMSP432_config reference the array of custom perf levels, and indicate the number of custom levels. The third addition enables extended support for crystals. The remaining parameters define crystal settings, plus an application-provided ISR function for handling any Clock System fault interrupts.

| typedef struct PowerMSP432_Freqs PowerMSP432_Freqs |

Structure holding device frequencies (in Hz)

| typedef struct PowerMSP432_ConfigV1 PowerMSP432_ConfigV1 |

Power global configuration (MSP432-specific)

| void PowerMSP432_initPolicy | ( | void | ) |

The Power Policy initialization function.

This is an optional policy initialization function that will be called during application startup, during Power Manager initialization.

| void PowerMSP432_sleepPolicy | ( | void | ) |

The SLEEP Power Policy.

This is a simple Power Policy that will transition the device to the PowerMSP432_SLEEP state, unless there is a constraint prohibiting this. If PowerMSP432_SLEEP cannot be activated, CPU Wait For Interrupt (WFI) will be chosen instead.

In order for this policy to run, 1) it must be selected as the Power Policy (either by being specified as the 'policyFxn' in the PowerMSP432_config structure, or specified at runtime with Power_setPolicy()), and 2) the Power Policy must be enabled (either via 'enablePolicy' in the PowerMSP432_config structure, or via a call to Power_enablePolicy() at runtime).

| void PowerMSP432_deepSleepPolicy | ( | void | ) |

The DEEPSLEEP Power Policy.

This is an agressive Power Policy which checks active constraints and automatically transitions the device into the deepest sleep state possible.

The first goal is to enter PowerMSP432_DEEPSLEEP_1; if that is not allowed, the secondary goal is PowerMSP432_DEEPSLEEP_0; if that is not allowed, the next goal is PowerMSP432_SLEEP; and finally, if that is not allowed, CPU Wait For Interrupt (WFI) will be chosen.

In order for this policy to run, 1) it must be selected as the Power Policy (either by being specified as the 'policyFxn' in the PowerMSP432_config structure, or specified at runtime with Power_setPolicy()), and 2) the Power Policy must be enabled (either via 'enablePolicy' in the PowerMSP432_config structure, or via a call to Power_enablePolicy() at runtime).