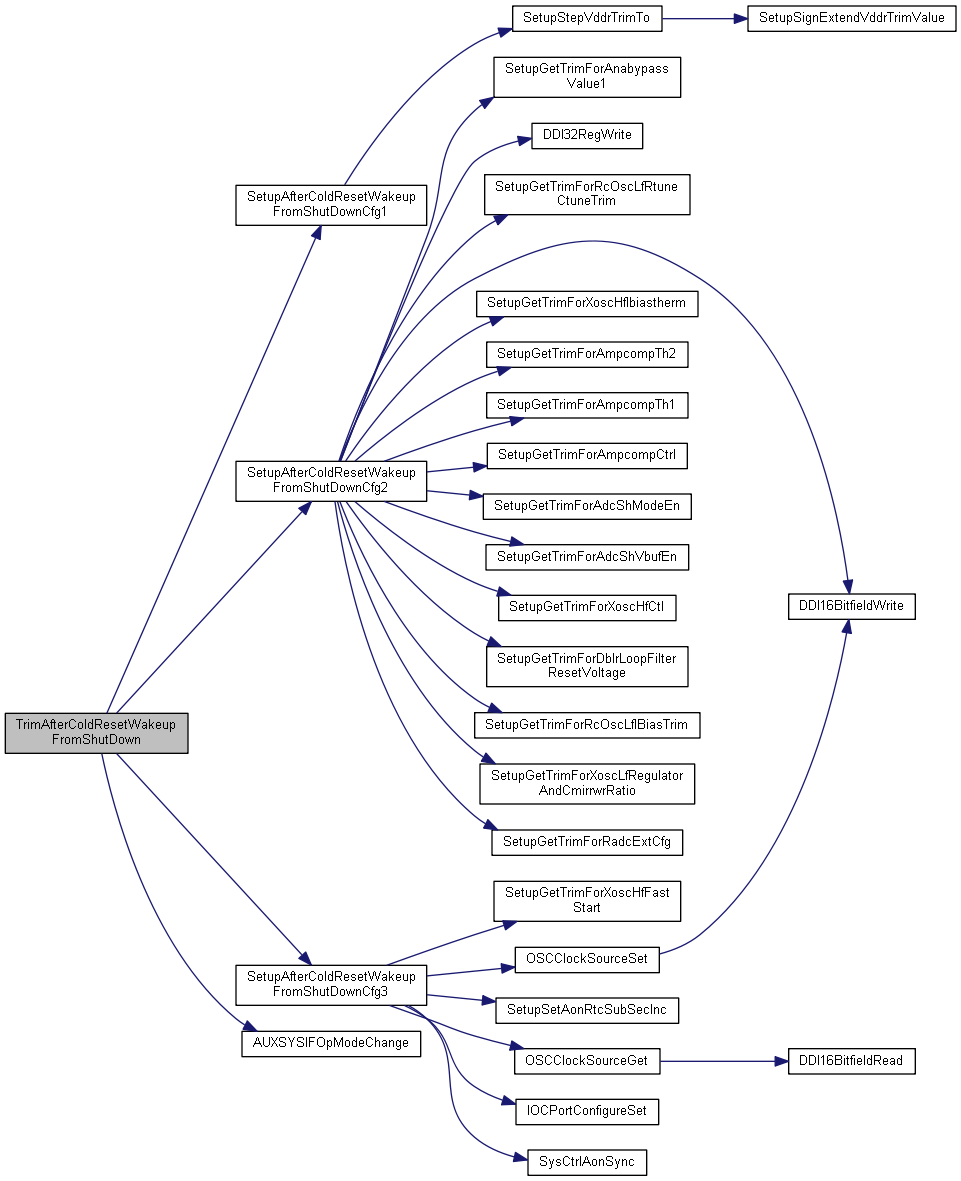

Trims to be applied when coming from SHUTDOWN (also called when coming from PIN_RESET).

244 uint32_t ccfg_ModeConfReg ;

247 if (( HWREG( CCFG_BASE + CCFG_O_SIZE_AND_DIS_FLAGS ) & CCFG_SIZE_AND_DIS_FLAGS_DIS_ALT_DCDC_SETTING ) == 0 ) {

251 HWREGB( ADI3_BASE + ADI_O_MASK4B + ( ADI_3_REFSYS_O_DCDCCTL5 * 2 )) = ( 0xF0 |

252 ( HWREG( CCFG_BASE + CCFG_O_MODE_CONF_1 ) >> CCFG_MODE_CONF_1_ALT_DCDC_IPEAK_S ));

263 HWREG(AUX_DDI0_OSC_BASE + DDI_O_MASK16B + (DDI_0_OSC_O_CTL0 << 1) + 4) = DDI_0_OSC_CTL0_CLK_DCDC_SRC_SEL_M | (DDI_0_OSC_CTL0_CLK_DCDC_SRC_SEL_M >> 16);

265 HWREGH(AUX_DDI0_OSC_BASE + DDI_0_OSC_O_CTL0);

268 ccfg_ModeConfReg = HWREG( CCFG_BASE + CCFG_O_MODE_CONF );

277 if ((( ccfg_ModeConfReg & CCFG_MODE_CONF_VDDR_EXT_LOAD ) == 0 ) &&

278 (( ccfg_ModeConfReg & CCFG_MODE_CONF_VDDS_BOD_LEVEL ) != 0 ) )

280 HWREGB( ADI3_BASE + ADI_3_REFSYS_O_DCDCCTL3 ) = ADI_3_REFSYS_DCDCCTL3_VDDR_BOOST_COMP_BOOST ;

285 #if ( CCFG_BASE == CCFG_BASE_DEFAULT )

288 NOROM_SetupAfterColdResetWakeupFromShutDownCfg2( ui32Fcfg1Revision, ccfg_ModeConfReg );

293 uint32_t ui32TrimValue ;

296 trimReg = HWREG( FCFG1_BASE + FCFG1_O_DAC_BIAS_CNF );

297 ui32TrimValue = (( trimReg & FCFG1_DAC_BIAS_CNF_LPM_TRIM_IOUT_M ) >>

298 FCFG1_DAC_BIAS_CNF_LPM_TRIM_IOUT_S ) ;

302 if ( trimReg & FCFG1_DAC_BIAS_CNF_LPM_BIAS_BACKUP_EN ) {

303 HWREGB( ADI3_BASE + ADI_O_SET + ADI_3_REFSYS_O_AUX_DEBUG ) = ADI_3_REFSYS_AUX_DEBUG_LPM_BIAS_BACKUP_EN;

305 HWREGB( ADI3_BASE + ADI_O_CLR + ADI_3_REFSYS_O_AUX_DEBUG ) = ADI_3_REFSYS_AUX_DEBUG_LPM_BIAS_BACKUP_EN;

309 uint32_t widthTrim = (( trimReg & FCFG1_DAC_BIAS_CNF_LPM_BIAS_WIDTH_TRIM_M ) >> FCFG1_DAC_BIAS_CNF_LPM_BIAS_WIDTH_TRIM_S );

310 HWREGH( AUX_ADI4_BASE + ADI_O_MASK8B + ( ADI_4_AUX_O_COMP * 2 )) =

319 #if ( CCFG_BASE == CCFG_BASE_DEFAULT )

322 NOROM_SetupAfterColdResetWakeupFromShutDownCfg3( ccfg_ModeConfReg );

329 HWREGBITW( FLASH_BASE + FLASH_O_CFG, FLASH_CFG_DIS_EFUSECLK_BITN ) = 1;

#define ADI_4_AUX_O_LPMBIAS

Definition: setup.c:47

void SetupAfterColdResetWakeupFromShutDownCfg3(uint32_t ccfg_ModeConfReg)

Third part of configuration required after cold reset and when waking up from shutdown.

Definition: setup_rom.c:324

#define ADI_4_AUX_COMP_LPM_BIAS_WIDTH_TRIM_S

Definition: setup.c:51

#define ADI_4_AUX_COMP_LPM_BIAS_WIDTH_TRIM_M

Definition: setup.c:50

#define AUX_SYSIF_OPMODE_TARGET_PDA

Definition: aux_sysif.h:99

void SetupAfterColdResetWakeupFromShutDownCfg1(uint32_t ccfg_ModeConfReg)

First part of configuration required after cold reset and when waking up from shutdown.

Definition: setup_rom.c:167

void AUXSYSIFOpModeChange(uint32_t targetOpMode)

Changes the AUX operational mode to the requested target mode.

Definition: aux_sysif.c:67

#define ADI_4_AUX_LPMBIAS_LPM_TRIM_IOUT_S

Definition: setup.c:49

void SetupAfterColdResetWakeupFromShutDownCfg2(uint32_t ui32Fcfg1Revision, uint32_t ccfg_ModeConfReg)

Second part of configuration required after cold reset and when waking up from shutdown.

Definition: setup_rom.c:222

#define ADI_4_AUX_LPMBIAS_LPM_TRIM_IOUT_M

Definition: setup.c:48