Data Structures | |

| struct | tDMAControlTable |

| A structure that defines an entry in the channel control table. More... | |

Functions | |

| static void | uDMAEnable (uint32_t ui32Base) |

| Enables the uDMA controller for use. More... | |

| static void | uDMADisable (uint32_t ui32Base) |

| Disables the uDMA controller for use. More... | |

| static uint32_t | uDMAErrorStatusGet (uint32_t ui32Base) |

| Gets the uDMA error status. More... | |

| static void | uDMAErrorStatusClear (uint32_t ui32Base) |

| Clears the uDMA error interrupt. More... | |

| static void | uDMAChannelEnable (uint32_t ui32Base, uint32_t ui32ChannelNum) |

| Enables a uDMA channel for operation. More... | |

| static void | uDMAChannelDisable (uint32_t ui32Base, uint32_t ui32ChannelNum) |

| Disables a uDMA channel for operation. More... | |

| static bool | uDMAChannelIsEnabled (uint32_t ui32Base, uint32_t ui32ChannelNum) |

| Checks if a uDMA channel is enabled for operation. More... | |

| static void | uDMAControlBaseSet (uint32_t ui32Base, void *pControlTable) |

| Sets the base address for the channel control table. More... | |

| static void * | uDMAControlBaseGet (uint32_t ui32Base) |

| Gets the base address for the channel control table. More... | |

| static void * | uDMAControlAlternateBaseGet (uint32_t ui32Base) |

| Gets the base address for the channel control table alternate structures. More... | |

| static void | uDMAChannelRequest (uint32_t ui32Base, uint32_t ui32ChannelNum) |

| Requests a uDMA channel to start a transfer. More... | |

| void | uDMAChannelAttributeEnable (uint32_t ui32Base, uint32_t ui32ChannelNum, uint32_t ui32Attr) |

| Enables attributes of a uDMA channel. More... | |

| void | uDMAChannelAttributeDisable (uint32_t ui32Base, uint32_t ui32ChannelNum, uint32_t ui32Attr) |

| Disables attributes of an uDMA channel. More... | |

| uint32_t | uDMAChannelAttributeGet (uint32_t ui32Base, uint32_t ui32ChannelNum) |

| Gets the enabled attributes of a uDMA channel. More... | |

| void | uDMAChannelControlSet (uint32_t ui32Base, uint32_t ui32ChannelStructIndex, uint32_t ui32Control) |

| Sets the control parameters for a uDMA channel control structure. More... | |

| void | uDMAChannelTransferSet (uint32_t ui32Base, uint32_t ui32ChannelStructIndex, uint32_t ui32Mode, void *pvSrcAddr, void *pvDstAddr, uint32_t ui32TransferSize) |

| Sets the transfer parameters for a uDMA channel control structure. More... | |

| void | uDMAChannelScatterGatherSet (uint32_t ui32Base, uint32_t ui32ChannelNum, uint32_t ui32TaskCount, void *pvTaskList, uint32_t ui32IsPeriphSG) |

| Configures a uDMA channel for scatter-gather mode. More... | |

| uint32_t | uDMAChannelSizeGet (uint32_t ui32Base, uint32_t ui32ChannelStructIndex) |

| Gets the current transfer size for a uDMA channel control structure. More... | |

| uint32_t | uDMAChannelModeGet (uint32_t ui32Base, uint32_t ui32ChannelStructIndex) |

| Gets the transfer mode for a uDMA channel control structure. More... | |

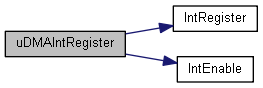

| static void | uDMAIntRegister (uint32_t ui32Base, uint32_t ui32IntChannel, void(*pfnHandler)(void)) |

| Registers an interrupt handler for the uDMA controller in the dynamic interrupt table. More... | |

| static void | uDMAIntUnregister (uint32_t ui32Base, uint32_t ui32IntChannel) |

| Unregisters an interrupt handler for the uDMA controller in the dynamic interrupt table. More... | |

| static void | uDMAIntClear (uint32_t ui32Base, uint32_t ui32ChanMask) |

| Clears uDMA interrupt done status. More... | |

| static uint32_t | uDMAIntStatus (uint32_t ui32Base) |

| Get the uDMA interrupt status. More... | |

| static void | uDMAIntSwEventEnable (uint32_t ui32Base, uint32_t ui32IntChannel) |

| Enable interrupt on software event driven uDMA transfers. More... | |

| static void | uDMAIntSwEventDisable (uint32_t ui32Base, uint32_t ui32IntChannel) |

| Disable interrupt on software event driven uDMA transfers. More... | |

| static uint32_t | uDMAGetStatus (uint32_t ui32Base) |

| Return the status of the uDMA module. More... | |

| static void | uDMAChannelPrioritySet (uint32_t ui32Base, uint32_t ui32ChannelNum) |

| Set the priority of a uDMA channel. More... | |

| static bool | uDMAChannelPriorityGet (uint32_t ui32Base, uint32_t ui32ChannelNum) |

| Get the priority of a uDMA channel. More... | |

| static void | uDMAChannelPriorityClear (uint32_t ui32Base, uint32_t ui32ChannelNum) |

| Clear the priority of a uDMA channel. More... | |

| void uDMAChannelAttributeDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32ChannelNum, | ||

| uint32_t | ui32Attr | ||

| ) |

Disables attributes of an uDMA channel.

This function is used to disable attributes of a uDMA channel.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | is the channel to configure. |

| ui32Attr | is a combination of attributes for the channel. The parameter is the bitwise OR of any of the following:

|

| void uDMAChannelAttributeEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32ChannelNum, | ||

| uint32_t | ui32Attr | ||

| ) |

Enables attributes of a uDMA channel.

This function is used to enable attributes of a uDMA channel.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | is the channel to configure. |

| ui32Attr | is a combination of attributes for the channel. The parameter is the bitwise OR of any of the following:

|

| uint32_t uDMAChannelAttributeGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32ChannelNum | ||

| ) |

Gets the enabled attributes of a uDMA channel.

This function returns a combination of flags representing the attributes of the uDMA channel.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | is the channel to configure. |

| void uDMAChannelControlSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32ChannelStructIndex, | ||

| uint32_t | ui32Control | ||

| ) |

Sets the control parameters for a uDMA channel control structure.

This function is used to set control parameters for a uDMA transfer. These are typically parameters that are not changed often.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelStructIndex | is the bitwise OR of the uDMA channel number and:

|

| ui32Control | is the bitwise OR of five values:

|

|

inlinestatic |

Disables a uDMA channel for operation.

This function disables a specific uDMA channel. Once disabled, a channel will not respond to uDMA transfer requests until re-enabled via uDMAChannelEnable().

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | is the channel number to disable. |

|

inlinestatic |

Enables a uDMA channel for operation.

This function enables a specific uDMA channel for use. This function must be used to enable a channel before it can be used to perform a uDMA transfer.

When a uDMA transfer is completed, the channel will be automatically disabled by the uDMA controller. Therefore, this function should be called prior to starting up any new transfer.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | is the channel number to enable. |

|

inlinestatic |

Checks if a uDMA channel is enabled for operation.

This function checks to see if a specific uDMA channel is enabled. This can be used to check the status of a transfer, since the channel will be automatically disabled at the end of a transfer.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | is the channel number to check. |

true : Channel is enabled.false : Disabled. | uint32_t uDMAChannelModeGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32ChannelStructIndex | ||

| ) |

Gets the transfer mode for a uDMA channel control structure.

This function is used to get the transfer mode for the uDMA channel. It can be used to query the status of a transfer on a channel. When the transfer is complete the mode will be UDMA_MODE_STOP.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelStructIndex | is the bitwise OR of the uDMA channel number and: |

|

inlinestatic |

Clear the priority of a uDMA channel.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | The uDMA channel to clear the priority for. |

|

inlinestatic |

Get the priority of a uDMA channel.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | The uDMA channel to get the priority for. |

|

inlinestatic |

Set the priority of a uDMA channel.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | is uDMA channel to set the priority for. |

|

inlinestatic |

Requests a uDMA channel to start a transfer.

This function allows software to request a uDMA channel to begin a transfer. This could be used for performing a memory to memory transfer, or if for some reason a transfer needs to be initiated by software instead of the peripheral associated with that channel.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | is the channel number on which to request a uDMA transfer. |

| void uDMAChannelScatterGatherSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32ChannelNum, | ||

| uint32_t | ui32TaskCount, | ||

| void * | pvTaskList, | ||

| uint32_t | ui32IsPeriphSG | ||

| ) |

Configures a uDMA channel for scatter-gather mode.

This function is used to configure a channel for scatter-gather mode. The caller must have already set up a task list, and pass a pointer to the start of the task list as the pvTaskList parameter.

The ui32TaskCount parameter is the count of tasks in the task list, not the size of the task list.

The flag bIsPeriphSG should be used to indicate if the scatter-gather should be configured for a peripheral or memory scatter-gather operation.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelNum | is the uDMA channel number. |

| ui32TaskCount | is the number of scatter-gather tasks to execute. |

| pvTaskList | is a pointer to the beginning of the scatter-gather task list. |

| ui32IsPeriphSG | is a flag to indicate it is a peripheral scatter-gather transfer (else it will be memory scatter-gather transfer) |

| uint32_t uDMAChannelSizeGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32ChannelStructIndex | ||

| ) |

Gets the current transfer size for a uDMA channel control structure.

This function is used to get the uDMA transfer size for a channel. The transfer size is the number of items to transfer, where the size of an item might be 8, 16, or 32 bits. If a partial transfer has already occurred, then the number of remaining items will be returned. If the transfer is complete, then 0 will be returned.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelStructIndex | is the bitwise OR of the uDMA channel number and: |

| void uDMAChannelTransferSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32ChannelStructIndex, | ||

| uint32_t | ui32Mode, | ||

| void * | pvSrcAddr, | ||

| void * | pvDstAddr, | ||

| uint32_t | ui32TransferSize | ||

| ) |

Sets the transfer parameters for a uDMA channel control structure.

This function is used to set the parameters for a uDMA transfer. These are typically parameters that are changed often. The function uDMAChannelControlSet() MUST be called at least once for this channel prior to calling this function.

The pvSrcAddr and pvDstAddr parameters are pointers to the first location of the data to be transferred. These addresses should be aligned according to the item size. The compiler will take care of this if the pointers are pointing to storage of the appropriate data type.

The two scatter/gather modes, MEMORY and PERIPHERAL, are actually different depending on whether the primary or alternate control structure is selected. This function will look for the UDMA_PRI_SELECT and UDMA_ALT_SELECT flag along with the channel number and will set the scatter/gather mode as appropriate for the primary or alternate control structure.

The channel must also be enabled using uDMAChannelEnable() after calling this function. The transfer will not begin until the channel has been set up and enabled. Note that the channel is automatically disabled after the transfer is completed, meaning that uDMAChannelEnable() must be called again after setting up the next transfer.

| ui32Base | is the base address of the uDMA port. |

| ui32ChannelStructIndex | is the bitwise OR of the uDMA channel number and:

|

| ui32Mode | is the type of uDMA transfer. The parameter should be one of the following values:

|

| pvSrcAddr | is the source address for the transfer. |

| pvDstAddr | is the destination address for the transfer. |

| ui32TransferSize | is the number of data items to transfer (NOT bytes). |

|

inlinestatic |

Gets the base address for the channel control table alternate structures.

This function gets the base address of the second half of the channel control table that holds the alternate control structures for each channel.

| ui32Base | is the base address of the uDMA port. |

|

inlinestatic |

Gets the base address for the channel control table.

This function gets the base address of the channel control table. This table resides in system memory and holds control information for each uDMA channel.

| ui32Base | is the base address of the uDMA port. |

|

inlinestatic |

Sets the base address for the channel control table.

This function sets the base address of the channel control table. This table resides in system memory and holds control information for each uDMA channel. The table must be aligned on a 1024 byte boundary. The base address must be set before any of the channel functions can be used. Setting the base address of the primary control table will automatically set the address for the alternate control table as the next memory location after the primary control table.

The size of the channel control table depends on the number of uDMA channels, and which transfer modes are used. Refer to the introductory text and the microcontroller datasheet for more information about the channel control table.

| ui32Base | is the base address of the uDMA port. |

| pControlTable | is a pointer to the 1024 byte aligned base address of the uDMA channel control table. The address must be an absolute address in system memory space. |

|

inlinestatic |

Disables the uDMA controller for use.

This function disables the uDMA controller. Once disabled, the uDMA controller will not operate until re-enabled with uDMAEnable().

| ui32Base | is the base address of the uDMA port. |

|

inlinestatic |

Enables the uDMA controller for use.

This function enables the uDMA controller. The uDMA controller must be enabled before it can be configured and used.

| ui32Base | is the base address of the uDMA port. |

|

inlinestatic |

Clears the uDMA error interrupt.

This function clears a pending uDMA error interrupt. It should be called from within the uDMA error interrupt handler to clear the interrupt.

| ui32Base | is the base address of the uDMA port. |

|

inlinestatic |

Gets the uDMA error status.

This function returns the uDMA error status. It should be called from within the uDMA error interrupt handler to determine if a uDMA error occurred.

| ui32Base | is the base address of the uDMA port. |

|

inlinestatic |

Return the status of the uDMA module.

| ui32Base | is the base address of the uDMA port. |

|

inlinestatic |

Clears uDMA interrupt done status.

Clears bits in the uDMA interrupt status register according to which bits are set in ui32ChanMask. There is one bit for each channel. If a a bit is set in ui32ChanMask, then that corresponding channel's interrupt status will be cleared (if it was set).

| ui32Base | is the base address of the uDMA port. |

| ui32ChanMask | is a 32-bit mask with one bit for each uDMA channel. |

|

inlinestatic |

Registers an interrupt handler for the uDMA controller in the dynamic interrupt table.

This function registers a function as the interrupt handler for a specific interrupt and enables the corresponding interrupt in the interrupt controller.

| ui32Base | is the base address of the uDMA module. |

| ui32IntChannel | specifies which uDMA interrupt is to be registered.

|

| pfnHandler | is a pointer to the function to be called when the interrupt is activated. |

|

inlinestatic |

Get the uDMA interrupt status.

This function returns the interrupt status for the specified UDMA. This function does not differentiate between software or hardware activated interrupts.

| ui32Base | is the base address of the uDMA port. |

|

inlinestatic |

Disable interrupt on software event driven uDMA transfers.

This register disables the blocking of the uDMA status signals propagation to the hardware peripheral connected to the uDMA on the ui32IntChannel.

| ui32Base | is the base address of the uDMA port. |

| ui32IntChannel | identifies which uDMA interrupt to disable software interrupts for. |

|

inlinestatic |

Enable interrupt on software event driven uDMA transfers.

| ui32Base | is the base address of the uDMA port. |

| ui32IntChannel | identifies which uDMA interrupt to enable software interrupts for. |

|

inlinestatic |

Unregisters an interrupt handler for the uDMA controller in the dynamic interrupt table.

This function will disable and clear the handler to be called for the specified uDMA interrupt.

| ui32Base | is the base address of the uDMA module. |

| ui32IntChannel | specifies which uDMA interrupt to unregister.

|

| #define UDMA_ALT_SELECT 0x00000020 |

Referenced by uDMAChannelScatterGatherSet(), and uDMAChannelTransferSet().

| #define UDMA_ARB_1 0x00000000 |

| #define UDMA_ARB_1024 0x00028000 |

| #define UDMA_ARB_128 0x0001c000 |

| #define UDMA_ARB_16 0x00010000 |

| #define UDMA_ARB_2 0x00004000 |

| #define UDMA_ARB_256 0x00020000 |

| #define UDMA_ARB_32 0x00014000 |

| #define UDMA_ARB_4 0x00008000 |

Referenced by uDMAChannelScatterGatherSet().

| #define UDMA_ARB_512 0x00024000 |

| #define UDMA_ARB_64 0x00018000 |

| #define UDMA_ARB_8 0x0000c000 |

| #define UDMA_ARB_M 0x0003C000 |

Referenced by uDMAChannelControlSet().

| #define UDMA_ARB_S 14 |

| #define UDMA_ATTR_ALL 0x0000000F |

| #define UDMA_ATTR_ALTSELECT 0x00000002 |

Referenced by uDMAChannelAttributeDisable(), uDMAChannelAttributeEnable(), and uDMAChannelAttributeGet().

| #define UDMA_ATTR_HIGH_PRIORITY 0x00000004 |

Referenced by uDMAChannelAttributeDisable(), uDMAChannelAttributeEnable(), and uDMAChannelAttributeGet().

| #define UDMA_ATTR_REQMASK 0x00000008 |

Referenced by uDMAChannelAttributeDisable(), uDMAChannelAttributeEnable(), and uDMAChannelAttributeGet().

| #define UDMA_ATTR_USEBURST 0x00000001 |

Referenced by uDMAChannelAttributeDisable(), uDMAChannelAttributeEnable(), and uDMAChannelAttributeGet().

| #define UDMA_CHAN_AON_PROG2 13 |

| #define UDMA_CHAN_AON_RTC 15 |

| #define UDMA_CHAN_AUX_ADC 7 |

| #define UDMA_CHAN_AUX_SW 8 |

| #define UDMA_CHAN_DMA_PROG 14 |

| #define UDMA_CHAN_SSI0_RX 3 |

| #define UDMA_CHAN_SSI0_TX 4 |

| #define UDMA_CHAN_SSI1_RX 16 |

| #define UDMA_CHAN_SSI1_TX 17 |

| #define UDMA_CHAN_SW_EVT0 0 |

| #define UDMA_CHAN_SW_EVT1 18 |

| #define UDMA_CHAN_SW_EVT2 19 |

| #define UDMA_CHAN_SW_EVT3 20 |

| #define UDMA_CHAN_TIMER0_A 9 |

| #define UDMA_CHAN_TIMER0_B 10 |

| #define UDMA_CHAN_TIMER1_A 11 |

| #define UDMA_CHAN_TIMER1_B 12 |

| #define UDMA_CHAN_UART0_RX 1 |

| #define UDMA_CHAN_UART0_TX 2 |

| #define UDMA_DST_INC_16 0x40000000 |

| #define UDMA_DST_INC_32 0x80000000 |

Referenced by uDMAChannelScatterGatherSet().

| #define UDMA_DST_INC_8 0x00000000 |

| #define UDMA_DST_INC_M 0xC0000000 |

Referenced by uDMAChannelControlSet(), and uDMAChannelTransferSet().

| #define UDMA_DST_INC_NONE 0xC0000000 |

Referenced by uDMAChannelTransferSet().

| #define UDMA_DST_INC_S 30 |

Referenced by uDMAChannelTransferSet().

| #define UDMA_MODE_ALT_SELECT 0x00000001 |

Referenced by uDMAChannelModeGet(), and uDMAChannelTransferSet().

| #define UDMA_MODE_AUTO 0x00000002 |

| #define UDMA_MODE_BASIC 0x00000001 |

| #define UDMA_MODE_M 0x00000007 |

Referenced by uDMAChannelModeGet(), uDMAChannelSizeGet(), and uDMAChannelTransferSet().

| #define UDMA_MODE_MEM_SCATTER_GATHER 0x00000004 |

Referenced by uDMAChannelModeGet(), uDMAChannelScatterGatherSet(), and uDMAChannelTransferSet().

| #define UDMA_MODE_PER_SCATTER_GATHER 0x00000006 |

Referenced by uDMAChannelModeGet(), uDMAChannelScatterGatherSet(), and uDMAChannelTransferSet().

| #define UDMA_MODE_PINGPONG 0x00000003 |

| #define UDMA_MODE_STOP 0x00000000 |

| #define UDMA_NEXT_USEBURST 0x00000008 |

Referenced by uDMAChannelControlSet().

| #define UDMA_NUM_CHANNELS 21 |

Referenced by uDMAChannelAttributeDisable(), uDMAChannelAttributeEnable(), uDMAChannelAttributeGet(), uDMAChannelControlSet(), uDMAChannelDisable(), uDMAChannelEnable(), uDMAChannelIsEnabled(), uDMAChannelModeGet(), uDMAChannelPriorityClear(), uDMAChannelPriorityGet(), uDMAChannelPrioritySet(), uDMAChannelRequest(), uDMAChannelScatterGatherSet(), uDMAChannelSizeGet(), uDMAChannelTransferSet(), uDMAIntSwEventDisable(), and uDMAIntSwEventEnable().

| #define UDMA_PRI_SELECT 0x00000000 |

| #define UDMA_PRIORITY_HIGH 0x00000001 |

Referenced by uDMAChannelPriorityGet().

| #define UDMA_PRIORITY_LOW 0x00000000 |

Referenced by uDMAChannelPriorityGet().

| #define UDMA_SIZE_16 0x11000000 |

| #define UDMA_SIZE_32 0x22000000 |

Referenced by uDMAChannelScatterGatherSet().

| #define UDMA_SIZE_8 0x00000000 |

| #define UDMA_SIZE_M 0x33000000 |

Referenced by uDMAChannelControlSet().

| #define UDMA_SIZE_S 24 |

| #define UDMA_SRC_INC_16 0x04000000 |

| #define UDMA_SRC_INC_32 0x08000000 |

Referenced by uDMAChannelScatterGatherSet().

| #define UDMA_SRC_INC_8 0x00000000 |

| #define UDMA_SRC_INC_M 0x0C000000 |

Referenced by uDMAChannelControlSet(), and uDMAChannelTransferSet().

| #define UDMA_SRC_INC_NONE 0x0c000000 |

Referenced by uDMAChannelTransferSet().

| #define UDMA_SRC_INC_S 26 |

Referenced by uDMAChannelTransferSet().

| #define UDMA_XFER_SIZE_M 0x00003FF0 |

Referenced by uDMAChannelSizeGet(), and uDMAChannelTransferSet().

| #define UDMA_XFER_SIZE_MAX 1024 |

Referenced by uDMAChannelScatterGatherSet(), and uDMAChannelTransferSet().

| #define UDMA_XFER_SIZE_S 4 |

Referenced by uDMAChannelScatterGatherSet(), uDMAChannelSizeGet(), and uDMAChannelTransferSet().

| #define uDMATaskStructEntry | ( | ui32TransferCount, | |

| ui32ItemSize, | |||

| ui32SrcIncrement, | |||

| pvSrcAddr, | |||

| ui32DstIncrement, | |||

| pvDstAddr, | |||

| ui32ArbSize, | |||

| ui32Mode | |||

| ) |

A helper macro for building scatter-gather task table entries.

This macro is intended to be used to help populate a table of uDMA tasks for a scatter-gather transfer. This macro will calculate the values for the fields of a task structure entry based on the input parameters.

There are specific requirements for the values of each parameter. No checking is done so it is up to the caller to ensure that correct values are used for the parameters.

This macro is intended to be used to initialize individual entries of a structure of tDMAControlTable type, like this:

tDMAControlTable MyTaskList[] =

{

uDMATaskStructEntry(Task1Count, UDMA_SIZE_8,

UDMA_SRC_INC_8, MySourceBuf,

UDMA_DST_INC_8, MyDestBuf,

UDMA_ARB_8, UDMA_MODE_MEM_SCATTER_GATHER),

uDMATaskStructEntry(Task2Count, ... ),

}

| ui32TransferCount | is the count of items to transfer for this task. It must be in the range 1-1024. |

| ui32ItemSize | is the bit size of the items to transfer for this task. It must be one of: |

| ui32SrcIncrement | is the bit size increment for source data. It must be one of: |

| pvSrcAddr | is the starting address of the data to transfer. |

| ui32DstIncrement | is the bit size increment for destination data. It must be one of: |

| pvDstAddr | is the starting address of the destination data. |

| ui32ArbSize | is the arbitration size to use for the transfer task. This is used to select the arbitration size in powers of 2, from 1 to 1024. It must be one of: |

| ui32Mode | is the transfer mode for this task. Note that normally all tasks will be one of the scatter-gather modes while the last task is a task list will be AUTO or BASIC. It must be one of: |