|

| struct | I2SControlTable |

| | A structure that defines an audio control table. Note: Memory for this structure must be initialized by user application. See detailed description! More...

|

| |

|

| void | I2SEnable (uint32_t ui32Base) |

| | Enables the I2S module for operation. More...

|

| |

| static void | I2SDisable (uint32_t ui32Base) |

| | Disables the I2S module for operation. More...

|

| |

| void | I2SAudioFormatConfigure (uint32_t ui32Base, uint32_t ui32FmtCfg, uint32_t ui32BitClkDelay) |

| | Configures the I2S module. More...

|

| |

| void | I2SChannelConfigure (uint32_t ui32Base, uint32_t ui32Chan0Cfg, uint32_t ui32Chan1Cfg) |

| | Setup the audio channel configuration. More...

|

| |

| static void | I2SClockConfigure (uint32_t ui32Base, uint32_t ui32ClkConfig) |

| | Configure the I2S frame clock. More...

|

| |

| void | I2SBufferConfig (uint32_t ui32Base, uint32_t ui32InBufBase, uint32_t ui32OutBufBase, uint16_t ui16DMABufSize, uint16_t ui16ChanBufSize) |

| | Set the input buffer pointers. More...

|

| |

| void | I2SPointerUpdate (uint32_t ui32Base, bool bInput) |

| | Update the buffer pointers. More...

|

| |

| void | I2SPointerSet (uint32_t ui32Base, bool bInput, void *pNextPointer) |

| | Set a buffer pointer (input or output) directly. More...

|

| |

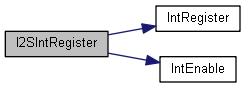

| static void | I2SIntRegister (uint32_t ui32Base, void(*pfnHandler)(void)) |

| | Registers an interrupt handler for an I2S interrupt in the dynamic interrupt table. More...

|

| |

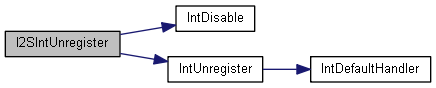

| static void | I2SIntUnregister (uint32_t ui32Base) |

| | Unregisters an interrupt handler for a I2S interrupt in the dynamic interrupt table. More...

|

| |

| void | I2SSampleStampConfigure (uint32_t ui32Base, bool bInput, bool bOutput) |

| | Configure the sample stamp generator. More...

|

| |

| static void | I2SIntEnable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| | Enables individual I2S interrupt sources. More...

|

| |

| static void | I2SIntDisable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| | Disables individual I2S interrupt sources. More...

|

| |

| static uint32_t | I2SIntStatus (uint32_t ui32Base, bool bMasked) |

| | Gets the current interrupt status. More...

|

| |

| static void | I2SIntClear (uint32_t ui32Base, uint32_t ui32IntFlags) |

| | Clears I2S interrupt sources. More...

|

| |

| static void | I2SSampleStampEnable (uint32_t ui32Base) |

| | Enable the Sample Stamp generator. More...

|

| |

| static void | I2SSampleStampDisable (uint32_t ui32Base) |

| | Disable the Sample Stamp generator. More...

|

| |

| uint32_t | I2SSampleStampGet (uint32_t ui32Base, uint32_t ui32Channel) |

| | Get the current value of a sample stamp counter. More...

|

| |

| static void | I2SStart (uint32_t ui32Base, uint8_t ui8FixDMALength) |

| | Starts the I2S. More...

|

| |

| static void | I2SStop (uint32_t ui32Base) |

| | Stops the I2S module for operation. More...

|

| |

| static void | I2SFormatConfigure (uint32_t ui32Base, uint8_t ui8iDataDelay, uint8_t ui8iMemory24Bits, uint8_t ui8iSamplingEdge, bool boolDualPhase, uint8_t ui8BitsPerSample, uint16_t ui16transmissionDelay) |

| | Configure the serial format of the I2S module. More...

|

| |

| static void | I2SFrameConfigure (uint32_t ui32Base, uint8_t ui8StatusAD0, uint8_t ui8ChanAD0, uint8_t ui8StatusAD1, uint8_t ui8ChanAD1) |

| | Setup the two interfaces SD0 and SD1 (also called AD0 and AD1). More...

|

| |

| static void | I2SWclkConfigure (uint32_t ui32Base, bool boolMaster, bool boolWCLKInvert) |

| | Configure the I2S frame clock (also called WCLK or WS). More...

|

| |

| static void | I2SInPointerSet (uint32_t ui32Base, uint32_t ui32NextPointer) |

| | Set the input buffer pointer. More...

|

| |

| static void | I2SOutPointerSet (uint32_t ui32Base, uint32_t ui32NextPointer) |

| | Set the output buffer pointer. More...

|

| |

| static uint32_t | I2SInPointerNextGet (uint32_t ui32Base) |

| | Get value stored in PTR NEXT IN register. More...

|

| |

| static uint32_t | I2SOutPointerNextGet (uint32_t ui32Base) |

| | Get value stored in PTR NEXT OUT register. More...

|

| |

| static uint32_t | I2SInPointerGet (uint32_t ui32Base) |

| | Get value stored in PTR IN register. More...

|

| |

| static uint32_t | I2SOutPointerGet (uint32_t ui32Base) |

| | Get value stored in PTR OUT register. More...

|

| |

| static void | I2SSampleStampInConfigure (uint32_t ui32Base, uint16_t ui16TrigValue) |

| | Configure the IN sample stamp generator. More...

|

| |

| static void | I2SSampleStampOutConfigure (uint32_t ui32Base, uint16_t ui16TrigValue) |

| | Configure the OUT sample stamp generator. More...

|

| |

| static void | I2SWclkCounterConfigure (uint32_t ui32Base, int16_t i16Value) |

| | Add the specified value to the WCLK count. More...

|

| |

| static void | I2SWclkCounterReset (uint32_t ui32Base) |

| | Reset the WCLK count. More...

|

| |

Introduction

The I2S API provides a set of functions for using the I2S module. This module provides a standardized serial interface to transfer audio samples from and to external audio devices such as a codec, DAC, or ADC.

The I2S module has the following features:

- Audio clock signals are internally generated by the PRCM module or externally by another device.

- One or two data pins, which can be configured independently as input or output

- Various data formats according to the settings of the module

- Up to two channels per data pin for dual phase formats and up to eight channels per data pin for single phase formats

- DMA with double-buffered pointers

- Error detection for DMA and audio clock signal integrity

- A Samplestamp generator that allows maintaining of constant audio latency

The I2S module is configured through the functions I2SFormatConfigure(), I2SFrameConfigure() and I2SWclkConfigure(). Transfers are enabled using I2SStart(). Transfers are disabled using I2SStop(). Please note that a specific procedure exists in order to disable transfers without losing data (refer to I2SStop()).

Data are transmitted using the two double-buffered pointers. For each interface, two registers are set with the address of the data to transfer. These registers are named INPTR and INPTRNEXT for the input interface and OUTPTR and OUTPTRNEXT for the output. When PTR is consumed, the hardware copies the content of PTRNEXT into PTR and the next transfer begins. The address of the next value to write or to read in memory (i.e. to receive or to send out) is set using I2SInPointerSet() and I2SOutPointerSet(). The values contented by INPTRNEXT, OUTPTRNEXT, INPTR and OUTPTR can be read using I2SInPointerNextGet(), I2SOutPointerNextGet(), I2SInPointerGet() and I2SOutPointerGet() functions.

Interrupts can help the user to refresh pointers on time. Interrupts can also be used to detect I2S errors. I2SIntEnable() and I2SIntDisable() activate and deactivate interrupt(s). Interrupt status can be read through I2SIntStatus() and a pending interrupt can be acquitted by I2SIntClear() function.

The sample stamps generator can be configured to slightly delay the emission or the reception of the data (based on the number of WCLK cycles) using I2SSampleStampInConfigure(), I2SSampleStampOutConfigure(), I2SWclkCounterReset() and I2SWclkCounterConfigure(). The current sample stamp can be computed using I2SSampleStampGet(). To finish, the sample stamps generator can be enable and disable using the following functions: I2SSampleStampEnable() and I2SSampleStampDisable(). The sample stamps generator must be enabled prior to any transfer.

Note: Other functions contained in the PRCM API are required to handle I2S.

API

Two APIs are coexisting. It is recommended to only use the new API as the old one is deprecated and will be removed soon.

New API: Functions to perform I2S configuration:

Functions to perform transfers:

Functions to handle interruptions:

Functions to handle sample stamps

Old API: I2SEnable(), I2SDisable(), I2SAudioFormatConfigure(), I2SChannelConfigure(), I2SClockConfigure(), I2SBufferConfig(), I2SIntEnable(), I2SIntDisable(), I2SIntStatus(), I2SIntClear(), I2SSampleStampEnable(), I2SSampleStampDisable(), I2SSampleStampGet(), I2SPointerSet (), I2SPointerUpdate(), I2SSampleStampConfigure(), I2SIntRegister(), I2SIntUnregister()

| void I2SAudioFormatConfigure |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32FmtCfg, |

|

|

uint32_t |

ui32BitClkDelay |

|

) |

| |

Configures the I2S module.

- Deprecated:

- This function will be removed in a future release.

The word length defines the size of the word transmitted on the data lines. For single phased formats I2S_WORD_LENGTH_x is the exact number of bits per word. In dual phased format this is the maximum number of bits per word. The size is set using I2S_WORD_LENGTH_8, I2S_WORD_LENGTH_16 or I2S_WORD_LENGTH_24.

- Parameters

-

| ui32Base | is the I2S module base address. |

| ui32FmtCfg | is the bitwise OR of several options:

- Sample size:

- Clock edge sampling:

- Phase:

- Word length:

|

| ui32BitClkDelay | defines the bit clock delay by setting the number of bit clock periods between the positive word clock edge and the MSB of the first word in a phase. The bit clock delay is determined by the ratio between the bit clock and the frame clock and the chosen audio format. The bit clock delay must be configured depending on the chosen audio format:

- 0 : Left Justified Format (LJF).

- 1 : I2S and DSP format.

- 2-255 : Right Justified format (RJF).

|

- Returns

- None

- See also

- I2SChannelConfigure()

110 ASSERT(I2SBaseValid(ui32Base));

111 ASSERT(ui32BitClkDelay <= 255);

#define I2S_MEM_LENGTH_24

Definition: i2s.h:217

uint16_t ui16MemLen

Length of the audio words stored in memory.

Definition: i2s.h:125

#define ASSERT(expr)

Definition: debug.h:73

I2SControlTable * g_pControlTable

Definition: i2s.c:71

| void I2SBufferConfig |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32InBufBase, |

|

|

uint32_t |

ui32OutBufBase, |

|

|

uint16_t |

ui16DMABufSize, |

|

|

uint16_t |

ui16ChanBufSize |

|

) |

| |

Set the input buffer pointers.

- Deprecated:

- This function will be removed in a future release.

The next pointer should always be written while the DMA is using the previous written pointer. If not written in time an I2S_INT_PTR_ERR will occur and all outputs will be disabled.

- Note

- At startup the next data pointer should be written just before and just after calling the I2SEnable().

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| ui32InBufBase | is the address of the input buffer. |

| ui32OutBufBase | is the address of the output buffer. |

| ui16DMABufSize | is the size of the DMA buffers. Must be greater than 0! |

| ui16ChanBufSize | is the size of the channel buffers. |

- Returns

- None

219 ASSERT(I2SBaseValid(ui32Base));

220 ASSERT(ui16DMABufSize > 0);

uint16_t ui16DMABufSize

Size of DMA buffer in number of samples.

Definition: i2s.h:121

uint32_t ui32OutBase

Base address of the output buffer.

Definition: i2s.h:128

#define ASSERT(expr)

Definition: debug.h:73

uint32_t ui32InBase

Base address of the input buffer.

Definition: i2s.h:126

I2SControlTable * g_pControlTable

Definition: i2s.c:71

uint16_t ui16ChBufSize

Size of Channel buffer.

Definition: i2s.h:122

| void I2SChannelConfigure |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32Chan0Cfg, |

|

|

uint32_t |

ui32Chan1Cfg |

|

) |

| |

Setup the audio channel configuration.

- Deprecated:

- This function will be removed in a future release.

The channel configuration is a bitwise OR of the input/output mode of each data line and the active audio channels within a specific audio frame.

Setting up the input/output mode use one of:

For dual phased audio (LJF,RJF,I2S) only mono and stereo modes are allowed. For single phased audio format (DSP) up to 8 active channels are allowed on a single data line. For setting up the active channels in a frame use:

- Single phased, use a bitwise OR'ed combination of:

- Dual phased, use one of:

- Note

- The audio format and the clock configuration should be set using I2SAudioFormatConfigure()

- Parameters

-

| ui32Base | is base address of the I2S module. |

| ui32Chan0Cfg | defines the channel configuration for data line 0. |

| ui32Chan1Cfg | defines the channel configuration for data line 1. |

- Returns

- None

- See also

- I2SAudioFormatConfigure()

130 uint32_t ui32OutChan;

131 uint32_t ui32ChanMask;

134 ASSERT(I2SBaseValid(ui32Base));

156 if(ui32ChanMask & 0x1)

169 if(ui32ChanMask & 0x1)

179 if(ui32Chan1Cfg & I2S_LINE_INPUT)

183 if(ui32ChanMask & 0x1)

191 else if(ui32Chan1Cfg & I2S_LINE_OUTPUT)

195 if(ui32ChanMask & 0x1)

#define I2S_LINE_MASK

Definition: i2s.h:180

#define I2S_CHAN_CFG_MASK

Definition: i2s.h:199

#define I2S_LINE_INPUT

Definition: i2s.h:178

uint8_t ui8InChan

Input Channel.

Definition: i2s.h:123

#define ASSERT(expr)

Definition: debug.h:73

uint8_t ui8OutChan

Output Channel.

Definition: i2s.h:124

#define I2S_LINE_OUTPUT

Definition: i2s.h:179

I2SControlTable * g_pControlTable

Definition: i2s.c:71

| static void I2SClockConfigure |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32ClkConfig |

|

) |

| |

|

inlinestatic |

Configure the I2S frame clock.

- Deprecated:

- This function will be removed in a future release.

Configure I2S clock to be either internal or external and either normal or inverted.

- Note

- The bit clock configuration is done externally, but the internal/ external setting must match what is chosen internally in the I2S module for the frame clock.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| ui32ClkConfig | is the clock configuration parameter. Bitwise OR'ed combination of clock source and clock polarity:

- Clock source:

- Clock polarity:

|

- Returns

- None

458 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SDisable |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Disables the I2S module for operation.

- Deprecated:

- This function will be removed in a future release.

This function will immediately disable the I2S module. To ensure that all buffer operations are completed before shutting down, the correct procedure is:

- Do not update the data pointers using I2SPointerUpdate().

- Await next interrupt resulting in I2S_INT_PTR_ERR.

- Disable the I2S using I2SDisable() and clear the pointer error using I2SIntClear().

- Disable bit clock source (done externally).

- Parameters

-

| ui32Base | is the I2S module base address. |

- Returns

- None

327 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| void I2SEnable |

( |

uint32_t |

ui32Base | ) |

|

Enables the I2S module for operation.

- Deprecated:

- This function will be removed in a future release.

- Note

- The module should only be enabled after configuration. When the module is disabled, no data or clocks will be generated on the I2S signals.

-

Immediately after enabling the module the programmer should update the DMA data pointer registers using I2SPointerUpdate() to ensure a new pointer is written before the DMA transfer completes. Failure to update the pointer in time will result in an I2S_INT_PTR_ERR.

- Parameters

-

| ui32Base | is the I2S module base address. |

- Returns

- None

82 ASSERT(I2SBaseValid(ui32Base));

uint16_t ui16DMABufSize

Size of DMA buffer in number of samples.

Definition: i2s.h:121

uint32_t ui32InOffset

Value of the current input pointer offset.

Definition: i2s.h:127

uint32_t ui32OutOffset

Value of the current output pointer offset.

Definition: i2s.h:129

uint32_t ui32OutBase

Base address of the output buffer.

Definition: i2s.h:128

#define ASSERT(expr)

Definition: debug.h:73

uint32_t ui32InBase

Base address of the input buffer.

Definition: i2s.h:126

I2SControlTable * g_pControlTable

Definition: i2s.c:71

| static void I2SFormatConfigure |

( |

uint32_t |

ui32Base, |

|

|

uint8_t |

ui8iDataDelay, |

|

|

uint8_t |

ui8iMemory24Bits, |

|

|

uint8_t |

ui8iSamplingEdge, |

|

|

bool |

boolDualPhase, |

|

|

uint8_t |

ui8BitsPerSample, |

|

|

uint16_t |

ui16transmissionDelay |

|

) |

| |

|

inlinestatic |

Configure the serial format of the I2S module.

The word length defines the size of the word transmitted on the data lines. For single phased formats ui8BitsPerSample is the exact number of bits per word. In dual phased format this is the maximum number of bits per word.

- Parameters

-

| ui32Base | is the I2S module base address. |

| ui8iDataDelay | is the number of BCLK periods between the first WCLK edge and the MSB of the first audio channel data transferred during the phase. |

| ui8iMemory24Bits | selects if the samples in memory are coded on 16 bits or 24 bits. Possible values are:

|

| ui8iSamplingEdge | selects if sampling on falling or rising edges. Possible values are:

|

| boolDualPhase | must be set to true for dual phase and to false for single phase and user-defined phase. |

| ui8BitsPerSample | is the number of bits transmitted for each sample. If this number does not match with the memory length selected (16 bits or24 bits), samples will be truncated or padded. |

| ui16transmissionDelay | is the number of WCLK periods before the first transmission. |

- Returns

- None

- See also

- I2SFrameConfigure()

966 ASSERT(I2SBaseValid(ui32Base));

967 ASSERT(ui8BitsPerSample <= I2S_AIFFMTCFG_WORD_LEN_MAX);

968 ASSERT(ui8BitsPerSample >= I2S_AIFFMTCFG_WORD_LEN_MIN);

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SFrameConfigure |

( |

uint32_t |

ui32Base, |

|

|

uint8_t |

ui8StatusAD0, |

|

|

uint8_t |

ui8ChanAD0, |

|

|

uint8_t |

ui8StatusAD1, |

|

|

uint8_t |

ui8ChanAD1 |

|

) |

| |

|

inlinestatic |

Setup the two interfaces SD0 and SD1 (also called AD0 and AD1).

This function sets interface's direction and activated channels.

- Parameters

-

| ui32Base | is base address of the I2S module. |

| ui8StatusAD0 | defines the usage of AD0 0x00: AD0 is disabled 0x01, AD0 is an input 0x02, AD0 is an output |

| ui8ChanAD0 | defines the channel mask for AD0. Use a bitwise OR'ed combination of:

|

| ui8StatusAD1 | defines the usage of AD1 0x00: AD1 is disabled 0x10, AD1 is an input 0x20, AD1 is an output |

| ui8ChanAD1 | defines the channel mask for AD1. Use a bitwise OR'ed combination of:

|

- Returns

- None

- See also

- I2SFormatConfigure()

1029 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static uint32_t I2SInPointerGet |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Get value stored in PTR IN register.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

- Returns

- the value of PTR IN.

1186 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static uint32_t I2SInPointerNextGet |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Get value stored in PTR NEXT IN register.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

- Returns

- the value of PTR NEXT IN.

1149 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SInPointerSet |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32NextPointer |

|

) |

| |

|

inlinestatic |

Set the input buffer pointer.

The next pointer should always be written while the DMA is using the previous written pointer. If not written in time an I2S_INT_PTR_ERR will occur and all inputs and outputs will be disabled. This function relies on pointer is pointing to a valid address.

- Note

- It is recommended that the pointer update is done in an interrupt context to ensure that the update is performed before the buffer is full.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| ui32NextPointer | is the adress of the data |

- Returns

- None

- See also

- I2SOutPointerSet()

1102 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SIntClear |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32IntFlags |

|

) |

| |

|

inlinestatic |

Clears I2S interrupt sources.

The specified I2S interrupt sources are cleared, so that they no longer assert. This function must be called in the interrupt handler to keep the interrupt from being recognized again immediately upon exit.

- Note

- Due to write buffers and synchronizers in the system it may take several clock cycles from a register write clearing an event in a module and until the event is actually cleared in the NVIC of the system CPU. It is recommended to clear the event source early in the interrupt service routine (ISR) to allow the event clear to propagate to the NVIC before returning from the ISR. At the same time, an early event clear allows new events of the same type to be pended instead of ignored if the event is cleared later in the ISR. It is the responsibility of the programmer to make sure that enough time has passed before returning from the ISR to avoid false re-triggering of the cleared event. A simple, although not necessarily optimal, way of clearing an event before returning from the ISR is:

- Write to clear event (interrupt source). (buffered write)

- Dummy read from the event source module. (making sure the write has propagated)

- Wait two system CPU clock cycles (user code or two NOPs). (allowing cleared event to propagate through any synchronizers)

- Parameters

-

| ui32Base | is the base address of the I2S port. |

| ui32IntFlags | is a bit mask of the interrupt sources to be cleared. The parameter is the bitwise OR of any of the following:

|

- Returns

- None

797 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SIntDisable |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32IntFlags |

|

) |

| |

|

inlinestatic |

Disables individual I2S interrupt sources.

This function disables the indicated I2S interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

- Parameters

-

| ui32Base | is the base address of the I2S port. |

| ui32IntFlags | is the bit mask of the interrupt sources to be disabled. The parameter is the bitwise OR of any of the following:

|

- Returns

- None.

707 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SIntEnable |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32IntFlags |

|

) |

| |

|

inlinestatic |

Enables individual I2S interrupt sources.

This function enables the indicated I2S interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

- Parameters

-

| ui32Base | is the base address of the I2S port. |

| ui32IntFlags | is the bit mask of the interrupt sources to be enabled. The parameter is the bitwise OR of any of the following:

|

- Returns

- None.

675 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SIntRegister |

( |

uint32_t |

ui32Base, |

|

|

void(*)(void) |

pfnHandler |

|

) |

| |

|

inlinestatic |

Registers an interrupt handler for an I2S interrupt in the dynamic interrupt table.

- Deprecated:

- This function will be removed in a future release.

- Note

- Only use this function if you want to use the dynamic vector table (in SRAM)!

This function registers a function as the interrupt handler for a specific interrupt and enables the corresponding interrupt in the interrupt controller.

Specific I2S interrupts must be enabled via I2SIntEnable(). It is the interrupt handler's responsibility to clear the interrupt source.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| pfnHandler | is a pointer to the function to be called when the I2S interrupt occurs. |

- Returns

- None

- See also

- IntRegister() for important information about registering interrupt handlers.

585 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

void IntRegister(uint32_t ui32Interrupt, void(*pfnHandler)(void))

Registers a function as an interrupt handler in the dynamic vector table.

Definition: interrupt.c:153

void IntEnable(uint32_t ui32Interrupt)

Enables an interrupt or system exception.

Definition: interrupt.c:283

| static uint32_t I2SIntStatus |

( |

uint32_t |

ui32Base, |

|

|

bool |

bMasked |

|

) |

| |

|

inlinestatic |

Gets the current interrupt status.

This function returns the interrupt status for the specified I2S. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

- Parameters

-

| ui32Base | is the base address of the I2S port |

| bMasked | selects between raw and masked interrupt status:

false : Raw interrupt status is required.true : Masked interrupt status is required.

|

- Returns

- Returns the current interrupt status as a vector of:

741 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SIntUnregister |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Unregisters an interrupt handler for a I2S interrupt in the dynamic interrupt table.

- Deprecated:

- This function will be removed in a future release.

This function does the actual unregistering of the interrupt handler. It clears the handler to be called when an I2S interrupt occurs. This function also masks off the interrupt in the interrupt controller so that the interrupt handler no longer is called.

- Parameters

-

| ui32Base | is the base address of the I2S port. |

- Returns

- None

- See also

- IntRegister() for important information about registering interrupt handlers.

619 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

void IntUnregister(uint32_t ui32Interrupt)

Unregisters an interrupt handler in the dynamic vector table.

Definition: interrupt.c:189

void IntDisable(uint32_t ui32Interrupt)

Disables an interrupt or system exception.

Definition: interrupt.c:327

| static uint32_t I2SOutPointerGet |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Get value stored in PTR OUT register.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

- Returns

- the value of PTR OUT.

1204 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static uint32_t I2SOutPointerNextGet |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Get value stored in PTR NEXT OUT register.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

- Returns

- the value of PTR NEXT OUT.

1168 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SOutPointerSet |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32NextPointer |

|

) |

| |

|

inlinestatic |

Set the output buffer pointer.

The next pointer should always be written while the DMA is using the previous written pointer. If not written in time an I2S_INT_PTR_ERR will occur and all inputs and outputs will be disabled. This function relies on pointer is pointing to a valid address.

- Note

- It is recommended that the pointer update is done in an interrupt context to ensure that the update is performed before the buffer is full.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| ui32NextPointer | is the adress of the data |

- Returns

- None

- See also

- I2SInPointerSet()

1131 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| void I2SPointerSet |

( |

uint32_t |

ui32Base, |

|

|

bool |

bInput, |

|

|

void * |

pNextPointer |

|

) |

| |

Set a buffer pointer (input or output) directly.

- Deprecated:

- This function will be removed in a future release.

This function allows bypassing of the pointers in the global control table.

The next pointer should always be written while the DMA is using the previous written pointer. If not written in time an I2S_INT_PTR_ERR will occur and all outputs will be disabled. Nothing is preventing the pointers from being identical, but this function relies on both pointers (input or output pointers) are pointing to a valid address.

- Note

- It is recommended that the pointer update is done in an interrupt context to ensure that the update is performed before the buffer is full.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| bInput | determines whether to update input or output pointer.

true : Update input pointer.false : Update output pointer

|

| pNextPointer | is a void pointer to user defined buffer. |

- Returns

- None

- See also

- I2SPointerUpdate()

238 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| void I2SPointerUpdate |

( |

uint32_t |

ui32Base, |

|

|

bool |

bInput |

|

) |

| |

Update the buffer pointers.

- Deprecated:

- This function will be removed in a future release.

The next pointer should always be written while the DMA is using the previous written pointer. If not written in time an I2S_INT_PTR_ERR will occur and all outputs will be disabled. Nothing is preventing the pointers from being identical, but this function relies on both pointers (input or output pointers) are pointing to a valid address.

- Note

- It is recommended that the pointer update is done in an interrupt context to ensure that the update is performed before the buffer is full.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| bInput | determines whether to update input or output pointer.

true : Update input pointer.false : Update output pointer

|

- Returns

- None

- See also

- I2SPointerSet()

259 uint32_t ui32NextPtr;

262 ASSERT(I2SBaseValid(ui32Base));

uint16_t ui16DMABufSize

Size of DMA buffer in number of samples.

Definition: i2s.h:121

uint32_t ui32InOffset

Value of the current input pointer offset.

Definition: i2s.h:127

uint32_t ui32OutOffset

Value of the current output pointer offset.

Definition: i2s.h:129

uint32_t ui32OutBase

Base address of the output buffer.

Definition: i2s.h:128

uint16_t ui16MemLen

Length of the audio words stored in memory.

Definition: i2s.h:125

uint8_t ui8InChan

Input Channel.

Definition: i2s.h:123

#define ASSERT(expr)

Definition: debug.h:73

uint32_t ui32InBase

Base address of the input buffer.

Definition: i2s.h:126

uint8_t ui8OutChan

Output Channel.

Definition: i2s.h:124

I2SControlTable * g_pControlTable

Definition: i2s.c:71

uint16_t ui16ChBufSize

Size of Channel buffer.

Definition: i2s.h:122

| void I2SSampleStampConfigure |

( |

uint32_t |

ui32Base, |

|

|

bool |

bInput, |

|

|

bool |

bOutput |

|

) |

| |

Configure the sample stamp generator.

- Deprecated:

- This function will be removed in a future release.

Use this function to configure the sample stamp generator.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| bInput | enables triggering of the sample stamp generator on input. |

| bOutput | enables triggering of the sample stamp generator on output. |

- Returns

- None

298 uint32_t ui32Trigger;

301 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

I2SControlTable * g_pControlTable

Definition: i2s.c:71

uint16_t ui16ChBufSize

Size of Channel buffer.

Definition: i2s.h:122

| static void I2SSampleStampDisable |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Disable the Sample Stamp generator.

Use this function to disable the sample stamp generators. When the sample stamp generator is disabled, the clock counters are automatically cleared.

- Returns

- None

841 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SSampleStampEnable |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Enable the Sample Stamp generator.

Use this function to enable the sample stamp generators.

- Note

- It is the user's responsibility to ensure that the sample stamp generator is properly configured before it is enabled. It is the setting of the Input and Output triggers configured using I2SSampleStampConfigure() that triggers the start point of the audio streams.

- Returns

- None

821 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| uint32_t I2SSampleStampGet |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32Channel |

|

) |

| |

Get the current value of a sample stamp counter.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| ui32Channel | is the sample stamp counter to sample |

- Returns

- Returns the current value of the selected sample stamp channel.

328 uint32_t ui32FrameClkCnt;

329 uint32_t ui32SysClkCnt;

330 uint32_t ui32PeriodSysClkCnt;

331 uint32_t ui32SampleStamp;

343 ui32SampleStamp = (ui32SysClkCnt << 16) / ui32PeriodSysClkCnt;

346 ui32SampleStamp |= (ui32FrameClkCnt << 16);

348 return (ui32SampleStamp);

#define I2S_STMP_SATURATION

Definition: i2s.h:235

| static void I2SSampleStampInConfigure |

( |

uint32_t |

ui32Base, |

|

|

uint16_t |

ui16TrigValue |

|

) |

| |

|

inlinestatic |

Configure the IN sample stamp generator.

Use this function to configure the sample stamp generator.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| ui16TrigValue | value used to set the trigger. |

- Returns

- None

1225 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SSampleStampOutConfigure |

( |

uint32_t |

ui32Base, |

|

|

uint16_t |

ui16TrigValue |

|

) |

| |

|

inlinestatic |

Configure the OUT sample stamp generator.

Use this function to configure the sample stamp generator.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| ui16TrigValue | value used to set the trigger. |

- Returns

- None

1247 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SStart |

( |

uint32_t |

ui32Base, |

|

|

uint8_t |

ui8FixDMALength |

|

) |

| |

|

inlinestatic |

Starts the I2S.

I2S must be configured before it is started.

- Note

- Immediately after enabling the module the programmer must update the DMA data pointer registers using I2SInPointerSet() and I2SOutPointerSet() to ensure a new pointer is written before the DMA transfer completes. Failure to update the pointer in time will result in an I2S_INT_PTR_ERR.

- Parameters

-

| ui32Base | is the I2S module base address. |

| ui8FixDMALength | is the length of the DMA buffer: this will allow the DMA to read ui8FixDMALength between to pointer refreshes. |

- Returns

- None

- See also

- I2SStop()

884 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SStop |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

| static void I2SWclkConfigure |

( |

uint32_t |

ui32Base, |

|

|

bool |

boolMaster, |

|

|

bool |

boolWCLKInvert |

|

) |

| |

|

inlinestatic |

Configure the I2S frame clock (also called WCLK or WS).

Configure WCLK clock to be either internal (master) or external (slave). Configure WCLK clock either normal or inverted.

- Note

- The bit clock configuration is done externally, but the internal/ external setting must match what is chosen internally in the I2S module for the frame clock.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| boolMaster | false: the device is a slave (external clock) true: the device is a master (internal clock) |

| boolWCLKInvert | false: WCLK is not inverted true: WCLK is internally inverted |

- Returns

- None

1065 ASSERT(I2SBaseValid(ui32Base));

1070 uint8_t ui8ClkSource = (uint8_t)boolMaster + 0x01;

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SWclkCounterConfigure |

( |

uint32_t |

ui32Base, |

|

|

int16_t |

i16Value |

|

) |

| |

|

inlinestatic |

Add the specified value to the WCLK count.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

| i16Value | is the offset to add to the counter (this value can be negative) |

- Returns

- None

1266 uint16_t ui16MinusValue;

1269 ASSERT(I2SBaseValid(ui32Base));

1277 ui16MinusValue = (uint16_t)(-i16Value);

#define ASSERT(expr)

Definition: debug.h:73

| static void I2SWclkCounterReset |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Reset the WCLK count.

- Parameters

-

| ui32Base | is the base address of the I2S module. |

- Returns

- None

1295 ASSERT(I2SBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| #define I2S_CHAN0_ACT 0x00000100 |

| #define I2S_CHAN0_MASK 0x00000001 |

| #define I2S_CHAN1_ACT 0x00000200 |

| #define I2S_CHAN1_MASK 0x00000002 |

| #define I2S_CHAN2_ACT 0x00000400 |

| #define I2S_CHAN2_MASK 0x00000004 |

| #define I2S_CHAN3_ACT 0x00000800 |

| #define I2S_CHAN3_MASK 0x00000008 |

| #define I2S_CHAN4_ACT 0x00001000 |

| #define I2S_CHAN4_MASK 0x00000010 |

| #define I2S_CHAN5_ACT 0x00002000 |

| #define I2S_CHAN5_MASK 0x00000020 |

| #define I2S_CHAN6_ACT 0x00004000 |

| #define I2S_CHAN6_MASK 0x00000040 |

| #define I2S_CHAN7_ACT 0x00008000 |

| #define I2S_CHAN7_MASK 0x00000080 |

| #define I2S_CHAN_CFG_MASK 0x0000FF00 |

| #define I2S_DMA_BUF_SIZE_128 0x00000080 |

| #define I2S_DMA_BUF_SIZE_256 0x00000100 |

| #define I2S_DMA_BUF_SIZE_64 0x00000040 |

| #define I2S_DUAL_PHASE_FMT 0x00000020 |

| #define I2S_EXT_WCLK 0x00000001 |

| #define I2S_INT_ALL 0x0000003F |

| #define I2S_INT_BUS_ERR 0x00000004 |

| #define I2S_INT_DMA_IN 0x00000020 |

| #define I2S_INT_DMA_OUT 0x00000010 |

| #define I2S_INT_PTR_ERR 0x00000001 |

| #define I2S_INT_TIMEOUT 0x00000008 |

| #define I2S_INT_WCLK 0x00000002 |

| #define I2S_INT_WCLK_ERR 0x00000002 |

| #define I2S_INVERT_WCLK 0x00000004 |

| #define I2S_LINE_INPUT 0x00000001 |

| #define I2S_LINE_MASK 0x00000003 |

| #define I2S_LINE_OUTPUT 0x00000002 |

| #define I2S_LINE_UNUSED 0x00000000 |

| #define I2S_MEM_LENGTH_16 0x00000000 |

| #define I2S_MEM_LENGTH_24 0x00000080 |

| #define I2S_MONO_MODE 0x00000100 |

| #define I2S_NEG_EDGE 0x00000000 |

| #define I2S_NORMAL_WCLK 0x00000000 |

| #define I2S_POS_EDGE 0x00000040 |

| #define I2S_SINGLE_PHASE_FMT 0x00000000 |

| #define I2S_STEREO_MODE 0x00000300 |

| #define I2S_STMP0 0x00000001 |

| #define I2S_STMP1 0x00000002 |

| #define I2S_STMP_SATURATION 0x0000FFFF |

| #define I2S_WORD_LENGTH_16 0x00000010 |

| #define I2S_WORD_LENGTH_24 0x00000018 |

| #define I2S_WORD_LENGTH_8 0x00000008 |