|

| void | I2CMasterInitExpClk (uint32_t ui32Base, uint32_t ui32I2CClk, bool bFast) |

| | Initializes the I2C Master block. More...

|

| |

| static void | I2CMasterControl (uint32_t ui32Base, uint32_t ui32Cmd) |

| | Controls the state of the I2C Master module. More...

|

| |

| static void | I2CMasterSlaveAddrSet (uint32_t ui32Base, uint8_t ui8SlaveAddr, bool bReceive) |

| | Sets the address that the I2C Master will place on the bus. More...

|

| |

| static void | I2CMasterEnable (uint32_t ui32Base) |

| | Enables the I2C Master block. More...

|

| |

| static void | I2CMasterDisable (uint32_t ui32Base) |

| | Disables the I2C master block. More...

|

| |

| static bool | I2CMasterBusy (uint32_t ui32Base) |

| | Indicates whether or not the I2C Master is busy. More...

|

| |

| static bool | I2CMasterBusBusy (uint32_t ui32Base) |

| | Indicates whether or not the I2C bus is busy. More...

|

| |

| static uint32_t | I2CMasterDataGet (uint32_t ui32Base) |

| | Receives a byte that has been sent to the I2C Master. More...

|

| |

| static void | I2CMasterDataPut (uint32_t ui32Base, uint8_t ui8Data) |

| | Transmits a byte from the I2C Master. More...

|

| |

| uint32_t | I2CMasterErr (uint32_t ui32Base) |

| | Gets the error status of the I2C Master module. More...

|

| |

| static void | I2CMasterIntEnable (uint32_t ui32Base) |

| | Enables the I2C Master interrupt. More...

|

| |

| static void | I2CMasterIntDisable (uint32_t ui32Base) |

| | Disables the I2C Master interrupt. More...

|

| |

| static void | I2CMasterIntClear (uint32_t ui32Base) |

| | Clears I2C Master interrupt sources. More...

|

| |

| static bool | I2CMasterIntStatus (uint32_t ui32Base, bool bMasked) |

| | Gets the current I2C Master interrupt status. More...

|

| |

| static void | I2CSlaveEnable (uint32_t ui32Base) |

| | Enables the I2C Slave block. More...

|

| |

| static void | I2CSlaveInit (uint32_t ui32Base, uint8_t ui8SlaveAddr) |

| | Initializes the I2C Slave block. More...

|

| |

| static void | I2CSlaveAddressSet (uint32_t ui32Base, uint8_t ui8SlaveAddr) |

| | Sets the I2C slave address. More...

|

| |

| static void | I2CSlaveDisable (uint32_t ui32Base) |

| | Disables the I2C slave block. More...

|

| |

| static uint32_t | I2CSlaveStatus (uint32_t ui32Base) |

| | Gets the I2C Slave module status. More...

|

| |

| static uint32_t | I2CSlaveDataGet (uint32_t ui32Base) |

| | Receives a byte that has been sent to the I2C Slave. More...

|

| |

| static void | I2CSlaveDataPut (uint32_t ui32Base, uint8_t ui8Data) |

| | Transmits a byte from the I2C Slave. More...

|

| |

| static void | I2CSlaveIntEnable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| | Enables individual I2C Slave interrupt sources. More...

|

| |

| static void | I2CSlaveIntDisable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| | Disables individual I2C Slave interrupt sources. More...

|

| |

| static void | I2CSlaveIntClear (uint32_t ui32Base, uint32_t ui32IntFlags) |

| | Clears I2C Slave interrupt sources. More...

|

| |

| static uint32_t | I2CSlaveIntStatus (uint32_t ui32Base, bool bMasked) |

| | Gets the current I2C Slave interrupt status. More...

|

| |

| void | I2CIntRegister (uint32_t ui32Base, void(*pfnHandler)(void)) |

| | Registers an interrupt handler for the I2C module in the dynamic interrupt table. More...

|

| |

| void | I2CIntUnregister (uint32_t ui32Base) |

| | Unregisters an interrupt handler for the I2C module in the dynamic interrupt table. More...

|

| |

Introduction

The Inter-Integrated Circuit (I2C) API provides a set of functions for using the CC26xx I2C master and slave module. Functions are provided to perform the following actions:

- Initialize the I2C module.

- Send and receive data.

- Obtain status.

- Manage interrupts for the I2C module.

The I2C master and slave module provide the ability to communicate to other IC devices over an I2C bus. The I2C bus is specified to support devices that can both transmit and receive (write and read) data. Also, devices on the I2C bus can be designated as either a master or a slave. The CC26xx I2C module supports both sending and receiving data as either a master or a slave, and also support the simultaneous operation as both a master and a slave. Finally, the CC26xx I2C module can operate at two speeds: standard (100 kb/s) and fast (400 kb/s).

The master and slave I2C module can generate interrupts. The I2C master module generates interrupts when a transmit or receive operation completes (or aborts due to an error). The I2C slave module can generate interrupts when data is sent or requested by a master and when a START or STOP condition is present.

Master Operations

When using this API to drive the I2C master module, the user must first initialize the I2C master module with a call to I2CMasterInitExpClk(). This function sets the bus speed and enables the master module.

The user may transmit or receive data after the successful initialization of the I2C master module. Data is transferred by first setting the slave address using I2CMasterSlaveAddrSet(). This function is also used to define whether the transfer is a send (a write to the slave from the master) or a receive (a read from the slave by the master). Then, if connected to an I2C bus that has multiple masters, the CC26xx I2C master must first call I2CMasterBusBusy() before trying to initiate the desired transaction. After determining that the bus is not busy, if trying to send data, the user must call the I2CMasterDataPut() function. The transaction can then be initiated on the bus by calling the I2CMasterControl() function with any of the following commands:

Any of these commands result in the master arbitrating for the bus, driving the start sequence onto the bus, and sending the slave address and direction bit across the bus. The remainder of the transaction can then be driven using either a polling or interrupt-driven method.

For the single send and receive cases, the polling method involves looping on the return from I2CMasterBusy(). Once the function indicates that the I2C master is no longer busy, the bus transaction is complete and can be checked for errors using I2CMasterErr(). If there are no errors, then the data has been sent or is ready to be read using I2CMasterDataGet(). For the burst send and receive cases, the polling method also involves calling the I2CMasterControl() function for each byte transmitted or received (using either the I2C_MASTER_CMD_BURST_SEND_CONT or I2C_MASTER_CMD_BURST_RECEIVE_CONT commands), and for the last byte sent or received (using either the I2C_MASTER_CMD_BURST_SEND_FINISH or I2C_MASTER_CMD_BURST_RECEIVE_FINISH commands).

If any error is detected during the burst transfer, the appropriate stop command (I2C_MASTER_CMD_BURST_SEND_ERROR_STOP or I2C_MASTER_CMD_BURST_RECEIVE_ERROR_STOP) should be used to call the I2CMasterControl() function.

For the interrupt-driven transaction, the user must register an interrupt handler for the I2C devices and enable the I2C master interrupt; the interrupt occurs when the master is no longer busy.

Slave Operations

When using this API to drive the I2C slave module, the user must first initialize the I2C slave module with a call to I2CSlaveInit(). This function enables the I2C slave module and initializes the address of the slave. After the initialization completes, the user may poll the slave status using I2CSlaveStatus() to determine if a master requested a send or receive operation. Depending on the type of operation requested, the user can call I2CSlaveDataPut() or I2CSlaveDataGet() to complete the transaction. Alternatively, the I2C slave can handle transactions using an interrupt handler registered with I2CIntRegister(), and by enabling the I2C slave interrupt.

API

The I2C API is broken into three groups of functions: those that handle status and initialization, those that deal with sending and receiving data, and those that deal with interrupts.

Status and initialization functions for the I2C module are:

Sending and receiving data from the I2C module is handled by the following functions:

The I2C master and slave interrupts are handled by the following functions:

| void I2CIntRegister |

( |

uint32_t |

ui32Base, |

|

|

void(*)(void) |

pfnHandler |

|

) |

| |

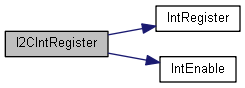

Registers an interrupt handler for the I2C module in the dynamic interrupt table.

- Note

- Only use this function if you want to use the dynamic vector table (in SRAM)!

This function registers a function as the interrupt handler for a specific interrupt and enables the corresponding interrupt in the interrupt controller.

Specific I2C interrupts must be enabled via I2CMasterIntEnable() and I2CSlaveIntEnable(). If necessary, it is the interrupt handler's responsibility to clear the interrupt source via I2CMasterIntClear() and I2CSlaveIntClear().

- Parameters

-

| ui32Base | is the base address of the I2C Master module. |

| pfnHandler | is a pointer to the function to be called when the I2C interrupt occurs. |

- Returns

- None

- See also

- IntRegister() for important information about registering interrupt handlers.

139 ASSERT(I2CBaseValid(ui32Base));

142 ui32Int = INT_I2C_IRQ;

#define ASSERT(expr)

Definition: debug.h:73

void IntRegister(uint32_t ui32Interrupt, void(*pfnHandler)(void))

Registers a function as an interrupt handler in the dynamic vector table.

Definition: interrupt.c:153

void IntEnable(uint32_t ui32Interrupt)

Enables an interrupt or system exception.

Definition: interrupt.c:283

| void I2CIntUnregister |

( |

uint32_t |

ui32Base | ) |

|

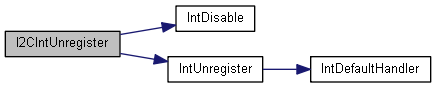

Unregisters an interrupt handler for the I2C module in the dynamic interrupt table.

This function will clear the handler to be called when an I2C interrupt occurs. This will also mask off the interrupt in the interrupt controller so that the interrupt handler no longer is called.

- Parameters

-

| ui32Base | is the base address of the I2C Master module. |

- Returns

- None

- See also

- IntRegister() for important information about registering interrupt handlers.

162 ASSERT(I2CBaseValid(ui32Base));

165 ui32Int = INT_I2C_IRQ;

#define ASSERT(expr)

Definition: debug.h:73

void IntUnregister(uint32_t ui32Interrupt)

Unregisters an interrupt handler in the dynamic vector table.

Definition: interrupt.c:189

void IntDisable(uint32_t ui32Interrupt)

Disables an interrupt or system exception.

Definition: interrupt.c:327

| static bool I2CMasterBusBusy |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Indicates whether or not the I2C bus is busy.

This function returns an indication of whether or not the I2C bus is busy. This function can be used in a multi-master environment to determine if another master is currently using the bus.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

- Returns

- Returns status of the I2C bus:

true : I2C bus is busy.false : I2C bus is not busy.

376 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static bool I2CMasterBusy |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Indicates whether or not the I2C Master is busy.

This function returns an indication of whether or not the I2C Master is busy transmitting or receiving data.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

- Returns

- Returns status of I2C Master:

true : I2C Master is busy.false : I2C Master is not busy.

344 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CMasterControl |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32Cmd |

|

) |

| |

|

inlinestatic |

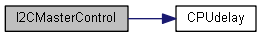

Controls the state of the I2C Master module.

This function is used to control the state of the Master module send and receive operations.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

| ui32Cmd | is the command to be issued by the I2C Master module The parameter can be one of the following values:

|

- Returns

- None

227 ASSERT(I2CBaseValid(ui32Base));

#define I2C_MASTER_CMD_BURST_SEND_START

Definition: i2c.h:102

#define I2C_MASTER_CMD_BURST_SEND_ERROR_STOP

Definition: i2c.h:108

#define I2C_MASTER_CMD_SINGLE_SEND

Definition: i2c.h:98

#define I2C_MASTER_CMD_BURST_RECEIVE_CONT

Definition: i2c.h:112

#define ASSERT(expr)

Definition: debug.h:73

#define I2C_MASTER_CMD_BURST_SEND_FINISH

Definition: i2c.h:106

#define I2C_MASTER_CMD_BURST_SEND_CONT

Definition: i2c.h:104

#define I2C_MASTER_CMD_BURST_RECEIVE_FINISH

Definition: i2c.h:114

#define I2C_MASTER_CMD_BURST_RECEIVE_START

Definition: i2c.h:110

#define I2C_MASTER_CMD_BURST_RECEIVE_ERROR_STOP

Definition: i2c.h:116

void CPUdelay(uint32_t ui32Count)

Provide a small non-zero delay using a simple loop counter.

Definition: cpu.c:343

| static uint32_t I2CMasterDataGet |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Receives a byte that has been sent to the I2C Master.

This function reads a byte of data from the I2C Master Data Register.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

- Returns

- Returns the byte received from by the I2C Master, cast as an uint32_t.

405 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CMasterDataPut |

( |

uint32_t |

ui32Base, |

|

|

uint8_t |

ui8Data |

|

) |

| |

|

inlinestatic |

Transmits a byte from the I2C Master.

This function will place the supplied data into I2C Master Data Register.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

| ui8Data | is the data to be transmitted by the I2C Master |

- Returns

- None

427 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CMasterDisable |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Disables the I2C master block.

This will disable operation of the I2C master block.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

- Returns

- None

317 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CMasterEnable |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Enables the I2C Master block.

This will enable operation of the I2C Master block.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

- Returns

- None

Referenced by I2CMasterInitExpClk().

293 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| uint32_t I2CMasterErr |

( |

uint32_t |

ui32Base | ) |

|

Gets the error status of the I2C Master module.

This function is used to obtain the error status of the Master module send and receive operations.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

- Returns

- Returns the error status of the Master module:

105 ASSERT(I2CBaseValid(ui32Base));

#define I2C_MASTER_ERR_NONE

Definition: i2c.h:124

#define ASSERT(expr)

Definition: debug.h:73

| void I2CMasterInitExpClk |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32I2CClk, |

|

|

bool |

bFast |

|

) |

| |

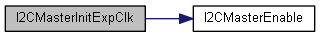

Initializes the I2C Master block.

This function initializes operation of the I2C Master block. Upon successful initialization of the I2C block, this function will have set the bus speed for the master, and will have enabled the I2C Master block.

If the parameter bFast is true, then the master block will be set up to transfer data at 400 kbps; otherwise, it will be set up to transfer data at 100 kbps.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

| ui32I2CClk | is the rate of the clock supplied to the I2C module. |

| bFast | set up for fast data transfers. |

- Returns

- None

71 ASSERT(I2CBaseValid(ui32Base));

90 ui32TPR = ((ui32I2CClk + (2 * 10 * ui32SCLFreq) - 1) / (2 * 10 * ui32SCLFreq)) - 1;

static void I2CMasterEnable(uint32_t ui32Base)

Enables the I2C Master block.

Definition: i2c.h:290

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CMasterIntClear |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Clears I2C Master interrupt sources.

The I2C Master interrupt source is cleared, so that it no longer asserts. This must be done in the interrupt handler to keep it from being called again immediately upon exit.

- Note

- Due to write buffers and synchronizers in the system it may take several clock cycles from a register write clearing an event in a module and until the event is actually cleared in the NVIC of the system CPU. It is recommended to clear the event source early in the interrupt service routine (ISR) to allow the event clear to propagate to the NVIC before returning from the ISR. At the same time, an early event clear allows new events of the same type to be pended instead of ignored if the event is cleared later in the ISR. It is the responsibility of the programmer to make sure that enough time has passed before returning from the ISR to avoid false re-triggering of the cleared event. A simple, although not necessarily optimal, way of clearing an event before returning from the ISR is:

- Write to clear event (interrupt source). (buffered write)

- Dummy read from the event source module. (making sure the write has propagated)

- Wait two system CPU clock cycles (user code or two NOPs). (allowing cleared event to propagate through any synchronizers)

- Parameters

-

| ui32Base | is the base address of the I2C module. |

- Returns

- None

525 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CMasterIntDisable |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Disables the I2C Master interrupt.

Disables the I2C Master interrupt source.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

- Returns

- None

487 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CMasterIntEnable |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Enables the I2C Master interrupt.

Enables the I2C Master interrupt source.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

- Returns

- None

466 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static bool I2CMasterIntStatus |

( |

uint32_t |

ui32Base, |

|

|

bool |

bMasked |

|

) |

| |

|

inlinestatic |

Gets the current I2C Master interrupt status.

This returns the interrupt status for the I2C Master module. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

- Parameters

-

| ui32Base | is the base address of the I2C Master module. |

| bMasked | selects either raw or masked interrupt status.

false : Raw interrupt status is requested.true : Masked interrupt status is requested.

|

- Returns

- Returns the current interrupt status.

true : Active.false : Not active.

553 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CMasterSlaveAddrSet |

( |

uint32_t |

ui32Base, |

|

|

uint8_t |

ui8SlaveAddr, |

|

|

bool |

bReceive |

|

) |

| |

|

inlinestatic |

Sets the address that the I2C Master will place on the bus.

This function will set the address that the I2C Master will place on the bus when initiating a transaction. When the bReceive parameter is set to true, the address will indicate that the I2C Master is initiating a read from the slave; otherwise the address will indicate that the I2C Master is initiating a write to the slave.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

| ui8SlaveAddr | is a 7-bit slave address |

| bReceive | flag indicates the type of communication with the slave.

true : I2C Master is initiating a read from the slave.false : I2C Master is initiating a write to the slave.

|

- Returns

- None

271 ASSERT(I2CBaseValid(ui32Base));

272 ASSERT(!(ui8SlaveAddr & 0x80));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CSlaveAddressSet |

( |

uint32_t |

ui32Base, |

|

|

uint8_t |

ui8SlaveAddr |

|

) |

| |

|

inlinestatic |

Sets the I2C slave address.

This function writes the specified slave address.

- Parameters

-

| ui32Base | is the base address of the I2C Slave module. |

| ui8SlaveAddr | is the 7-bit slave address |

- Returns

- None.

638 ASSERT(I2CBaseValid(ui32Base));

639 ASSERT(!(ui8SlaveAddr & 0x80));

#define ASSERT(expr)

Definition: debug.h:73

| static uint32_t I2CSlaveDataGet |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Receives a byte that has been sent to the I2C Slave.

This function reads a byte of data from the I2C Slave Data Register.

- Parameters

-

| ui32Base | is the base address of the I2C Slave module. |

- Returns

- Returns the byte received from by the I2C Slave, cast as an uint32_t.

711 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CSlaveDataPut |

( |

uint32_t |

ui32Base, |

|

|

uint8_t |

ui8Data |

|

) |

| |

|

inlinestatic |

Transmits a byte from the I2C Slave.

This function will place the supplied data into I2C Slave Data Register.

- Parameters

-

| ui32Base | is the base address of the I2C Slave module. |

| ui8Data | data to be transmitted from the I2C Slave. |

- Returns

- None

733 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CSlaveDisable |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Disables the I2C slave block.

This will disable operation of the I2C slave block.

- Parameters

-

| ui32Base | is the base address of the I2C Slave module. |

- Returns

- None

660 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CSlaveEnable |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Enables the I2C Slave block.

This will enable operation of the I2C Slave block.

- Parameters

-

| ui32Base | is the base address of the I2C Slave module. |

- Returns

- None

Referenced by I2CSlaveInit().

582 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CSlaveInit |

( |

uint32_t |

ui32Base, |

|

|

uint8_t |

ui8SlaveAddr |

|

) |

| |

|

inlinestatic |

Initializes the I2C Slave block.

This function initializes operation of the I2C Slave block. Upon successful initialization of the I2C blocks, this function will have set the slave address and have enabled the I2C Slave block.

The parameter ui8SlaveAddr is the value that will be compared against the slave address sent by an I2C master.

- Parameters

-

| ui32Base | is the base address of the I2C Slave module. |

| ui8SlaveAddr | is the 7-bit slave address. |

- Returns

- None

612 ASSERT(I2CBaseValid(ui32Base));

613 ASSERT(!(ui8SlaveAddr & 0x80));

static void I2CSlaveEnable(uint32_t ui32Base)

Enables the I2C Slave block.

Definition: i2c.h:579

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CSlaveIntClear |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32IntFlags |

|

) |

| |

|

inlinestatic |

Clears I2C Slave interrupt sources.

The specified I2C Slave interrupt sources are cleared, so that they no longer assert. This must be done in the interrupt handler to keep it from being called again immediately upon exit.

- Note

- Due to write buffers and synchronizers in the system it may take several clock cycles from a register write clearing an event in a module and until the event is actually cleared in the NVIC of the system CPU. It is recommended to clear the event source early in the interrupt service routine (ISR) to allow the event clear to propagate to the NVIC before returning from the ISR. At the same time, an early event clear allows new events of the same type to be pended instead of ignored if the event is cleared later in the ISR. It is the responsibility of the programmer to make sure that enough time has passed before returning from the ISR to avoid false re-triggering of the cleared event. A simple, although not necessarily optimal, way of clearing an event before returning from the ISR is:

- Write to clear event (interrupt source). (buffered write)

- Dummy read from the event source module. (making sure the write has propagated)

- Wait two system CPU clock cycles (user code or two NOPs). (allowing cleared event to propagate through any synchronizers)

- Parameters

-

| ui32Base | is the base address of the I2C module. |

| ui32IntFlags | is a bit mask of the interrupt sources to be cleared. The parameter is the bitwise OR of any of the following:

|

- Returns

- None

844 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CSlaveIntDisable |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32IntFlags |

|

) |

| |

|

inlinestatic |

Disables individual I2C Slave interrupt sources.

Disables the indicated I2C Slave interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

- Parameters

-

| ui32Base | is the base address of the I2C Slave module. |

| ui32IntFlags | is the bit mask of the interrupt sources to be disabled. The parameter is the bitwise OR of any of the following:

|

- Returns

- None

797 ASSERT(I2CBaseValid(ui32Base));

803 ui32Val &= ~ui32IntFlags;

#define I2C_SLAVE_INT_STOP

Definition: i2c.h:144

#define I2C_SLAVE_INT_START

Definition: i2c.h:145

#define I2C_SLAVE_INT_DATA

Definition: i2c.h:146

#define ASSERT(expr)

Definition: debug.h:73

| static void I2CSlaveIntEnable |

( |

uint32_t |

ui32Base, |

|

|

uint32_t |

ui32IntFlags |

|

) |

| |

|

inlinestatic |

Enables individual I2C Slave interrupt sources.

Enables the indicated I2C Slave interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

- Parameters

-

| ui32Base | is the base address of the I2C module. |

| ui32IntFlags | is the bit mask of the slave interrupt sources to be enabled. The parameter is the bitwise OR of any of the following:

|

- Returns

- None

763 ASSERT(I2CBaseValid(ui32Base));

769 ui32Val |= ui32IntFlags;

#define I2C_SLAVE_INT_STOP

Definition: i2c.h:144

#define I2C_SLAVE_INT_START

Definition: i2c.h:145

#define I2C_SLAVE_INT_DATA

Definition: i2c.h:146

#define ASSERT(expr)

Definition: debug.h:73

| static uint32_t I2CSlaveIntStatus |

( |

uint32_t |

ui32Base, |

|

|

bool |

bMasked |

|

) |

| |

|

inlinestatic |

Gets the current I2C Slave interrupt status.

This returns the interrupt status for the I2C Slave module. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

- Parameters

-

| ui32Base | is the base address of the I2C Slave module. |

| bMasked | selects either raw or masked interrupt status.

false : Raw interrupt status is requested.true : Masked interrupt status is requested.

|

- Returns

- Returns the current interrupt status as an OR'ed combination of:

873 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| static uint32_t I2CSlaveStatus |

( |

uint32_t |

ui32Base | ) |

|

|

inlinestatic |

Gets the I2C Slave module status.

This function will return the action requested from a master, if any.

- Parameters

-

| ui32Base | is the base address of the I2C Slave module. |

- Returns

- Returns the status of the I2C Slave module:

689 ASSERT(I2CBaseValid(ui32Base));

#define ASSERT(expr)

Definition: debug.h:73

| #define I2C_MASTER_CMD_BURST_RECEIVE_CONT 0x00000009 |

| #define I2C_MASTER_CMD_BURST_RECEIVE_ERROR_STOP 0x00000004 |

| #define I2C_MASTER_CMD_BURST_RECEIVE_FINISH 0x00000005 |

| #define I2C_MASTER_CMD_BURST_RECEIVE_START 0x0000000b |

| #define I2C_MASTER_CMD_BURST_SEND_CONT 0x00000001 |

| #define I2C_MASTER_CMD_BURST_SEND_ERROR_STOP 0x00000004 |

| #define I2C_MASTER_CMD_BURST_SEND_FINISH 0x00000005 |

| #define I2C_MASTER_CMD_BURST_SEND_START 0x00000003 |

| #define I2C_MASTER_CMD_SINGLE_RECEIVE 0x00000007 |

| #define I2C_MASTER_CMD_SINGLE_SEND 0x00000007 |

| #define I2C_MASTER_ERR_ADDR_ACK 0x00000004 |

| #define I2C_MASTER_ERR_ARB_LOST 0x00000010 |

| #define I2C_MASTER_ERR_DATA_ACK 0x00000008 |

| #define I2C_MASTER_ERR_NONE 0 |

| #define I2C_SLAVE_ACT_NONE 0 |

| #define I2C_SLAVE_ACT_RREQ 0x00000001 |

| #define I2C_SLAVE_ACT_RREQ_FBR 0x00000005 |

| #define I2C_SLAVE_ACT_TREQ 0x00000002 |

| #define I2C_SLAVE_INT_DATA 0x00000001 |

| #define I2C_SLAVE_INT_START 0x00000002 |

| #define I2C_SLAVE_INT_STOP 0x00000004 |