Functions | |

| uint32_t | CRYPTOAesLoadKey (uint32_t *pui32AesKey, uint32_t ui32KeyLocation) |

| Write the key into the Key Ram. More... | |

| uint32_t | CRYPTOAesCbc (uint32_t *pui32MsgIn, uint32_t *pui32MsgOut, uint32_t ui32MsgLength, uint32_t *pui32Nonce, uint32_t ui32KeyLocation, bool bEncrypt, bool bIntEnable) |

| Start an AES-CBC operation (encryption or decryption). More... | |

| uint32_t | CRYPTOAesCbcStatus (void) |

| Check the result of an AES CBC operation. More... | |

| uint32_t | CRYPTOAesEcb (uint32_t *pui32MsgIn, uint32_t *pui32MsgOut, uint32_t ui32KeyLocation, bool bEncrypt, bool bIntEnable) |

| Start an AES-ECB operation (encryption or decryption). More... | |

| uint32_t | CRYPTOAesEcbStatus (void) |

| Check the result of an AES ECB operation. More... | |

| static void | CRYPTOAesEcbFinish (void) |

| Finish the encryption operation by resetting the operation mode. More... | |

| static void | CRYPTOAesCbcFinish (void) |

| Finish the encryption operation by resetting the operation mode. More... | |

| uint32_t | CRYPTOCcmAuthEncrypt (bool bEncrypt, uint32_t ui32AuthLength, uint32_t *pui32Nonce, uint32_t *pui32PlainText, uint32_t ui32PlainTextLength, uint32_t *pui32Header, uint32_t ui32HeaderLength, uint32_t ui32KeyLocation, uint32_t ui32FieldLength, bool bIntEnable) |

| Start CCM operation. More... | |

| uint32_t | CRYPTOCcmAuthEncryptStatus (void) |

| Check the result of an AES CCM operation. More... | |

| uint32_t | CRYPTOCcmAuthEncryptResultGet (uint32_t ui32TagLength, uint32_t *pui32CcmTag) |

| Get the result of an AES CCM operation. More... | |

| uint32_t | CRYPTOCcmInvAuthDecrypt (bool bDecrypt, uint32_t ui32AuthLength, uint32_t *pui32Nonce, uint32_t *pui32CipherText, uint32_t ui32CipherTextLength, uint32_t *pui32Header, uint32_t ui32HeaderLength, uint32_t ui32KeyLocation, uint32_t ui32FieldLength, bool bIntEnable) |

| Start a CCM Decryption and Inverse Authentication operation. More... | |

| uint32_t | CRYPTOCcmInvAuthDecryptStatus (void) |

| Checks CCM decrypt and Inverse Authentication result. More... | |

| uint32_t | CRYPTOCcmInvAuthDecryptResultGet (uint32_t ui32AuthLength, uint32_t *pui32CipherText, uint32_t ui32CipherTextLength, uint32_t *pui32CcmTag) |

| Get the result of the CCM operation. More... | |

| static uint32_t | CRYPTODmaStatus (void) |

| Get the current status of the Crypto DMA controller. More... | |

| void | CRYPTODmaEnable (uint32_t ui32Channels) |

| Enable Crypto DMA operation. More... | |

| void | CRYPTODmaDisable (uint32_t ui32Channels) |

| Disable Crypto DMA operation. More... | |

| static void | CRYPTOIntEnable (uint32_t ui32IntFlags) |

| Enables individual Crypto interrupt sources. More... | |

| static void | CRYPTOIntDisable (uint32_t ui32IntFlags) |

| Disables individual CRYPTO interrupt sources. More... | |

| static uint32_t | CRYPTOIntStatus (bool bMasked) |

| Gets the current interrupt status. More... | |

| static void | CRYPTOIntClear (uint32_t ui32IntFlags) |

| Clears Crypto interrupt sources. More... | |

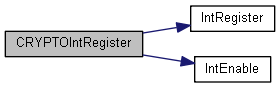

| static void | CRYPTOIntRegister (void(*pfnHandler)(void)) |

| Registers an interrupt handler for a Crypto interrupt in the dynamic interrupt table. More... | |

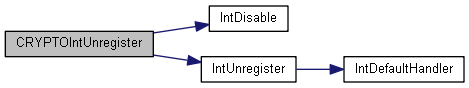

| static void | CRYPTOIntUnregister (void) |

| Unregisters an interrupt handler for a Crypto interrupt in the dynamic interrupt table. More... | |

| uint32_t CRYPTOAesCbc | ( | uint32_t * | pui32MsgIn, |

| uint32_t * | pui32MsgOut, | ||

| uint32_t | ui32MsgLength, | ||

| uint32_t * | pui32Nonce, | ||

| uint32_t | ui32KeyLocation, | ||

| bool | bEncrypt, | ||

| bool | bIntEnable | ||

| ) |

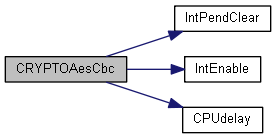

Start an AES-CBC operation (encryption or decryption).

The function starts an AES CBC mode encrypt or decrypt operation. End operation can be detected by enabling interrupt or by polling CRYPTOAesCbcStatus(). Result of operation is returned by CRYPTOAesCbcStatus().

| pui32MsgIn | is a pointer to the input data. |

| pui32MsgOut | is a pointer to the output data. |

| ui32MsgLength | is the length in bytes of the input data. |

| pui32Nonce | is a pointer to 16-byte Nonce. |

| ui32KeyLocation | is the location of the key in Key RAM. This parameter can have any of the following values: |

| bEncrypt | is set true to encrypt or set false to decrypt. |

| bIntEnable | is set true to enable Crypto interrupts or false to disable Crypto interrupt. |

|

inlinestatic |

Finish the encryption operation by resetting the operation mode.

This function should be called after CRYPTOAesCbcStatus() has reported that the operation is finished successfully.

| uint32_t CRYPTOAesCbcStatus | ( | void | ) |

Check the result of an AES CBC operation.

This function should be called after CRYPTOAesCbc() function to check if the AES CBC operation was successful.

| uint32_t CRYPTOAesEcb | ( | uint32_t * | pui32MsgIn, |

| uint32_t * | pui32MsgOut, | ||

| uint32_t | ui32KeyLocation, | ||

| bool | bEncrypt, | ||

| bool | bIntEnable | ||

| ) |

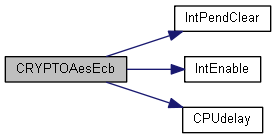

Start an AES-ECB operation (encryption or decryption).

The ui32KeyLocation parameter is an enumerated type which specifies the Key Ram location in which the key is stored.

| pui32MsgIn | is a pointer to the input data. |

| pui32MsgOut | is a pointer to the output data. |

| ui32KeyLocation | is the location of the key in Key RAM. This parameter can have any of the following values: |

| bEncrypt | is set true to encrypt or set false to decrypt. |

| bIntEnable | is set true to enable Crypto interrupts or false to disable Crypto interrupt. |

|

inlinestatic |

Finish the encryption operation by resetting the operation mode.

This function should be called after CRYPTOAesEcbStatus() has reported that the operation is finished successfully.

| uint32_t CRYPTOAesEcbStatus | ( | void | ) |

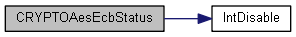

Check the result of an AES ECB operation.

This function should be called after CRYPTOAesEcb() function to check if the AES ECB operation was successful.

Referenced by CRYPTOAesCbcStatus().

| uint32_t CRYPTOAesLoadKey | ( | uint32_t * | pui32AesKey, |

| uint32_t | ui32KeyLocation | ||

| ) |

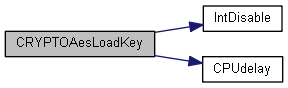

Write the key into the Key Ram.

The ui32KeyLocation parameter is an enumerated type which specifies the Key Ram location in which the key is stored.

The pointer pui8AesKey has the address where the Key is stored.

| pui32AesKey | is a pointer to an AES Key. |

| ui32KeyLocation | is the location of the key in Key RAM. This parameter can have any of the following values: |

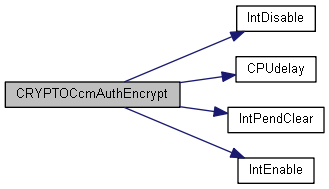

| uint32_t CRYPTOCcmAuthEncrypt | ( | bool | bEncrypt, |

| uint32_t | ui32AuthLength, | ||

| uint32_t * | pui32Nonce, | ||

| uint32_t * | pui32PlainText, | ||

| uint32_t | ui32PlainTextLength, | ||

| uint32_t * | pui32Header, | ||

| uint32_t | ui32HeaderLength, | ||

| uint32_t | ui32KeyLocation, | ||

| uint32_t | ui32FieldLength, | ||

| bool | bIntEnable | ||

| ) |

Start CCM operation.

The ui32KeyLocation is an enumerated type which specifies the Key Ram location in which the key is stored.

| bEncrypt | determines whether to run encryption or not. |

| ui32AuthLength | is the length of the authentication field - 0, 2, 4, 6, 8, 10, 12, 14 or 16 octets. |

| pui32Nonce | is a pointer to 13-byte or 12-byte Nonce (Number used once). |

| pui32PlainText | is a pointer to the octet string input message. |

| ui32PlainTextLength | is the length of the message. |

| pui32Header | is the length of the header (Additional Authentication Data or AAD). |

| ui32HeaderLength | is the length of the header in octets. |

| ui32KeyLocation | is the location in Key RAM where the key is stored. This parameter can have any of the following values: |

| ui32FieldLength | is the size of the length field (2 or 3). |

| bIntEnable | enables interrupts. |

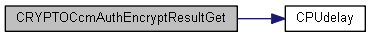

| uint32_t CRYPTOCcmAuthEncryptResultGet | ( | uint32_t | ui32TagLength, |

| uint32_t * | pui32CcmTag | ||

| ) |

Get the result of an AES CCM operation.

This function should be called after CRYPTOCcmAuthEncryptStatus().

| ui32TagLength | is length of the Tag. |

| pui32CcmTag | is the location of the authentication Tag. |

| uint32_t CRYPTOCcmAuthEncryptStatus | ( | void | ) |

Check the result of an AES CCM operation.

This function should be called after CRYPTOCcmAuthEncrypt() function to check if the AES CCM operation was successful.

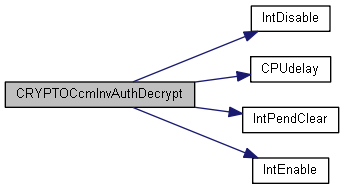

| uint32_t CRYPTOCcmInvAuthDecrypt | ( | bool | bDecrypt, |

| uint32_t | ui32AuthLength, | ||

| uint32_t * | pui32Nonce, | ||

| uint32_t * | pui32CipherText, | ||

| uint32_t | ui32CipherTextLength, | ||

| uint32_t * | pui32Header, | ||

| uint32_t | ui32HeaderLength, | ||

| uint32_t | ui32KeyLocation, | ||

| uint32_t | ui32FieldLength, | ||

| bool | bIntEnable | ||

| ) |

Start a CCM Decryption and Inverse Authentication operation.

The ui32KeyLocation is an enumerated type which specifies the Key Ram location in which the key is stored.

| bDecrypt | determines whether to run decryption or not. |

| ui32AuthLength | is the length of the authentication field - 0, 2, 4, 6, 8, 10, 12, 14 or 16 octets. |

| pui32Nonce | is a pointer to 13-byte or 12-byte Nonce (Number used once). |

| pui32CipherText | is a pointer to the octet string encrypted message. |

| ui32CipherTextLength | is the length of the encrypted message. |

| pui32Header | is the length of the header (Additional Authentication Data or AAD). |

| ui32HeaderLength | is the length of the header in octets. |

| ui32KeyLocation | is the location in Key RAM where the key is stored. This parameter can have any of the following values: |

| ui32FieldLength | is the size of the length field (2 or 3). |

| bIntEnable | enables interrupts. |

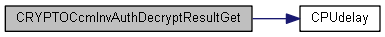

| uint32_t CRYPTOCcmInvAuthDecryptResultGet | ( | uint32_t | ui32AuthLength, |

| uint32_t * | pui32CipherText, | ||

| uint32_t | ui32CipherTextLength, | ||

| uint32_t * | pui32CcmTag | ||

| ) |

Get the result of the CCM operation.

| ui32AuthLength | is the length of the authentication field - 0, 2, 4, 6, 8, 10, 12, 14 or 16 octets. |

| pui32CipherText | is a pointer to the octet string encrypted message. |

| ui32CipherTextLength | is the length of the encrypted message. |

| pui32CcmTag | is the location of the authentication Tag. |

| uint32_t CRYPTOCcmInvAuthDecryptStatus | ( | void | ) |

Checks CCM decrypt and Inverse Authentication result.

| void CRYPTODmaDisable | ( | uint32_t | ui32Channels | ) |

Disable Crypto DMA operation.

The specified Crypto DMA channels are disabled.

| ui32Channels | is a bitwise OR of the channels to disable. |

| void CRYPTODmaEnable | ( | uint32_t | ui32Channels | ) |

Enable Crypto DMA operation.

The specified Crypto DMA channels are enabled.

| ui32Channels | is a bitwise OR of the channels to enable. |

|

inlinestatic |

Get the current status of the Crypto DMA controller.

This function is used to poll the Crypto DMA controller to check if it is ready for a new operation or if an error has occurred.

The CRYPTO_DMA_BUS_ERROR can also be caught using the crypto event handler.

|

inlinestatic |

Clears Crypto interrupt sources.

The specified Crypto interrupt sources are cleared, so that they no longer assert. This function must be called in the interrupt handler to keep the interrupt from being recognized again immediately upon exit.

| ui32IntFlags | is a bit mask of the interrupt sources to be cleared. |

|

inlinestatic |

Disables individual CRYPTO interrupt sources.

This function disables the indicated Crypto interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt. Disabled sources have no effect on the processor.

| ui32IntFlags | is the bitwise OR of the interrupt sources to be enabled. |

|

inlinestatic |

Enables individual Crypto interrupt sources.

This function enables the indicated Crypto interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt. Disabled sources have no effect on the processor.

| ui32IntFlags | is the bitwise OR of the interrupt sources to be enabled. |

|

inlinestatic |

Registers an interrupt handler for a Crypto interrupt in the dynamic interrupt table.

This function registers a function as the interrupt handler for a specific interrupt and enables the corresponding interrupt in the interrupt controller.

Specific UART interrupts must be enabled via CRYPTOIntEnable(). It is the interrupt handler's responsibility to clear the interrupt source.

| pfnHandler | is a pointer to the function to be called when the UART interrupt occurs. |

|

inlinestatic |

Gets the current interrupt status.

This function returns the interrupt status for the specified Crypto. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

| bMasked | whether to use raw or masked interrupt status:

|

|

inlinestatic |

Unregisters an interrupt handler for a Crypto interrupt in the dynamic interrupt table.

This function does the actual unregistering of the interrupt handler. It clears the handler to be called when a Crypto interrupt occurs. This function also masks off the interrupt in the interrupt controller so that the interrupt handler no longer is called.

| #define AES_CCM_TEST_ERROR 10 |

| #define AES_DMA_BSY 11 |

Referenced by CRYPTOAesEcbStatus(), CRYPTOCcmAuthEncryptStatus(), and CRYPTOCcmInvAuthDecryptStatus().

| #define AES_DMA_BUS_ERROR 3 |

| #define AES_ECB_LENGTH 16 |

Referenced by CRYPTOAesEcb().

| #define AES_ECB_TEST_ERROR 8 |

| #define AES_KEYSTORE_READ_ERROR 1 |

Referenced by CRYPTOAesCbc(), CRYPTOAesEcb(), CRYPTOAesLoadKey(), CRYPTOCcmAuthEncrypt(), and CRYPTOCcmInvAuthDecrypt().

| #define AES_KEYSTORE_WRITE_ERROR 2 |

| #define AES_NULL_ERROR 9 |

| #define AES_SUCCESS 0 |

| #define CCM_AUTHENTICATION_FAILED 4 |

Referenced by CRYPTOCcmInvAuthDecryptResultGet().

| #define CRYPTO_AES128_DECRYPT 0x00000008 |

Referenced by CRYPTOAesCbc(), and CRYPTOAesEcb().

| #define CRYPTO_AES128_ENCRYPT 0x0000000C |

Referenced by CRYPTOAesCbc(), and CRYPTOAesEcb().

| #define CRYPTO_AES_CBC 5 |

| #define CRYPTO_AES_CCM 3 |

| #define CRYPTO_AES_CTR_128 0x3 |

Referenced by CRYPTOCcmAuthEncrypt(), and CRYPTOCcmInvAuthDecrypt().

| #define CRYPTO_AES_CTR_32 0x0 |

| #define CRYPTO_AES_CTR_64 0x1 |

| #define CRYPTO_AES_CTR_96 0x2 |

| #define CRYPTO_AES_ECB 2 |

| #define CRYPTO_AES_KEYL0AD 1 |

| #define CRYPTO_AES_NONE 0 |

| #define CRYPTO_AES_RNG 4 |

| #define CRYPTO_DMA_BSY 0x00000003 |

Referenced by CRYPTOAesEcbStatus(), CRYPTOCcmAuthEncryptStatus(), and CRYPTOCcmInvAuthDecryptStatus().

| #define CRYPTO_DMA_BUS_ERR 0x80000000 |

Referenced by CRYPTOCcmAuthEncrypt(), and CRYPTOCcmInvAuthDecrypt().

| #define CRYPTO_DMA_BUS_ERROR 0x00020000 |

Referenced by CRYPTOAesEcbStatus(), CRYPTOCcmAuthEncryptStatus(), and CRYPTOCcmInvAuthDecryptStatus().

| #define CRYPTO_DMA_CHAN0 0x00000001 |

Referenced by CRYPTODmaDisable(), and CRYPTODmaEnable().

| #define CRYPTO_DMA_CHAN1 0x00000002 |

Referenced by CRYPTODmaDisable(), and CRYPTODmaEnable().

| #define CRYPTO_DMA_IN_DONE 0x00000002 |

Referenced by CRYPTOIntClear(), CRYPTOIntDisable(), and CRYPTOIntEnable().

| #define CRYPTO_DMA_READY 0x00000000 |

| #define CRYPTO_IRQTYPE_LEVEL 0x00000001 |

Referenced by CRYPTOAesCbc(), CRYPTOAesEcb(), CRYPTOAesLoadKey(), CRYPTOCcmAuthEncrypt(), CRYPTOCcmInvAuthDecrypt(), and CRYPTOIntEnable().

| #define CRYPTO_IRQTYPE_PULSE 0x00000000 |

| #define CRYPTO_KEY_AREA_0 0 |

Referenced by CRYPTOAesLoadKey().

| #define CRYPTO_KEY_AREA_1 1 |

Referenced by CRYPTOAesLoadKey().

| #define CRYPTO_KEY_AREA_2 2 |

Referenced by CRYPTOAesLoadKey().

| #define CRYPTO_KEY_AREA_3 3 |

Referenced by CRYPTOAesLoadKey().

| #define CRYPTO_KEY_AREA_4 4 |

Referenced by CRYPTOAesLoadKey().

| #define CRYPTO_KEY_AREA_5 5 |

Referenced by CRYPTOAesLoadKey().

| #define CRYPTO_KEY_AREA_6 6 |

Referenced by CRYPTOAesLoadKey().

| #define CRYPTO_KEY_AREA_7 7 |

Referenced by CRYPTOAesLoadKey().

| #define CRYPTO_KEY_ST_RD_ERR 0x20000000 |

Referenced by CRYPTOAesCbc(), CRYPTOAesEcb(), CRYPTOCcmAuthEncrypt(), and CRYPTOCcmInvAuthDecrypt().

| #define CRYPTO_KEY_ST_WR_ERR 0x40000000 |

| #define CRYPTO_RESULT_RDY 0x00000001 |

Referenced by CRYPTOIntClear(), CRYPTOIntDisable(), and CRYPTOIntEnable().

| #define KEY_BLENGTH 16 |

Referenced by CRYPTOAesLoadKey().

| #define KEY_EXP_LENGTH 176 |

| #define KEY_STORE_SIZE_128 0x00000001 |

Referenced by CRYPTOAesLoadKey(), CRYPTOCcmAuthEncrypt(), and CRYPTOCcmInvAuthDecrypt().

| #define KEY_STORE_SIZE_192 0x00000002 |

| #define KEY_STORE_SIZE_256 0x00000003 |

| #define KEY_STORE_SIZE_BITS 0x00000003 |

| #define STATE_BLENGTH 16 |