4.3. FC¶

4.4. IPC¶

IPC technical documents links

| Links | Description |

|---|---|

| IPC User’s Guide | TI IPC User’s Guide |

4.4.1. IPC Examples¶

4.4.1.1. IPC RTOS Examples¶

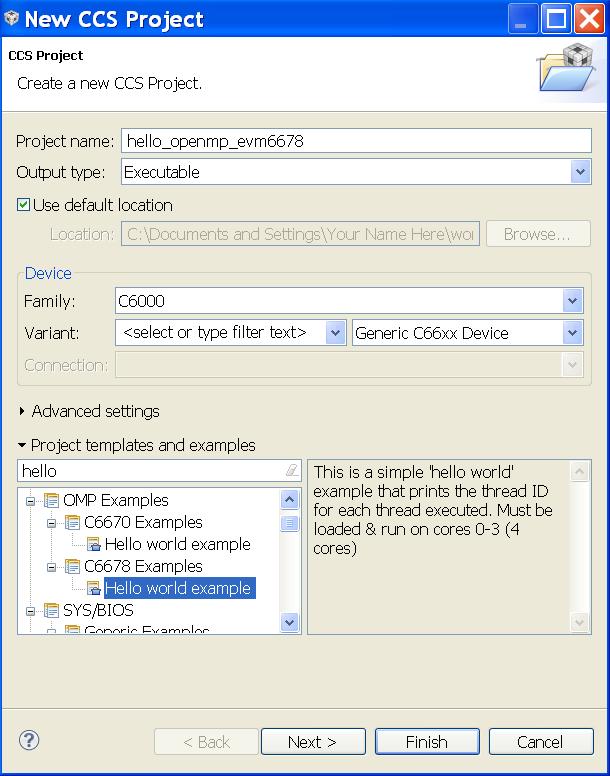

IPC Examples with ARM Host running TI-RTOS

The IPC package includes examples for the use-case with both the Host and slave cores running TI-RTOS. They can be built from the Processor SDK RTOS package.

Note

To Install RTOS Proc SDK, please follow the instructions in the RTOS SDK Getting Started Guide

In the RTOS Processor SDK, the ipc examples are located under <RTOS_SDK_INSTALL_DIR>/processor_sdk_rtos_<platform>_x_xx_xx_xx/ipc_<version>/examples/<platform>_bios_elf.

Once the RTOS Processor SDK is installed at the default location, the IPC examples can be built with the following commands:

Change to Processor SDK RTOS directory

$ cd <RTOS_SDK_INSTALL_DIR>/processor_sdk_rtos_<platform>_x_xx_xx_xx

Start the top level build:

$ make ipc_examples

4.6. Boot¶

4.6.1. Overview¶

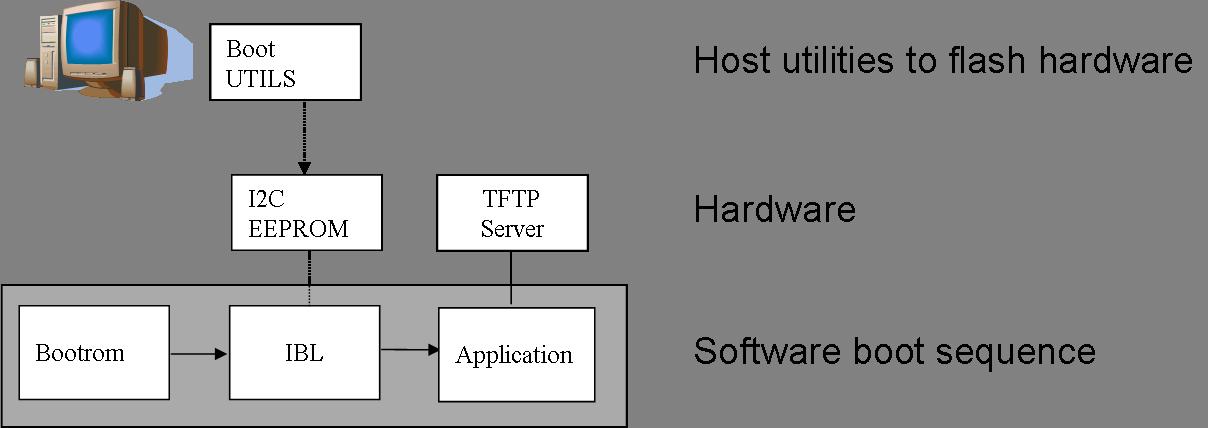

This page provides an overview about the Secondary Bootloader support provided in Processor SDK RTOS.

The Secondary Bootloader (SBL) sets-up the PLL clocks, powers on the I/O Peripherals, initializes the DDR, loads the application image into DDR & brings the slave cores for applicable SOCs out of reset. Additional details including execution boot flow is covered in more elaborate detail under individual SOC section.

4.6.2. Boot Modes¶

4.6.2.1. MMCSD¶

MMCSD bootloader is required to boot target using an SD card containing bootloader and application images. When the board is powered ON the ROM bootloader detects the MMCSD bootloader image and loads it to the internal memory.The bootloader initializes the board, copies the application image from SD card to the DDR memory and gives control to the application.

4.6.2.2. QSPI¶

A flash device interfaced with QSPI is flashed with QSPI bootloader and application images. When the board is powered ON the ROM bootloader detects the bootloader image from flash device and loads it to the internal memory. The Bootloader initializes the board, copies the application image from QSPI device to the DDR memory and gives control to the application.

4.6.2.3. UART¶

A Serial connection is used for transferring the bootloader binary from PC to target board through XMODEM protocol. The bootloader on execution prompts for application image to transfer through XMODEM. On providing the path, the application binary is transferred through serial connection to DDR memory and the control is passed to application to execute.

4.6.2.4. MCSPI/SPI¶

A SPI flash device flashed with MCSPI/SPI bootloader and application images is used for booting the board. When the board is powered ON the ROM bootloader detects the bootloader image from flash device and loads it to the internal memory. The Bootloader initializes the board, copies the application image from flash to the DDR memory and gives control to the application.

4.6.2.5. NAND¶

NAND flash with bootloader and and application images is used for booting the board. When the board is powered ON the ROM bootloader detects the bootloader image from flash device and loads it to the internal memory. The bootloader initializes the board, copies the application image from flash to the DDR memory and gives control to the application.

Note

For information on boot mode setting, see the applicable EVM Hardware User Guide

4.6.3. Platforms¶

4.6.3.1. AM335x/AM437x¶

4.6.3.1.1. Overview¶

Bootloader supports power-on-reset bootstraps for the board. It initializes board, loads application from the memory device to DDR and transfers control to application. Section provides additional details including flashing and booting instructions across different media.

4.6.3.1.2. Source Reference¶

< BASE_DIR = PDK_INSTALL_DIR\packages\ti\starterware>

4.6.3.1.2.1. Bootloader build files for AM335x/AM437x¶

Source files:

- BASE_DIRbootloadersrc: Common source files for bootloader functionality

- BASE_DIRbootloadersrc<device>: Files specific to device to initialize platform features like PLL, pinmux and DDR

Build Files:

- BASE_DIR/build/makerules/rules_a8.mk: Common Compiler flags used for A8 cores. Applies to AMIC110 and AM335x

- BASE_DIR/build/makerules/rules_a8.mk: Common Compiler flags used for A9 cores. Applies to AM437x devices

- BASE_DIR/build/makerules/platform.mk: Global settings for all components for a particular platform.

- BASE_DIR/build/makerules/components.mk: Specific settings for components in starterware

- BASE_DIR/build/makerules/build_cfg.mk: Flags to enable features in the build

- BASE_DIR/bootloader/Makefile: Makefile for bootloader that provides list of source files and library to create bootloader binary.

Boot and flashing tools:

- BASE_DIR/tools Contains tools to create boot images and flashing tools to program the boot binary on the boot media.

4.6.3.1.3. Bootloader execution sequence¶

The Processor SDK RTOS boot loader uses a two stage boot process. The different stages of the application boot sequence using Processor SDK RTOS bootloader are shown below:

4.6.3.1.3.1. Boot Sequence¶

- Power on Reset

- ROM Bootloader (RBL)

- Platform configuration and initialization.

- DPLL and clock settings for MPU, I2C, MMCSD, USB, SPI, QSPI, Ethernet etc.

- Checks Sysboot pins and choose booting device

- If no valid bootloader found on booting device, RBL checks for next booting device. The sequence depends on RBL execution flow and Sysboot pins.

- RBL gets image size and load address by checking TI Image Header appended on bootloader binary(.bin). Check binary formats.

- Loads the binary to internal OCMC memory at the Load address fetched from TI Image Header

- Passes control to Secondary Bootloader(SBL)

- Platform configuration and initialization.

- Secondary Bootloader(SBL)

- Configure PLL and Initialize DDR

- Configure PRCM and PinMux for Boot Peripherals

- Copies application image to DDR

- Passes execution control to Application

- Application execution

4.6.3.1.4. Tools and Binary formats¶

| Binary format | Requirement | Details |

| .bin | QSPI bootloader, UART bootloader and app |

QSPI bootloader binary should in .bin format and Application binary should be in _ti.bin format. UART bootloader and applications are loaded in .bin format through XMODEM in terminal. |

| _ti.bin | MMCSD bootloader and app, NAND bootloader and app, MCSPI boot loader and app, QSPI app. |

.bin binaries are converted to _ti.bin format by adding Image size(4bytes) and Image load address(4bytes) as image header. Refer to Image format section in Initialization chapter of AM437x TRM MMCSD, NAND and MCSPI boot loaders and application binaries should be appended with ti image header. |

TI Boot image

| Offset | Binary value |

|---|---|

| 0x00000000 | Size |

| 0x00000004 | Entry Point (Location) |

| 0x00000008 | Binary (.bin) |

Note

- For bootloader Entry point is usually 0x402f0000

- For the app the entry point is usually 0x80000000.

4.6.3.1.4.1. Binary format conversion procedure¶

4.6.3.1.4.1.1. Binary format conversion in Linux¶

- To convert from .out -> .bin

TOOLCHAIN_PATH_<A8/A9>/bin/arm-none-eabi-objcopy -O binary <application>.out <application>.bin

- Build tiimage.out. Go to starterware/tools/ti_image/

gcc tiimage.c –o tiimage.out

- To convert from .bin -> _ti.bin

tiimage.out <Image Load Address> NONE <application>.bin <application>_ti.bin

4.6.3.1.4.1.2. Binary format conversion in Windows¶

- To convert from .out -> .bin

TOOLCHAIN_PATH_<A8/A9>/bin/arm-none-eabi-objcopy -O binary <application>.out <application>.bin

2) To convert from .bin -> _ti.bin. tiimage.exe is provided as prebuilt binary in starterware/tools/ti_image.

tiimage.exe <Image Load Address> NONE <application>.bin <application>_ti.bin

4.6.3.1.5. Boot Modes supported¶

Following are the Boot Modes supported through AM335x/AM437x bootloader for the various EVMs.

| MMCSD | NAND | McSPI | QSPI | UART | |

| AM335x GPEVM | YES | YES | YES | NO | YES |

| AM335x ICEv2 | YES | NO | YES | NO | NO |

| AM335x StarterKi t | YES | NO | NO | NO | YES |

| AM335x BeagleBon eBlack | YES | NO | NO | NO | YES |

| AM437x GPEVM | YES | NO | NO | NO | YES |

| AM437x IDK | YES | NO | NO | YES | NO |

| AM437x StarterKi t | YES | NO | NO | NO | NO |

4.6.3.1.6. Building the Bootloader¶

- Pre-requisite: Setup SDK build environment as described in article

- Setup_Environment

Normal Operation of Bootloader:

Bootloading an application from flash into DDR memory as in case of TI evaluation platforms is described as normal operation mode for the bootloader. This is the default behaviour of the bootloader and can be built using the following command in starterware.

gmake bootloader BUILDCFG=boot BOOTMODE=<BOOT_MODE> PLATFORM=<EVM> PROFILE=<BUILD_PROFILE> -s KW_BUILD=no

- BOOT_MODE: mcspi, nand, qspi, mmcsd, uart (Check supported boot modes for your evaluation platform)

- EVM: am335x-evm, am43xx-evm, amic110-ddrless

- BUILD_PROFILE: debug, release

Additional Build options (currently support only for AMIC110/AM335x ICE Users)

- DDR less Application boot setup

gmake bootloader BUILDCFG=boot BOOTMODE=mcspi PLATFORM=amic110-ddrless PROFILE=debug -s KW_BUILD=no USE_DDR=no

gmake bootloader BUILDCFG=boot BOOTMODE=mcspi PLATFORM=amic110-ddrless PROFILE=release -s KW_BUILD=no USE_DDR=no

This option builds an ultra light weight (<10 KB) bootloader for cost optimized application that don`t external DDR memory.

- PRU/ICSS Enable in SBL

gmake bootloader BUILDCFG=boot BOOTMODE=mcspi PLATFORM=am335x-evm PROFILE=debug -s KW_BUILD=no ENABLE_PRU=yes

gmake bootloader BUILDCFG=boot BOOTMODE=mcspi PLATFORM=am335x-evm PROFILE=release -s KW_BUILD=no ENABLE_PRU=yes

This feature is required in application that need to quick wake up of ICSS/PRU cores. The PRU cores can be woken up and loaded from the SBL by combining the ENABLE_PRU and BIN_LOAD arguments.

- Load additional binaries from flash

gmake bootloader BUILDCFG=boot BOOTMODE=mcspi PLATFORM=am335x-evm PROFILE=debug -s KW_BUILD=no BIN_LOAD=yes

gmake bootloader BUILDCFG=boot BOOTMODE=mcspi PLATFORM=am335x-evm PROFILE=release -s KW_BUILD=no BIN_LOAD=yes

The location of binaries in offset is configured using sbl_flash_offset_cfg.h in the bootloader source. Users are required to use TIIMAGE tool to append an header to the binary so that the bootloader knows the loction and size of the binary to be loaded.

Industrial DDRless Booting

The AMIC110 DDRLESS platform provides a superset flag to enable all the above features and build the bootloader . The superset build is invoked using BUILD_ICSS_DDRLESS_BOOT=yes as shown below:

gmake bootloader BUILDCFG=boot BOOTMODE=mcspi PLATFORM=amic110-ddrless PROFILE=debug -s KW_BUILD=no BUILD_ICSS_DDRLESS_BOOT=yes

gmake bootloader BUILDCFG=boot BOOTMODE=mcspi PLATFORM=amic110-ddrless PROFILE=release -s KW_BUILD=no BUILD_ICSS_DDRLESS_BOOT=yes

Prebuilt binaries inside the Processor SDK RTOS for AMIC110-DDRLESS will be configured using this option to allow for testing of cost optimized industrial use case.

4.6.3.1.7. Boot Mode settings¶

Boot mode settings for all supported AM335x and AM437x boards are here

4.6.3.1.8. Boot Modes¶

4.6.3.1.8.1. Booting Via SD Card¶

Booting from SD Card involves two steps.

- Preparing SD card.

- Booting target.

4.6.3.1.8.1.1. Preparing SD card¶

- To boot target the SD card should be bootable. Follow the steps at Creating bootable SD card in windows or Creating bootable SD card in Linux.

- Delete the “MLO” and “app” in the bootable SD card which are created in the process of making the SD bootable.

- Bootloader images with ti header (<mmcsd_bootloader>_ti.bin)should be renamed to “MLO”. Bootloader images are located at <PDK_INSTALL_DIRpackagestistarterwarestarterwarebinarybootloaderbin<TargetType>

- Similarly the converted application binary image has to be renamed to “app” from “<app_name>_ti.bin“

- Copy both the boot loader image “MLO” and the application image “app” to the SD card.

- The SD card is ready for use on target.

4.6.3.1.8.1.2. Booting target¶

- Insert SD card to the base board SD slot. Connect a UART cable to a host running a serial terminal application (teraterm/hyperterminal) with 115200 baud, 8bit, No parity and 1 STOP bit configuration.

- Configure the board for SD Boot mode

- SD instance 0 (on base board) is available in all profiles.

- SD instance 0 boot mode needs to appropriately set. For SD boot to be selected first, SD boot should appear first in the boot device list in the boot mode. If any other boot mode is selected, even if a SD boot card is inserted, and does not appear first in the list, the first available sane boot image (like NAND or SPI etc) is booted and SD is not selected. Only if no sane boot image is found in the first devices, SD boot image will be selected.

- Once SD boot image is chosen, the MLO is first detected and copied and executed from the OCMC0 RAM. The MLO then copies the application image (app) from the card to the SDRAM and passes the control to the application. If the process is succesful, messages identifying board and SoC will appear on the serial console.

After this the application will take control and execute.

NOTE: If board have BootMode selection pins choose proper Boot Selection pins from hardware reference manuals.

4.6.3.1.8.2. Booting Via QSPI¶

Booting from QSPI flash involves two steps-

- Preparing Flash Device

- Booting target.

4.6.3.1.8.2.1. Preparing Flash Device¶

Procedure relies on contents being copied to SD card. Additional details below:

- Copy bootloader image(bootloader_boot_qspi_a9host_debug.bin rename) and app image(“<app_name>_ti.bin”) into the SD card. The file names have to be renamed in such a way that the length of name is less than 9 characters. Any file name less than 9 characters can be used. Rename the bootloader file to ‘boot’ and application image to ‘app’ with no extensions.

- Copy the ‘config’ file into the SD card which will contain the names of the image to be flashed and the offset. A sample config file can be found at <PDK_INSTALL_DIRpackagestistarterwarestarterwaretoolsqspiconfig> directory. Do not change name of the config file. NOTE: “config” file can be used without any modifications if bootloader and application images are renamed to “boot” and “app”. NOTE: Do not rename bootloader to be copied to SD card as “MLO”, as MMCSD bootloader expects “MLO” and “app” to boot.

- Now SD card contains 1)boot 2)app 3)config files. config file contains the address of boot image as 0x0 and app image as 0x80000. Insert it into the SD card slot.

- Connect the board with CCS and load the prebuilt qspi flash writer application from <PDK_INSTALL_DIRpackagestistarterwarestarterwarebinaryqspi_app_flash_writerbinm43xx-evm>

- Run the QSPI flash writer application. Following logs expected on console.

StarterWare QSPI Flash Writer!!

BOARDInit status [0x0]

SoC : [AM43XX]

Core : [A9]

Board Detected : [IDKEVM]

Base Board Revision : [UNKNOWN]

Daughter Card Revision: [UNKNOWN]

Copying boot to QSPI Flash

Copying app to QSPI Flash

Changing read to quad mode

Read mode has been changed to Quad mode

SUCCESS!!!

Flashing completed

4.6.3.1.8.2.2. Booting the target.¶

- Connect UART cable to a host running serial terminal application (teraterm/hyperterminal) with 115200 baud, 8bit, No parity and 1 STOP bit configuration.

- After flashing successfully remove SD card and reboot to see following logs

StarterWare Boot Loader

BOARDInit status [0x0]

SoC : [AM43XX]

Core : [A9]

Board Detected : [IDKEVM]

Base Board Revision : [UNKNOWN]

Daughter Card Revision: [UNKNOWN]

Copying Header of the application image

Copying image from flash to DDR

Jumping to StarterWare Application...

NOTE: Boot logs will appear approximately after 25 seconds on reset.

NOTE:If there is no boot mode selection present on board, boot image will be loaded depending on ROM boot sequence

Example: If QSPI flash and MMCSD has valid bootloaders, on reset MMCSD boot image will be loaded following ROM Boot sequence.

4.6.3.1.8.3. Booting Via UART¶

ROM and Bootloader supports XMODEM protocol with images being binary not requiring any additional headers. Following are steps for boot:

- Configure board for UART boot mode :

UART boot need to be first in the boot device list. Note: In case if

any other boot mode is selected, the first available boot image

(eg:NAND or MMCSD etc) will override. In case of no valid images,

UART boot will be selected.

- Select View->Memory Browser through CCS.

- Select address 0x44e10040.

- Write 0x19 to last 2 bytes of this memory address.(UART boot)

- Soft reset the board. This is a volatile bit which gets reset after power on.

- ROM code will print “CC..” on UART console expecting Bootloader via XMODEM. File can be sent via xmodem through tera-term File-> Transfer -> XMODEM -> Send.

- On transmitting bootloader image, bootloader_boot_uart_a9host_debug.bin via XMODEM, following message will be expected on serial console.

CCCCCCCCCCCCCCCCCCCCCCCCCCCC

StarterWare Boot Loader

BOARDInit status [0x0]

SoC : [AM43XX]

Core : [A9]

Board Detected : [IDKEVM]

Base Board Revision : [UNKNOWN]

Daughter Card Revision: [UNKNOWN]

GPIO Instance number: 0

Pin number: 22

Please transfer file:

CCCCCCCCCCCCCCCCCCCCCCCCCCCCCCCCCC

4. As a next step application binary (without header) can be sent via XMODEM which will lead to application start executing.

4.6.3.1.8.4. Booting Via McSPI¶

Booting from McSPI involves two steps.

- Preparing Flash Device

- Booting the target.

Preparing Flash Device

- Set the appropriate bootmode if applicable for EVM.Refer Boot mode settings. Note: Most of the boards may not have switch settings.

- Add a required target configuration in CCS depending on emulator and board connected.

- Connect target to required core. Ex: A8.

- Load the flash writer from <PDK_INSTALL_DIRpackagestistarterwarestarterwaretoolsflash_writerspi_flash_writer_AM335X.out onto the EVM.

- Run the application and observe the logs on CCS console.

Starting SPIWriter.

Choose Operation:

Enter 1 ----> To FLASH an Image

Enter 2 ----> To ERASE Flash

Enter 3 ----> To EXIT

- When Flash option is chosen program prompts to enter file name.

Enter the File Name

- Provide the complete path of file bootloader_boot_mcspi_a8host_release_ti.bin at directory “binary/bootloader/bin/<PLATFORM>/<gcc/ccs>/” and hit Enter.

Enter the Offset in bytes (in HEX)

- Provide 0x00000 to flash bootloader.

- To flash application binary image <app_name>_a8host_ti.bin, provide 0x20000.

- Wait for few miniuits as flashing is a slower process.

Erasing flash at byte offset: xx, byte length: xxxx

SF: Successfully erased xxxx bytes @ xxxx

Writing flash at page offset: x, number of pages: xxxx

Flashing is in progress...

Verifying... Success.

- Once SPI flash writing completes disconnect target.

Booting the target

- Connect a serial cable to a host running a serial terminal application (teraterm/hyperterminal) with 115200 baud, 8bit, No parity and 1 STOP bit configuration.

- Configure the board for SPI boot mode.

- On reset, ROM bootloder copies the bootloader from flash to internal memory. The bootloader then copies the application image from flash to DDR and passes the control to the application.

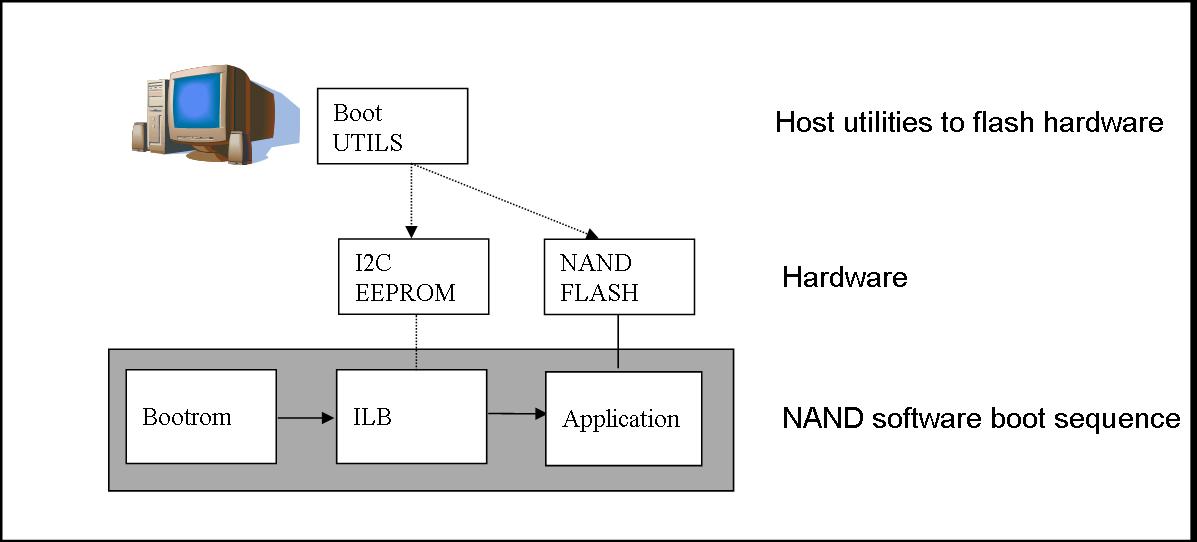

4.6.3.1.8.5. Booting Via NAND¶

Booting from NAND involves two steps.

- Preparing Flash Device

- Booting the target.

Preparing Flash Device

- Configure BOOT pins for NAND Boot mode settings

- Connect target with CCS.

- Load the <PDK_INSTALL_DIRpackagestistarterwarestarterwaretoolsflash_writernand_flash_writer_AM335X.out> to target and Run. Flash writer will output messages to CCS console. When it prompts for inputs, proper inputs shall be given via CCS console.

- When prompted for binary file name, update file with proper path.

- Select option for flashing.

Choose your operation

Enter 1 ---> To Flash an Image

Enter 2 ---> To ERASE the whole NAND

Enter 3 ---> To EXIT

- If Option 1 is selected, enter image path to flash when prompted as shown below.

Enter image file path

Provide the complete path (e.g. <PDK_INSTALL_DIRpackagestistarterwarestarterwarebinarybootloaderbin<am335x/am437x-evm><compiler>bootloader_boot_nand_a8host_<debug/release>_ti.bin)

- Enter offset when prompted as shown below.

Enter offset (in hex):

- Use hex format

- If bootloader is to be flashed, provide 0x00000. For application binary, provide 0x80000.

- Select ECC for flashing.

Choose the ECC scheme from given options

Enter 1 ---> BCH 8 bit

Enter 2 ---> HAM

Enter 3 ---> T0 EXIT

Please enter ECC scheme type:

Always select BCH8 for bootloader and application as ROM code and bootloader uses the BCH8 ECC scheme.

- Ensure that flash info displayed by tool matches NAND flash in EVM.

- After this tool should first erase the required region in flash and then start flashing new image.

- If flashing procedure is complete following message should be displayed.

Application is successfully flashed

NAND flashing successful!

- Once NAND flash writing completes, disconnect from CCS.

Booting the target

- Connect a UART cable to a host running a serial terminal application (teraterm/hyperterminal) with 115200 baud, 8bit, No parity and 1 STOP bit configuration.

- Configure the board for NAND boot mode. Refer Boot mode settings

- On reset, ROM detects bootloader from NAND and copies it to internal memory. Bootloader then copies application image from the NAND to DDR and passes control to application. If the process is succesful, following messages appear in serial console.

StarterWare Boot Loader

BOARDInit status [0x0]

SoC : [AM335X]

Core : [A8]

Board Detected : [GPEVM]

Base Board Revision : [1.5]

Daughter Card Revision: [UNKNOWN]

NAND flash is connected to GPMC on this board

Jumping to StarterWare Application...

After this application should take control and execute.

4.6.3.1.9. Test Application¶

The section explains steps for building and booting a sample pdk application for am335x or am437x using MMCSD bootloader.

4.6.3.1.9.1. Test Application Image Creation¶

Follow below steps to generate the bootable application image.

- Generate .out files using steps for Rebuilding PDK. Locate .out file in directory <PDK_INSTALL_PATH/MyExampleProjects/<ExampleProjectDirectory>/Debug>

- Convert files to support MMCSD boot using steps as per Binary format conversion procedure.

- Rename generated <Application>_ti.bin to “app”.

4.6.3.1.9.2. Loading Test application¶

Follow procedure to use “app” file as per section Booting Via SD Card.

4.6.3.1.10. Usage Notes¶

- Bootloader Memory map

The bootloader code runs from internal OCMC memory and occupies certain amount of OCMC memory that is not available for application to use during booting.

Refer to the map file for the boot loader to check for latest information on the memory utilization in the boot loader.

Location of linker command file:

BASE_DIR\binary\bootloader\bin\<platform>\gcc

After SBL execution is complete, this region can be used as per application requirement.

- Configuring entry point for SBL

The three files that help setup the entry point in the bootloader build are “PDK_INSTALL_PATHpackagestistarterwaresocarmv7agccsbl_init.S” and the linker command file “PDK_INSTALL_PATHpackagestistarterwareexamplesgcc<device>_boot.lds”. The global symbol Entry is used to provide the entry point to the bootloader. The Base address of the memory section OCMCRAM (starts at 1K offset in OCMC RAM as defined in TRM) is then used by the tiimage or GPHEader tool to provide RBL the guidance to find the entry point to pass control. After MLO is created check the TI image format file( _ti.bin) to confirm that the entry point matches the location of Entry symbol in the .map file.

Note

The object file created by sbl_init.S should always be the first object file in the link order for the symbol Entry to be placed at the BASE address of the memory section SBL_MEM

- Boot image creation tools generates a large boot image if load sections are fragmented

Please note that when using objcopy the compiler generates a contiguous binary that gets loaded by the bootloader at the location specified in the header appended by TIIMAGE boot utility. IF you have some code sections in OCMC or SRAM and some section in DDR the compiler will generates a binary that spans across full memory range which would be in order of MB or even GB size so it is recommended that you create compact binaries that can be loaded into memory or implement a ELF parser to bootloader memory sections that may be fragmented in the address space. you can also load separate binaries for OCMC sections and DDR memory and load the sections separately

- Removing Heap section from application binary to speed up boot times

A common issue reported with the ARM GCC compiler is that it appends Heap section associated with the binary to the binary image used to boot. The Heap section is usually filled with zeros so can cause significant delay in boot times. Essentially the bootloader will be writing a bunch of zeros in memory so is inefficient. Following work around has been used to circumvent the issue

Option 1: Eliminate the heap by using the compiler option “–remove-section” as described in the E2E post below:

Refer: E2E post to configure Heap in ARM application binary by adding “–remove-section”

Example BIOS configuration:

var heap1 = HeapMem.create();

heap1.size = 256 * 1024 * 1024;

heap1.sectionName = ".stack";

Memory.defaultHeapInstance = heap1;

Compiler Setting : –remove-section=.stack

Option 2 Configure Segment type to be “NO LOAD” in .cfg and use excludeSections

SYSBIOS Memory map configurations allows user to specify the section name, length and type. by configuring the section type to “NOLOAD” and using excludeSection option the heap memory can be eliminated from the final binary.

Example BIOS configuration:

Program.sectMap[".biosheap"] = new Program.SectionSpec();

Program.sectMap[".biosheap"].runSegment = "DDR2"

Program.sectMap[".biosheap"].type = "NOLOAD";

Program.sectionsExclude = ".biosheap"

Alternate approach using linker command file:

.ddr3Heap (NOLOAD):

{

*(.ddr3Heap)

} > HOST_DDR3

Note

The approach described above helps improve boot times but Users are recommended to initialize the HEAP sections to zeros post boot during initialization to avoid any undesired behavior during normal operation of the app

4.6.3.1.11. Debugging application boot¶

Steps to debug application boot using Processor SDK RTOS bootloader are discussed in the article `Common steps to debug application boot <index_Foundational_Components.html#common-steps-to-debug-application-boot>`__

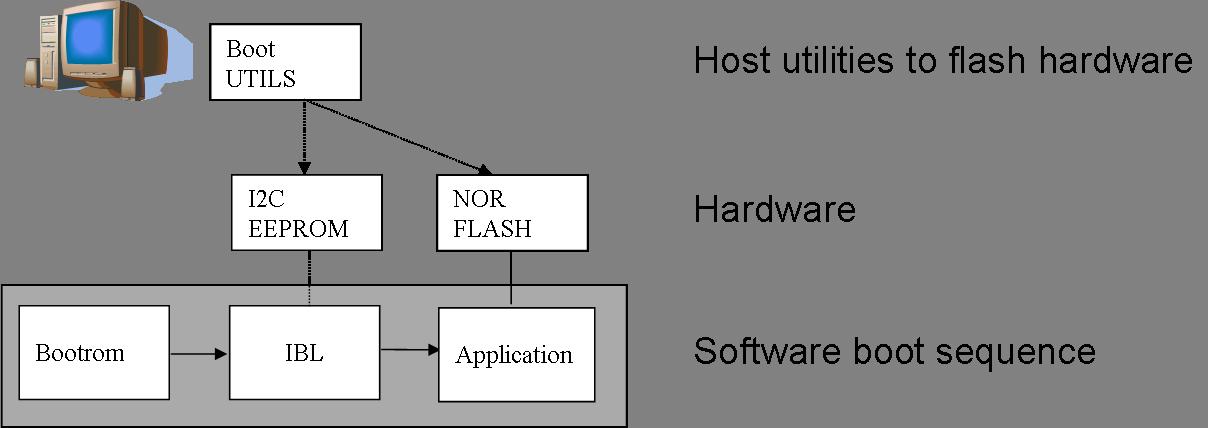

4.6.3.2. AM57x¶

4.6.3.2.1. Overview¶

The Secondary Bootloader (SBL) for AM57xx device initializes the execution environment for multi-core application and this can be used to demonstrate an out-of-box experience.The section covers additional details including execution sequence, tools and additional flashing instructions.

4.6.3.2.2. Bootloader Execution Sequence¶

- Power On Reset

- ROM Bootloader (RBL)

- Software pre-programmed in ROM memory starts executing

- Checks Sysboot pins and choose booting device

- If no valid bootloader found on booting device, RBL checks for next booting device.

- Platform configuration and initialization.

- Configures DPLL and clock settings for MPU, and boot media like I2C, MMCSD, SD/MMC, SPI, QSPI, Ethernet etc for reliable boot.

- The sequence depends on RBL execution flow and Sysboot pins.

- RBL gets image size and load address by checking TI Image Header appended on bootloader binary(.bin). Check binary formats.

- Loads the binary to internal memory at the Load address fetched from TI Image Header

- Passes control to Secondary Bootloader(SBL)

Note

Detailed description of ROM bootloader is provided in Initialization Chapter in AM57xx Technical Reference manual

- Secondary bootloader(SBL)

- User level secondary bootloader(SBL) begins execution from internal memory by running basic initialization routines like setting up Stack, BSS and then jumps to main() to begin Board Initialization.

- Board Initialization is done by a call to Board_init() API.For additional details refer Processor SDK Board Support.

- It includes setting up PLLs, enabling clocks to all interfaces and modules, performing pinmux and setting up UART console.

- Once Board Initialization is complete, it enables clocks to the slave cores like C66x/DSP, IPU, etc and brings them out of reset.

- Parses Multicore Application image located in memory device and copies it to DDR memory based on load address for different sections.

- Once copy is successful it transfers control to application.

- Application then starts executing from DDR.

Note

- RBL requires boot loader to be in a special format with a header appended to the binary image. The header shall contain the load address of the bootloader and size of the bootloader image.

- For more information on the TI header refer TRM document

4.6.3.2.3. Directory structure¶

Makefiles:

- PDK_INSTALL_PATH/ti/boot/sbl/board/<EVAL_BOARD>/build: Makefile for bootloader that provides list of source files and library and compiler options to create bootloader binary.

Source Files:

- PDK_INSTALL_PATH/ti/boot/sbl/board/<EVAL_BOARD>: Source to SBL main function that consolidates all features

- PDK_INSTALL_PATH/ti/boot/sbl/soc: Source to SOC specific initialization used in the SBL.

- PDK_INSTALL_PATH/ti/boot/sbl/src: Source to boot media specific initialization used in the SBL.

4.6.3.2.4. Tools and Binary Formats¶

This section lists out the various tools and scripts used by SBL for different boot modes and those required to create a bootable application image.

SBL/MLO image format: To generate the MLO, SBL uses tiImageGen tool to prepend the sbl.bin image with the TI header information. The image format has been described in detail in the Image Format Section of theAM57xx Technical Reference manual

Application image format: A bootable application image can be created by using the Am57xImageGen script provided under tools folder as part of sbl. It can be located at <PDK_INSTALL_DIR>/packages/ti/boot/sbl/tools/scripts folder.

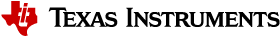

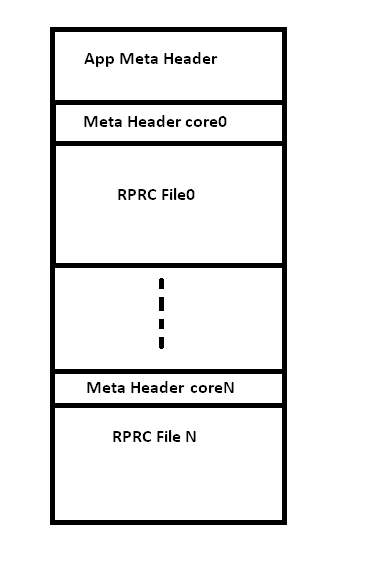

The Am57xImageGen script uses out2rprc and multicoreImageGen format conversion tools to create the final application image. Graphical view of the multicore application image is provided below:

The script creates the bootable image in 2 steps

Step 1: Conversion to RPRC format conversion

- Firstly, application executable is converted from ELF/COFF format (.out) to custom TI Rprc binary image using out2rprc tool. This tool strips out the initialized sections from the executable file (i.e. *.out) and places them in a compact format that the SBL can understand. The output (bin) file is typically much smaller than the original executable (out) file.

- The rprc files are intermediate files in a format that is consumed by MulticoreImageGen tool that generates the final binary.

RPRC File Header Format

| Offset | Binary value |

|---|---|

| 0x00000000 | Magic Word(43525052) |

| 0x00000004 | Entry Point (Location) |

| 0x00000008 | Reserved Addr |

| 0x0000000C | Section Count |

| 0x00000010 | Version |

RPRC Section Header Format

| Offset | Binary value |

|---|---|

| 0x00000000 | Section start Address |

| 0x00000004 | Reserved Addr |

| 0x00000008 | Size |

| 0x0000000C | Reserved CRC |

| 0x00000010 | Reserved |

Step 2: Multicore Image file generation

- RPRC files for each cores is combined into a single multicore bootable application image.

Multicore boot image format

Meta Header Start

| Offset | Binary value |

|---|---|

| 0x00000000 | Magic String (0x5254534D) |

| 0x00000004 | Number of Files |

| 0x00000008 | Device ID |

| 0x0000000C | Reserved |

Meta Header per Core

| Offset | Binary value |

|---|---|

| 0x00000000 | Core ID |

| 0x00000004 | Image Offset |

Core ID and Device ID for specific devices can be located in the file sbl_slave_core_boot.h in the boot/sbl/soc/<SOC_NAME> folder

Refer section App Image Creation for more details on usage of this script and application image creation.

Flashing Tools

SBL provides a CCS based qspi flash writer utility to flash image and multicore AppImage from a SD card to onboard QSPI device. It is located at <PDK_INSTALL_DIR>/packages/ti/boot/sbl/tools/flashWriter/qspi

4.6.3.2.5. Building the SBL¶

Pre-requisites to Building

- Set your environment using pdksetupenv.bat or pdksetupenv.sh. Refer to the Processor SDK RTOS Building page for information on setting up your build environment

- The SBL has following dependencies and will need the following

libraries built

- Board

- UART

- I2C

- SPI

- CSL

- OSAL

- MMCSD

- PM

Note

Refer to the makefile for the board you are using for the latest driver dependency. These libraries should come pre-built with any fresh installation of the Processor SDK RTOS but may be removed if a gmake clean is invoked

Compiling the SBL Components

To build the SBL components:

- cd <PDK>/packages/ti/board/diag

- make all BOARD=<BOARD_NAME> SOC=<SOC_NAME> BOOTMODE=<BOOTMEDIA>

- BOARD_NAME : idkAM572x, idkAM571x, evmAM572x, idkAM574x

- SOC_NAME : AM572x, AM571x, AM574x

This will make the SBL for a specific $BOARD and $BOOT_MEDIA. Output files will be located in: <PDK>/packages/ti/boot/sbl/binary/<BOARD>

Note

Refer <PDK>/packages/ti/boot/sbl/sbl_<DEVICE>.sh for more build options

Boot Modes

This Release of SBL supports MMCSD and QSPI Boot modes. The different boot modes supported for all the boards is tabulated in the table below.

| MMCSD | QSPI | eMMC | |

| AM572x GPEVM | YES | NO | YES |

| AM572x IDKEVM | YES | YES | NO |

| AM571x IDKEVM | YES | YES | NO |

| AM574x IDKEVM | YES | YES | NO |

4.6.3.2.5.1. Booting Via SD Card¶

- Preparing the SD card.

- Booting the target.

4.6.3.2.5.1.1. Preparing the SD card¶

- To boot the target the SD card should be bootable. Follow the steps at Creating bootable SD card in windows or Creating bootable SD card in Linux.

- Delete the “MLO” and “app” in the bootable SD card which are created in the process of making the SD bootable.

- Copy the sbl binary(MLO) to the SD card.

- Copy the Application image(app) generated using the Script to the SD card.

4.6.3.2.5.1.2. Booting the target¶

- Insert micro SD card into the SD card slot of the board.

- Open a serial communication terminal like TeraTerm, MiniCom on host PC and connect to the UART console port

- Do a power reset of the board to boot the appliation from the SD card.

4.6.3.2.5.2. Booting Via eMMC¶

- Preparing the eMMC.

- Booting the target.

4.6.3.2.5.2.1. Preparing the eMMC¶

- To format the eMMC of the target board, Run the following application on the target board USB_DevMsc_mmcsd .

- To boot the target the eMMC should be bootable. Follow the steps same as SD card formatting as given at Creating bootable SD card in windows or Creating bootable SD card in Linux except instead of SD card, connect the target board eMMC to the host PC.

- Delete the “MLO” and “app” in the bootable eMMC which are created in the process of making the eMMC bootable.

- Copy the sbl binary(MLO) to the eMMC.

- Copy the Application image(app) generated using the Script to the eMMC.

4.6.3.2.5.2.2. Booting the target¶

- Set boot settings to eMMC by selecting J3, J4 and J6 jumpers on Pin 2 and 3 of AM572x EVM Board.

- Ensure there is no SD card inserted in the SD card slot.

- Open a serial communication terminal like TeraTerm, MiniCom on host PC and connect to the UART console port

- Do a power reset of the board to boot the appliation from the eMMC.

4.6.3.2.5.3. Booting Via QSPI¶

Booting from QSPI flash involves two steps-

- Flashing bootloader and app image to QSPI flash.

- Booting the target.

4.6.3.2.5.3.1. Preparing Flash Device¶

Use the CCS based qspi_flash_writer.out utility provided in <TI_PDK_INSTALL_DIR>/packages/ti/boot/sbl/tools/flashwriter/qspi/<Board>’ to flash the SBL image at offset 0 and application image at offset 0x80000 to the QSPI device.

QSPI device Memory Map:

| Offset 0x00 | SBL |

| Offset 0x80000 | Application Multicore Image |

The images can be flashed into QSPI flash by following steps given below.

- Copy QSPI mode SBL image TI_PDK_INSTALL_DIRpackagestibootsblbinary<BoardName>qspibinMLO and application image(app) generated using the Script into the SD card. Rename the bootloader file to ‘boot’ and application image to ‘app’ with no extensions.

- Copy ‘config’ file into the SD card, the config file should contain names of the image to be flashed and the offset. A sample config file can be found at TI_PDK_INSTALL_DIRpackagestibootsbltoolsflashWriterqspiconfig. Do not change the name of the config file. NOTE: “config” file can be used without any modifications if bootloader and application images are renamed to “boot” and “app”. NOTE: Do not rename the bootloader to be copied to SD card as “MLO”, as MMCSD bootloader expects “MLO” and “app” to boot.

- Now SD card contains 3 files 1)boot 2)app 3)config files. config file contains the address of boot image as 0x0 and app image as 0x80000. Insert it into the SD card slot.

- Connect the board with CCS and and load the prebuilt qspi flash writer application from $(TI_PDK_INSTALL_DIR)packagestibootsbltoolsflashWriterqspibin<BoardName>\

- Run the QSPI flash writer application. You will see the following logs on the EVM’s UART console.

- After the images have been flashed to the QSPI device disconnect from CCS and do a power reset to boot from the QSPI memory.

PDK QSPI Flash Writer!!

Copying boot to QSPI Flash

Copying app to QSPI Flash

Changing read to quad mode

Read mode has been changed to Quad mode

SUCCESS!!!

Flashing completed

Note

- The file names have to be renamed in such a way that the length of name is less than 9 characters. Any file name less than 9 characters can be used.

- This application will flash the image at required offset without taking into consideration any overwriting to previously flashed image.

- It is the responsibility of the user to provide proper offsets.

4.6.3.2.6. Test Application¶

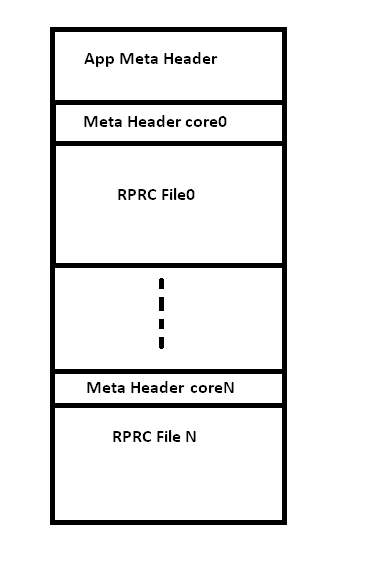

SBL provides a test application to demonstrate booting of multicore application image on A15 and DSP cores.The multicore sample application uses mailbox for inter-processor communication. It is used to validate the multi-core boot-up use case.

Master application sends wake-up message to the DSP slave cores & waits for acknowledgement message from the slave cores in an infinite loop.Each slave DSP core waits for wake-up message from the master core responds back with an acknowledgement message.

4.6.3.2.6.1. Application Image Creation¶

Application Image creation involves two steps.

- Generating the .outs of applications for individual cores

- Combining the .outs of individual cores to create a bootable multicore image

The steps to create the bootable image in Linux and Windows environment are listed below.

Note

- Valid SOC settings are AM571x/AM572x

- Valid BOARD settings are evmAM572x/idkAM571x/idkAM572x

4.6.3.2.6.2. Linux Environment¶

Command to build the test application.

Go to cd (TI_PDK_INSTALL_DIR)\packages\ti\boot\sbl

make example BOARD=<BOARD> SOC=<SOC> to build the application

make example_clean BOARD=<BOARD>

Example:

make example BOARD=idkAM572x SOC=AM572x

To create the final bootable application image use the AM57xImageGen script and follow these steps

1. Set the following environment variable in the shell. BIN_PATH: Pointing to the path where the AppImage needs to be generated

Ex: export BIN_PATH=$(TI_PDK_INSTALL_DIR)/packages/ti/boot/sbl/binary

2. Edit the script file to point to the application elf files by setting the input application variables.

App_MPU_CPU0: Point to the path where the application .out for A15 MPU is located App_DSP1: Point to the path where the dsp core 1 application is located App_DSP2: Point to the path where the dsp core 2 application is located

export APP_MPU_CPU0=$(TI_PDK_INSTALL_DIR)/packages/ti/boot/sbl/binary/idkAM572x/example/armv7/bin/sbl_app.out

export APP_DSP1=$(TI_PDK_INSTALL_DIR)/packages/ti/boot/sbl/binary/idkAM572x/example/c66/dsp1/bin/sbl_app.xe66

export APP_DSP2=$(TI_PDK_INSTALL_DIR)/packages/ti/boot/sbl/binary/idkAM572x/example/c66/dsp2/bin/sbl_app.xe663

export APP_IPU1_CPU0=$(TI_PDK_INSTALL_DIR)/packages/ti/boot/sbl/binary/idkAM572x/example/m4/ipu1/bin/sbl_app.xem4

export APP_IPU1_CPU0=$(TI_PDK_INSTALL_DIR)/packages/ti/boot/sbl/binary/idkAM572x/example/m4/ipu2/bin/sbl_app.xem4

3. If it is not required to load an application on specific core leave the variable blank.

- Run the script file AM57xImageGen found under the path $(TI_PDK_INSTALL_DIR)/packages/ti/boot/sbl/tools/scripts

5. An application image by name app is created in the path pointed by BIN_PATH variable

6. Copy the Bootlaoder image(MLO) and application(app) in the SD card to boot using MMCSD boot mode.

Note

- The AM57xImageGen.sh script depends on tools like mono to execute the out2rprc.exe.

- The linux host environment needs to have this tool installed to execute this script.

- Refer this link to download the mono tool

4.6.3.2.6.3. Windows environment¶

Command to build the test application.

Go to cd (TI_PDK_INSTALL_DIR)\packages\ti\boot\sbl

gmake example BOARD=<BOARD> SOC=<SOC> to build the application

gmake example_clean BOARD=<BOARD>

Example:

gmake example BOARD=idkAM572x SOC=AM572x

To create the final bootable application image use the AM57xImageGen script and follow these steps

- Set the following environment variable in windows command prompt

BIN_PATH: Pointing to the path where the AppImage needs to be generated

Ex: set BIN_PATH=%TI_PDK_INSTALL_DIR%\packages\ti\boot\sbl\binary

2. Edit the batch file to point to the application elf files by setting the input application variables.

App_MPU_CPU0: Point to the path where the application .out for A15 MPU is located App_DSP1: Point to the path where the dsp core 1 application is located App_DSP2: Point to the path where the dsp core 2 application is located

set App_MPU_CPU0=%TI_PDK_INSTALL_DIR%\packages\ti\boot\sbl\binary\idkAM572x\example\armv7\bin\sbl_app.out

set App_DSP1=%TI_PDK_INSTALL_DIR%\packages\ti\boot\sbl\binary\idkAM572x\example\c66\dsp1\bin\sbl_app.xe66

set App_DSP2=%TI_PDK_INSTALL_DIR%\packages\ti\boot\sbl\binary\idkAM572x\example\c66\dsp2\bin\sbl_app.xe66

set App_IPU1_CPU0=%TI_PDK_INSTALL_DIR%\packages\ti\boot\sbl\binary\idkAM572x\example\m4\ipu1\bin\sbl_app.xem4

set App_IPU2_CPU0=%TI_PDK_INSTALL_DIR%\packages\ti\boot\sbl\binary\idkAM572x\example\m4\ipu2\bin\sbl_app.xem4

3. If it is not required to load an application on specific core leave the variable blank.

- Run the batch file AM57xImageGen found under the path $(TI_PDK_INSTALL_DIR)/packages/ti/boot/sbl/tools/scripts

5. Follow the steps 4 to 6 listed above for Linux environment. | Setup Requirements “”“”“”“”“”“”“”“”“”“” For information on board specific requirements like power supply, UART console port connections refer the Hardware User guide of the respective boards.

The configurations needed to setup UART console through a serial terminal application on host PC are listed in the next section.

4.6.3.2.6.3.1. UART Console Setup¶

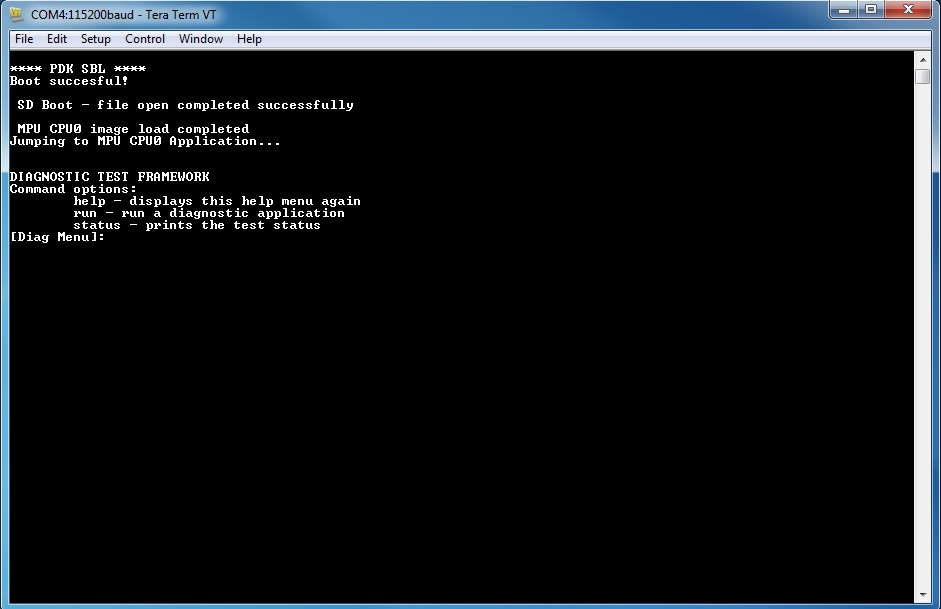

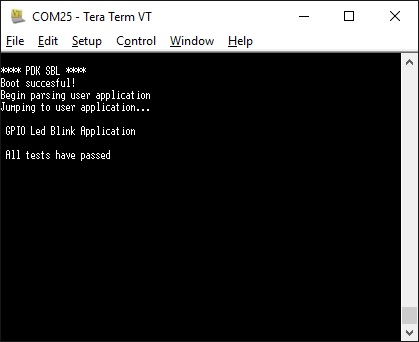

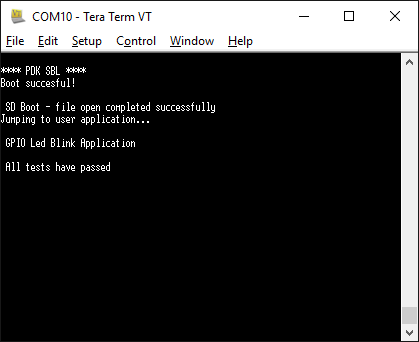

PDK SBL prints messages on the UART Serial Console running on the host. Hence, a serial terminal application (like Tera Term/HyperTerminal/minicom) should be running on the host.

The host serial port must be configured at 115200 baud, no parity, 1 stop bit and no flow control. Please ensure that the local echo setting for the terminal is turned off.

4.6.3.2.6.3.2. Loading the test application¶

Follow these steps to load the test application using a SD card on the target

copy the MLO to your SD card (located at %TI_PDK_INSTALL_DIR%packagestibootsblbinary[BOARD]mmcsd)

- copy the example app located at path pointed to by BIN_PATH to your SD card

- insert your SD card into your board and power on your board

- open teraterm to connect to the board’s UART console

- press the “Hard Reset” button on your board

On Successful bootup you should see the following logs on the UART console for a AM572x based board.

Note

MPU Core 0 example does a sequential check of mailbox messages sent from the other cores. On rare occasions, the check happens before the message is sent - the “<core> boot-up Successful” message might not be displayed even though the core(s) were booted successfully.

4.6.3.2.7. Application Integration¶

4.6.3.2.7.1. Memory Map¶

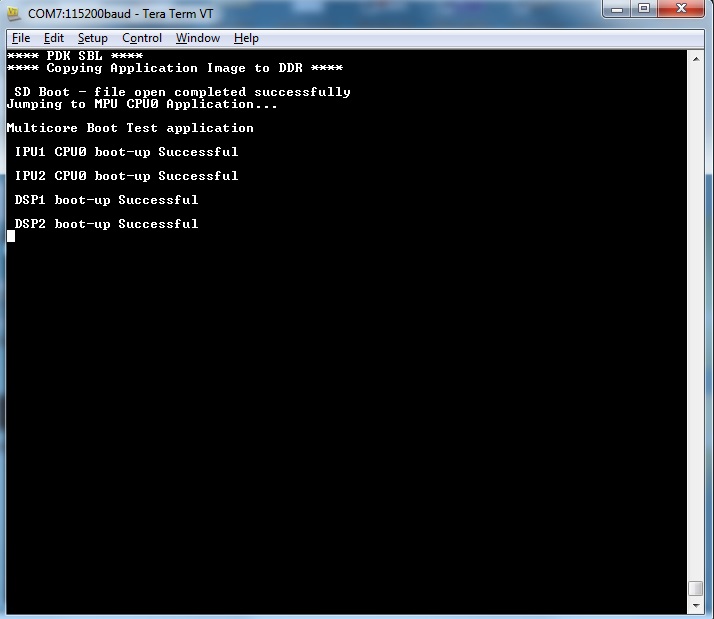

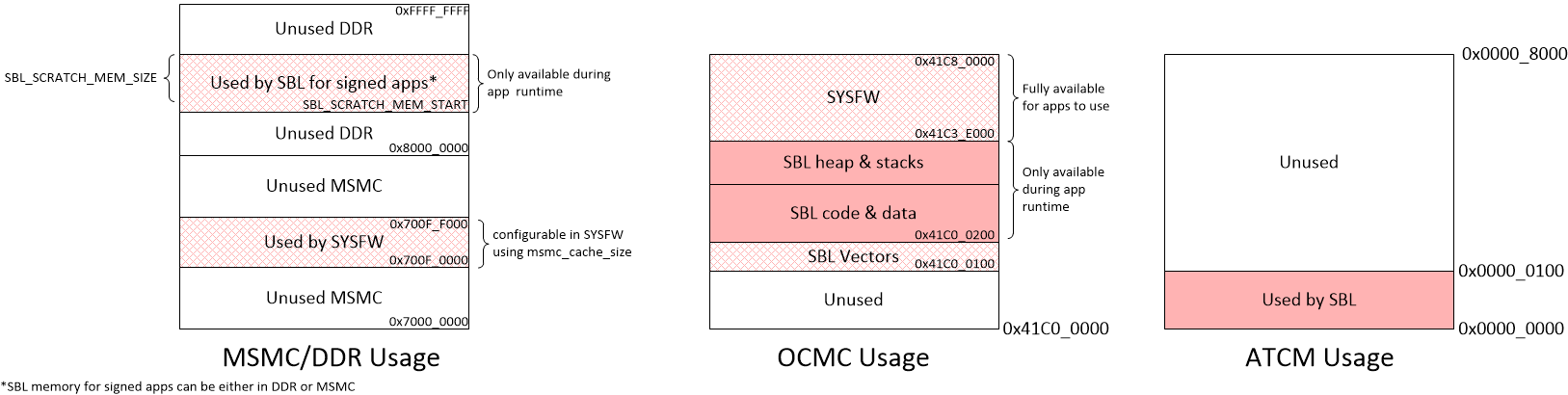

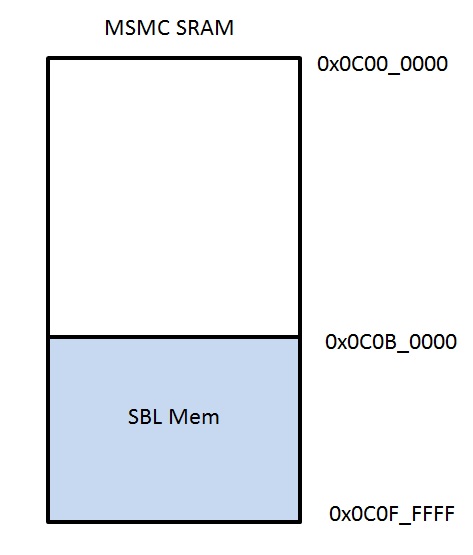

Table indicated below provides memory map details for SBL image in OCMC_RAM1. For more details on pinmux and IO delay requirements refer this link Processor SDK Board Support

We recommend that users should refer to the linker command file and the map file for the boot loader to check for latest information on the memory utilization in the boot loader.

Location of linker command file: <PDK_INSTALL_PATH>packagestibootsblboard<BOARD>build

The SBL memory map is shown below

Note

- After the application boots and is running on the SOC, it is free to use the SBL_MEM region.

- The pinmux data from the board library and MMU Table are part of the SBL_MEM region indicated in the figure above. If pinmux data needs to be placed at a specific location then users can update the SBL linker command file to add the BOARD_IO_DELAY_CODE and BOARD_IO_DELAY_DATA as described in Application Integration of board library for AM5x

4.6.3.2.8. SBL Customization¶

4.6.3.2.8.1. Changing boot media offsets¶

The location at which SBL resides on the flash is predefined by the ROM bootloader spec and so these defaults can`t be changed. However the SBL is a user defined bootloader so many of the defaults can easily be modified to meet application requirements. For example the flash offset location from which the bootloader reads the application is configured in the source files located under PDK_INSTALL_PATHpackagestibootsblsrc<BOOT_MEDIA>

Examples of customization that can be changed: - QSPI/SPI flash offsets: These offsets are configured in sbl_qspi.c

and sbl_spi.c

- MMCSD: The name of the application is hard coded as app in function SBL_MMCBootImage in the sbl_mmcsd.c

4.6.3.2.8.2. Speeding up boot by increasing speed of the boot interface¶

The SBL for AM57xx devices uses LLD drivers to read and write from boot media supported. The SBL uses the default SOC configuration of the drivers and the speeds setup. For example, the SPI driver default SPI bitrate is 1 MHz (Refer PDK_INSTALL_PATHpackagestidrvspisrcSPI_drv.c) so if you wish to speed up boot you can update the SPI parameter in the SBL as shown below:

SPI_Params_init(&spiParams);

spiParams.bitRate = 24000000U;

The configuration of the driver is usually done in the boot/sbl/soc/<device>/sbl_soc.c file.

- For SD/MMC: You can configure higher speed and change bus width using MMCSD_v1_HwAttrs_s or MMCSD_v0_HwAttrs_s

- For QSPI: 2 pin and 4 pin mode, and input frequency is configured using QSPI_HwAttrs in the QSPI driver. Check driver for defaults.

Also, check to see if the CACHE and MMU settings for the ARM core are setup to enable fast boot.

Note

SYSBOOT settings for AM57xx

The SYSBOOT configuration in your hardware using Sitara devices (AM3/AM4/AM5) can play a big role in the time required to boot successfully. On these devices the boot pins configure a boot sequence for the ROM bootloader to check for valid boot image so if you have a preferred boot mode designers are required to use SYSBOOT setup such that the preferred boot media is first in the boot sequence. If the preferred boot media occurs later boot sequence, the boot is likely to add the time required by RBL to check other boot media for an valid image. For example if QSPI is the preferred boot media on your AM57xx hardware then you should have system configure SYSBOOT to boot of QSPI first using SYSBOOT setting for QSPI_1 or QSPI4 for Memory preferred booting or Production booting (Refer: Initialization chapter in TRM).Incorrect SYSBOOT configuration can causes long delays especially if peripheral boot is configured to be one of the preferred boot modes in the boot order

4.6.3.2.8.3. Reducing size of SBL and application¶

Another way to optimize boot times is to reduce the size of the binary that needs to be loaded by the bootloader by building the app with optimization for code size using -Os (GNU GCC) and for -O<level> when using TI compilers.

Other than compiler based optimizations developers can actively shutdown non-essential modules and features to reduce code size. For example if UART logging is not required or DDR memory is not connected in the system, the initialization functions can be removed to reduce code size.

4.6.3.2.9. Usage Notes¶

4.6.3.2.9.1. SBL AVS and ABB setup¶

AVS and ABB configuration is mandated for normal operation of AM57xx devices. All Processor SDK RTOS releases v3.3 and later contain SBL that sets up AVS and ABB configuration features using PM LLD APIs The complete details of PMIC configuration and AVS and ABB configuration required by the chip for different OPP has been implemented in the file:

PDK_INSTALL_PATHpackagestibootsblboardsrcsbl_avs_config.c If you are using the same PMIC as GP EVM or IDK platform then you can reuse the settings as is in SBL for your custom platform

4.6.3.2.9.2. Configuring entry point for SBL¶

The two key files that help setup the entry point in the SBL build are “sbl/soc/<SOC_NAME>/sbl_init.S” and the linker command file “sbl/soc/<SOC_NAME>/linker.cmd”. The global symbol Entry is used to provide the entry point to the SBL. The Base address of the memory section SBL_MEM is then used by the tiimage and GP Header tool to provide RBL the guidance to find the entry point to pass control. After MLO is created check the TI image format file(MLO or _ti.bin) or the GP Header file to confirm that the entry point matches the location of Entry symbol in the sbl.map

Note

The object file created by sbl_init.S should always be the first object file in the link order for the symbol Entry to be placed at the BASE address of the memory section SBL_MEM

4.6.3.2.9.3. Debugging application boot¶

Steps to debug application boot using Processor SDK RTOS bootloader are discussed in the article Common steps to debug application boot

4.6.3.3. AM65x¶

4.6.3.3.1. Overview¶

The Secondary Bootloader (SBL) for AM65xx device initializes the execution environment for multi-core applications and this can be used to demonstrate a real world product experience. This section covers additional details including execution sequence, tools and additional flashing instructions.

The SBL is essentially a baremetal application, and it uses many components from the Processor SDK

- <PDK>/packages/ti/build : For build infrastructure

- <PDK>/packages/ti/csl : For initialization and SoC addresses

- <PDK>/packages/ti/board : For board and usecase specific initialization

- <PDK>/packages/ti/drv/spi : For reading applications from OSPI flashes

- <PDK>/packages/ti/drv/udma : For reading data from boot media using DMA

- <PDK>/packages/ti/drv/mmcsd : For reading applications from MMC/SD/eMMC

- <PDK>/packages/ti/fs/fatfs : For reading files from MMC/SD/eMMC

- <PDK>/packages/ti/drv/sciclient : For communicating with DMSC sub-system

- <PDK>/packages/ti/drv/uart : For log messages

- <PDK>/packages/ti/osal : Primitives required by ti/drv components

The SBL is in turn used by the board framework to load and start diagnostics

Bootloader Execution Sequence

- Power On Reset

- ROM Bootloader (RBL)

- Software pre-programmed in AM65xx ROM memory starts executing

- The RBL performs platform configuration and initialization.

- It then checks sysboot pins and chooses booting device

- The RBL then configures PLL and clock settings for R5, and boot media like eMMC, SD/MMC, OSPI, UART, PCIe, Ethernet etc for reliable boot.

- If no valid bootloader found on booting device, the RBL checks for next booting device, based on sysboot pins

- It then gets image size and load address by checking the X.509 certificate that is part of the bootloader image.

- The RBL then verifies, optionally decrypts and loads the binary to internal memory at the load address specified in the X.509 certificate.

- Finally it resets the R5 and passes control to Secondary Bootloader(SBL) running on the R5.

- Secondary bootloader(SBL)

- User level secondary bootloader(SBL) begins execution from internal memory. It enables ATCM, starts PMU timers for profiling, initializes the MCU, and sets up the stack, heap and globals. It then jumps to main().

- Board Initialization is done by calls to Board_init() API.For additional details refer Processor SDK Board Support.

- The RAT is setup. Pin MUX and UART console are setup by calling Board_init() API. The system firmware (SYSFW) is then loaded from the boot media into the DMSC subsystem.

- Once the SYSFW is up and running, the rest of the initialization can be done.

- This includes optionally using Board_init() to configure PLLs, LPSCs and DDR.

- The SBL then loads the application from the boot media. If the image is signed, the application will be copied into a user specified reserved memory, and the SBL will attempt to verify the image by calling system firmware APIs. On HS devices, the boot proceeds only if image verification passes.

- The SBL parses application image(s) for each of the core(s) from boot media and scatter loads it to memory.

- Once the application is loaded, the SBL communicates with the system firmware to setup the clocks for the core(s) and release it from reset.

- The core then starts executing from application entry point.

NOTE

- RBL requires boot loader (SBL) to be in a special format with the binary image appended to a X.509 certificate. The certificate contains the load address, size and SHA of the bootloader image.

- For a detailed description of ROM bootloader and more information on the image format expected by the RBL refer the initialization chapter in the AM65xx Technical Reference Manual

- In addition to the bootloader and application, the DMSC firmware binary is also needed for the SoC to complete the system boot flow.

- The first 256 bytes of the ATCM are reserved by SBL for its use. The SBL initializes the ATCM with 0xFF before it uses it.

- If the multicore application image is also signed with a X.509 certificate, the same binary can be used on GP and HS devices. For information on the application’s X.509 certificate format, please refer Security X509 Certificate Documentation

- When the R5 is released from reset, it will always fetch and execute the first intruction from address 0x0.

4.6.3.3.2. Block Diagram¶

4.6.3.3.3. Memory Map¶

4.6.3.3.4. Directory structure¶

sbl

│

├── board

│ └── k3

│ └── sbl_main.c <= define main() for SBL, board specific init

│

├── build

│ ├── makefile <= makefile for the SBL component

│ ├── sbl_am65xx.sh <= For legacy, called by Yocto build

│ ├── sbl_boot_test.mk <= Builds SBL single core tests

│ ├── sbl_smp_test.mk <= Builds example app for using SBL lib

│ ├── sbl_mcu0_boot_perf_test.mk <= Builds example app for SBL performance tuning

│ ├── sbl_mcu0_boot_xip_entry.mk <= Builds example trampoline app to demonstrate transitioning to a XIP app from SBL

│ ├── sbl_mcu0_boot_xip_test.mk <= Builds example app to demonstrate XIP execution from XIP capable boot media

│ ├── sbl_img.mk <= builds SBL image that is loaded and executed by ROM code

│ ├── sbl_lib.mk <= Builds sbl library that other apps can link into

│ ├── sbl_multicore_smp.mk <= Builds multi-core image from SBL lib eg. test to demonstrate symmetric multiprocessor boot (SMP)

│ └── sbl_multicore_amp.mk <= Builds multi-core image from single core tests to demonstrate asymmetric multiprocessor boot (AMP)

│

├── example

│ └── k3MulticoreApp

│ ├── binary

│ │ └── am65xx

│ │ ├── sbl_baremetal_*.appimage <= SBL loadable board specific sample apps for testing SBL boot flow on GP devices

│ │ ├── sbl_baremetal_*.appimage.signed <= SBL loadable board specific signed sample apps for testing SBL boot flow on HS devices

│ │ └── sbl_baremetal_*_release.x*.bin <= Binary image that can be eXecuted In Place on XIP capable boot media

│ ├── mcuAmplinker.lds <= Linker comamnd file when TI CGT is used for Asym. Multiproc. boot

│ ├── mpuAmplinker.lds <= GCC linker command file (for Cortex Axx cores) for Asym. Multiproc. boot

│ ├── mcuBootPerfLinker.lds <= TI CGT Linker comamnd file for SBL performance tuning example.

│ ├── mcuLockStepLinker.lds <= Linker comamnd file when TI CGT is used for R5 lock-step boot

│ ├── mpuSmplinker.lds <= GCC linker command file (for Cortex Axx cores) for SMP boot

│ ├── mcuXiplinker.lds <= Linker command file for XIP trampoline app

│ ├── xip_entry.lds <= Linker comamnd file for XIP test case

│ ├── xip_entry.asm <= Entry point of XIP trampoline app

│ ├── xip_stub.c <= Simple SBL test app that demonstrates transitioning to a XIP app

│ ├── sbl_amp_multicore.c <= Simple SBL test that displays UART message

│ ├── sbl_amp_multicore_sections.h <= Allows same source to be loaded to different sections for different cores.

│ ├── sbl_mcu_0_boot_perf_benchmark.c <= SBL Test to tune boot performance.

│ ├── sbl_multicore_a53.asm <= Test case entry point for Cortex-Axx cores

│ ├── sbl_multicore_r5.asm <= Test case entry point for Cortex-R5 cores

│ ├── sbl_multicore_r5_sections.inc <= Allows same source to be loaded to different sections for different MCUs.

│ ├── sbl_printf.c <= Lightweight UART printf function for SBL testing

│ ├── sbl_smp_multicore.c <= Simple SBL SMP test that uses SBL lib to reset MPUs

│ └── sbl_smp_r5.asm <= Provides dummy override function for __mpu_init for SMP testcase.

│

├── binary <= ROM bootable SBL images for each board/boot media

│ ├── am65xx_evm

│ │ ├── mmcsd

│ │ │ └── bin

│ │ │ └── sbl_mmcsd_img_mcu1_0_release.tiimage

│ │ └── ospi

│ │ └── bin

│ │ └── sbl_ospi_img_mcu1_0_release.tiimage

│ └── am65xx_idk

│ ├── mmcsd

│ │ └── bin

│ │ └── sbl_mmcsd_img_mcu1_0_release.tiimage

│ └── ospi

│ └── bin

│ └── sbl_ospi_img_mcu1_0_release.tiimage

│

├── lib <= SBL lib for each boot media/board supported

│ ├── mmcsd

│ │ ├── am65xx_evm

│ │ │ └── r5f

│ │ │ └── release

│ │ │ └── sbl_lib_mmcsd.aer5f

│ │ └── am65xx_idk

│ │ └── r5f

│ │ └── release

│ │ └── sbl_lib_mmcsd.aer5f

│ │

│ ├── ospi

│ │ ├── am65xx_evm

│ │ │ └── r5f

│ │ │ └── release

│ │ │ └── sbl_lib_ospi.aer5f

│ │ └── am65xx_idk

│ │ └── r5f

│ │ └── release

│ │ └── sbl_lib_ospi.aer5f

│ │

│ └── cust

│ ├── am65xx_evm

│ │ └── r5f

│ │ └── release

│ │ └── sbl_lib_cust.aer5f

│ └── am65xx_idk

│ └── r5f

│ └── release

│ └── sbl_lib_cust.aer5f

│

├── soc <= SOC specific SBL code

│ └── k3

│ ├── linker.cmd <= Linker file used for generating ROM loadable SBL image.

│ ├── sbl_err_trap.h <= Error loops for SBL

│ ├── sbl_init.asm <= SBL Entry point

│ ├── sbl_misc.asm <= SBL Assembly utility functions

│ ├── sbl_log.h <= SBL logging framework

│ ├── sbl_sci_client.c <= Calls SYSFW on DMSC

│ ├── sbl_sci_client.h

│ ├── sbl_slave_core_boot.c <= Code that contains the sequence to release a core from reset

│ ├── sbl_slave_core_boot.h

│ ├── sbl_soc.c <= Cache Ops, PMU init, image verfication, etc & SoC specific code like RAT Init..

│ ├── sbl_soc_cfg.h <= Abstraction layer for hiding K3 SoC level changes from SBL

│ └── sbl_profile.h <= SBL profiling framework

│

├── src <= Common drivers used across SOCs

│ ├── mmcsd

│ ├── ospi

│ ├── qspi

│ ├── rprc <= RPRC image parser used by SBL

│ └── spi

│

└── tools

├── btoccs

├── byteswap

├── ccsutil

├── flashWriter <= Unused for AM65xx. AM65xx uses Uniflash to program flashes.

├── multicoreImageGen <= Stitches multiple RPRC images for different cores into a single image

├── omapl13x_boot_utils <= Unused for AM65xx

├── omapl13x_sd_card_format <= Unused for AM65xx

├── out2rprc <= Converts .out into .rprc files, so that SBL can load non-continuous memory sections

├── scripts <= Scripts used by .out generated by CCS projects into SBL loadable images

│ ├── K3ImageGen.bat

│ └── K3ImageGen.sh

└── tiImageGen <= Unused for AM65xx. Image generation is handled by PDK build framework (<prsdk_install_path>/pdk_*/packages/ti/build/)

4.6.3.3.5. Image Formats¶

SBL format:

To generate the a bootable image, the SBL build uses the x509CertificateGen script to sign the sbl binary with so that the ROM Boot Loader (RBL) can parse it. The image format expected by the RBL has been described in detail in the Image Format Section of the AM65xx Technical Reference Manual

Note

For HS devices, the SBL and system firmware have to be signed with the MPK. For an easy out-of-box experience, the Processor SDK for HS devices signs the SBL and system firmware with a TI Dummy Key. Images signed with a TI dummy key will boot on both GP and HS boards from TI.

Warning

The TI Dummy Key(s) MUST be replaced by customers during production with their own Private Keys. If the TI Dummy Keys are used in a production system, the system will be open to security attacks.

Warning

While SBL and system firmware images signed with the TI Dummy Keys will work on both GP and HS devices, the boot time will be significantly impacted on GP devices. Using SBL signed by TI Dummy Keys on GP devices is only recommended during the prototyping phase - when porting code developed on GP to HS devices.

Application image format:

Two utilities - out2rprc and multicoreImageGen are used to convert an application elf image(s) into an image loadable by the SBL. The structure of a multicore application image is provided below:

RPRC File Header Format

| Offset | Binary value |

|---|---|

| 0x00000000 | Magic Word(43525052) |

| 0x00000004 | Entry Point (Location) |

| 0x00000008 | Reserved Addr |

| 0x0000000C | Section Count |

| 0x00000010 | Version |

RPRC Section Header Format

| Offset | Binary value |

|---|---|

| 0x00000000 | Section start Address |

| 0x00000004 | Reserved Addr |

| 0x00000008 | Size |

| 0x0000000C | Reserved CRC |

| 0x00000010 | Reserved |

Multicore boot image format

Meta Header Start

| Offset | Binary value |

|---|---|

| 0x00000000 | Magic String (0x5254534D) |

| 0x00000004 | Number of Files |

| 0x00000008 | Device ID |

| 0x0000000C | Reserved |

Meta Header per Core

| Offset | Binary value |

|---|---|

| 0x00000000 | Core ID |

| 0x00000004 | Image Offset |

Signed application image format:

To convert the multicore application image into a format that can be verified, the build flow uses the x509CertificateGen script to create a x509 certificate for the app image. Images that have a x509 certificate are called signed images. Signed applications images are mandatory for HS devices, but will work also work on GP devices.

Signed images are automatically detected by the SBL and loaded into a scratch memory area specified during SBL build. The scratch memory area used by default is specified in sbl_lib.mk via the flags SBL_SCRATCH_MEM_START and SBL_SCRATCH_MEM_SIZE. The SBL_SCRATCH_MEM* options can also be specified for custom builds to override the defaults.

The SBL scratch memory is unavailable to applications during app load time, as the SBL is still active. Once the SBL transfers control to the application, this memory is available for app use - in other words SBL_SCRATCH_MEM* is available during app runtime.

For information on the application’s X.509 certificate format, please refer Security X509 Certificate Documentation

4.6.3.3.6. Building the SBL and its components¶

Pre-requisites to Building

- Set your environment using pdksetupenv.bat or pdksetupenv.sh. Refer to Processor SDK RTOS Building for information on setting up your build environment

NOTE

- SBL needs openssl to build. To check if openssl is present, type the following at the linux or windows prompt.

openssl version

- To build on Linux, you need to have mono installed.

- Refer Build Dependencies for instructions on how to install these tools, if they are not already present on your system.

Compiling the SBL

To build all the SBL components:

cd <PDK>/packages/ti/boot/sbl/build

gmake clean all (for windows)

make clean all (for Linux)

- SBL image files are be located at: <PDK>/packages/ti/boot/sbl/binary/

- SBL examples are located at <PDK>/packages/ti/boot/sbl/examples/k3MulticoreApp/binary

- SBL lib are located at <PDK>/packages/ti/boot/sbl/lib/

Compile time options for the SBL

The SBL supports several compile time options to tweak the SBL to satisfy requirements of ease of use, boot time and size. These can be enabled or disabled by editing sbl/sbl_component.mk

- SBL_LOG_LEVEL : Controls amount of SBL logs (on the MCU UART) and system firmware logs(on WAKEUP UART). Varies from 0(no logs) to 3 (all logs)

- SBL_USE_DMA : Valid values are 0 (use CPU to access boot media) or 1 (use DMA to access boot media).

- SBL_DISPLAY_PROFILE_INFO : At the end of the boot process, displays a log of timestamps at which different SBL profile points are hit. This is useful to see how much time the SBL spends in different functions. SBL_LOG_LEVEL can significantly affect performance numbers.

- SBL_ENABLE_PLL : Dials up all the PLLs calling Board_init(). Makes it easier for applications as they no longer have to initialize the PLLs. However, enabling this significantly increases boot time and power consumption. Requires system firmware to be loaded.

- SBL_ENABLE_CLOCKS : Enables all the module clocks by calling Board_init(). Makes it easier for applications as they no longer have to enable clocks.

- SBL_ENABLE_DDR : Initializes the DDR. At the cost of boot time, this enables applications to run from and use DDR. SBL_ENABLE_CLOCKS and SBL_ENABLE_PLL must also be enabed for this to work. Enabling this option increases the boot time.

- SBL_SKIP_MCU_RESET : Jumps to the MCU0 application entry point without resetting the core. Enables faster boot time. Will not change the MCU’s mode (lock-step/split). Application also inherits the MCU state as the SBL left it in.

The SBL also supports a “custom” build, in addition to standard out-of-box builds. A custom build is a useful way of testing out the effect of different build options - like when optimizing for boot time, or enabling custom usecases like eXecute In Place (XIP) to reduce memory usage.

For an example of how to use such custom builds, please refer to sbl/sbl_component.mk. It shows how to specify a select list of build options while building SBL images and libs.

Compiling apps that can be loaded by SBL:

Memory Map Considerations

Applications that the SBL loads must comply with the am655x-sbl-memory-usage. In the application’s linker command file, care must be taken to not use the first 0x100 bytes of any R5 MCU’s ATCM memory and SBL reserved memory from 0x41C00100 to 0x41C3E000. If the applications are signed, no loadable sections must be placed in the SBL scratch memory area. The scratch memory can be used at application runtime for stacks, heaps, etc.

NOTE

- The local address 0x0 of the MPU is not accessible from the MCU, so any MPU linker command file must not specify any loadable sections in that memory region. The SBL will not be able to access that memory to load code or data.

Converting ELF executables to SBL loadable image

Depending on the usecase, an ELF application executable can be converted into an image that can be loaded by SBL in many ways.

- Using CCS: Any project created using the pdkProjectCreate scripts will automatically generate a SBL loadable app, as part of a post-build step.

- Using makefiles: Add the following lines to the component’s .mk file

app_name_SBL_APPIMAGEGEN = yes

export app_name_SBL_APPIMAGEGEN

- Existing ELF executable: By calling the K3ImageGen script.

Linux Syntax: K3ImageGen.sh <CoreID> <.out>

Example:

cd <prsdk_install_path>/pdk_*/packages/ti/boot/sbl/example/ampMulticoreApp/binary/am65xx_evm/

K3ImageGen.sh 4 sbl_baremetal_boot_test_am65xx_evm_mcu1_0TestApp_release.xer5f

Windows Syntax: K3ImageGen.bat "<CoreID> <.out>"

Example:

cd <prsdk_install_path>\pdk_*\packages\ti\boot\sbl\example\ampMulticoreApp\binary\am65xx_evm\

K3ImageGen.bat "4 sbl_baremetal_boot_test_am65xx_evm_mcu1_0TestApp_release.xer5f"

- Multicore Images: Multicore images, as the name suggests, allows the SBL to load applications for multiple cores from a single image. Creating such images invloves three steps.

- Generate the ELF application executables for individual cores

- Convert the ELF executables into intermediate .rprc images

- Combine the .rprc images of individual cores to create a single multicore image

To covert any .out into the intermediate .rprc format, execute the following commands

For Linux:

mono <PDK>/packages/ti/boot/sbl/tools/out2rprc/bin/out2rprc.exe input.out output.rprc

For Windows:

<PDK>\packages\ti\boot\sbl\tools\out2rprc\bin\out2rprc.exe input.out output.rprc

To stitch multiple .rprc images into a multicore image, execute the following command

For Linux:

<PDK>/packages/ti/boot/sbl/tools/multicoreImageGen/bin/MulticoreImageGen LE 55 output.appimage <core_id_1> core_1.rprc <core_id_2> core_2.rprc

For Windows:

<PDK>/packages/ti/boot/sbl/tools/multicoreImageGen/bin/MulticoreImageGen.exe LE 55 output.appimage <core_id_1> core_1.rprc <core_id_2> core_2.rprc

NOTE

- The linux host environment needs to have mono installed.

- The values used for the Core ID and Device ID can be found in sbl/soc/k3/ sbl_slave_core_boot.h

- To simply load an ELF without executing it, use CoreID value ONLY_LOAD_ID

- If an image for MCU_1 core is provided, the SBL will attempt to switch to split mode.

- If only an image for MCU_0 is provided, the SBL will not change the mode of the MCU subsystem.

- To enable SMP on the MPU, ie, to get multiple MPUs execute from a single binary

from the same address, use one of the following core_ids

- MPU1_SMP_ID: The same app binary runs on both cores in MPU cluster 1

- MPU2_SMP_ID: The same app binary runs on both cores in MPU cluster 2

- MPU_SMP_ID: The same app binary runs all the MPUs

Converting ELF executables to executable binary images

Sometimes, for exteremely constrained and specialized usecases like ultra-low-latency boot or DDR-less systems, an ELF application executable can be converted into a binary image that can executed directly from the boot media, without loading into internal memory.

As internal memory is always accessible, this mode of execution allows some otherwise mandatory steps steps like DDR initlization or clock initialization to be done later or skipped altogether.

Working with such highly contrained systems require some special steps..

- Make sure that the boot media supports eXecuting In Place (XIP).

- Use the custom SBL build to select the build options to build a SBL that meets the usecase requirements.

- In the linker command file for the application, make sure that all the data sections, stacks, heaps and globals are in internal read/write memory

- In the linker command file for the application, make sure that there are no holes in the loadable sections. Such non-contiguous sections can drastically blow up the binary image size, when comapred to the ELF executable size.

- To generate an executable binary image from the applications ELF file, add the following lines to the component’s .mk file

app_name_SBL_APP_BINIMAGEGEN = yes

export app_name_SBL_APP_BINIMAGEGEN

4.6.3.3.7. Testing the SBL¶

SBL provides test applications to demonstrate booting the A53 and R5 cores in both symmetric/lock step & asymmetric/split-mode and other features. The multicore sample application prints a message on the UART for each core. The functionality the different tests exercises are listed below.

- sbl_*_boot_test_*_all_coresTestApp_release: A single multicore boot test case that boots each core in the SoC with a separate app. Also tests DDR loading

- sbl_*_boot_test_*_xxxx_xTestApp_release.appimage: A simple testcase for booting core xxxx_x (eg. MCU1_0, MPU2_0 etc.)

- sbl_*_smp_test_*_all_coresTestApp_release.appimage: A single SMP boot test case that boots MCUs in lock step. The MCU app then uses the SBL lib to boot all the MPUs in SMP mode, ie, all the MPUs execute a single binary from the same address.

- sbl_baremetal_boot_perf_*_mcu1_0TestApp_release.appimage: A single MCU1_0 test case that can be used to measure the effect of enabling/disabling the perf. tuning knobs in the SBL for OSPI boot. The size of the test case can be easily modified by changing the value of SIZE_OF_PAD in sbl/example/k3MulticoreApp/ sbl_mcu_0_boot_perf_benchmark.c to profile for different app image sizes.

- sbl_baremetal_boot_xip_test_am65xx_evm_mcu1_0TestApp_release.xer5f.bin: A testcase demonstrating booting an XIP application from OSPI flash. Please refer sbl/build/ sbl_mcu0_boot_xip_test.mk and sbl/example/k3MulticoreApp/mcuXiplinker.lds to see how to convert an existing application into an XIP application. The sbl_*_xip_entry_*.appimage works in tandem with sbl_*xip_test_*.xer5f.bin to transition the system from non-xip to xip boot, as the ROM, by default, does not support XIP from boot media. After programming the sbl and syfw, to program both sbl_*_xip_entry_*.appimage and sbl_*xip_test_*.xer5f.bin into OSPI flash, use the following uniflash commands

For Windows:

.\dslite.bat --mode processors -c COM9 -f <PDK>\packages\ti\boot\sbl\example\k3MulticoreApp\binary\am65xx\sbl_baremetal_boot_xip_entry_am65xx_evm_mcu1_0TestApp_release.appimage -d 3 -o A0000

.\dslite.bat --mode processors -c COM9 -f <PDK>\packages\ti\boot\sbl\example\k3MulticoreApp\binary\am65xx\sbl_baremetal_boot_xip_test_am65xx_evm_mcu1_0TestApp_release.xer5f.bin -d 3 -o E0000

For Linux:

sudo ./dslite.sh --mode processors -c /dev/ttyUSB1 -f <PDK>/packages/ti/boot/sbl/example/k3MulticoreApp/binary/am65xx/sbl_baremetal_boot_xip_entry_am65xx_evm_mcu1_0TestApp_release.appimage -d 3 -o A0000

sudo ./dslite.sh --mode processors -c /dev/ttyUSB1 -f <PDK>/packages/ti/boot/sbl/example/k3MulticoreApp/binary/am65xx/sbl_baremetal_boot_xip_test_am65xx_evm_mcu1_0TestApp_release.xer5f.bin -d 3 -o E0000

The test log for sbl_*_boot_test_*_all_coresTestApp_release is

SYSFW ver xx.x.x-v20xx.xx (xxx xxx) running

SBL Revision: xx.xx.xx.xx (MMM DD YYYY - HH:MM:SS)

MPU1_0 running

MPU1_1 running

MPU2_0 running

MPU2_1 running

MCU1_1 running

MCU1_0 running

MCU1_0 reports: All tests have passed

The test log for sbl_*_smp_test_*_all_coresTestApp_release.appimage is

SYSFW ver xx.x.x-v20xx.xx (xxx xxx) running

SBL Revision: xx.xx.xx.xx (MMM DD YYYY - HH:MM:SS)

MPU SMP boot test

Cores 0 & 1 will boot from 0x801007a0

Cores 2 & 3 will boot from 0x803007a0

Resetting all ARM cores now...

No of Cortex-A core(s) running: 1

No of Cortex-A core(s) running: 2

No of Cortex-A core(s) running: 3

No of Cortex-A core(s) running: 4

All tests have passed

The test log for sbl_baremetal_boot_perf_*_mcu1_0TestApp_release.appimage, when the best boot time is reached is

Time elapsed since start of SBL: 36665us

fxn:boot_perf_test_main cycles: 14666041