10. How to Guides¶

10.1. Target¶

10.1.1. Run IPC Examples on AM572x¶

10.1.1.1. DRA7xx/AM572xx IPC Examples¶

IPC Hello Example:

ex01_hello

The following examples demonstrate some of the rudimentary IPC capabilities. They are mostly two processors examples. These examples may be built for any two processors on your device, but only for two at a time. An IPC Ping example using three processors is also presented at the end.

Hello example uses the reader/writer design pattern. One processor will be the reader and the other will be the writer. The reader creates a message queue and waits on it for messages. The writer opens the reader’s message queue and sends messages to it. The writer allocates the message from a shared message pool and the reader returns the message to the pool. Thus, messages are sent in only one direction. Default settings of the Hello world example configures DSP1 as the writer and DSP2 as the reader.

Note

if Windows 7 machine is used for building these examples, GnuWin32 make utility needs to be installed to run make which can be downloaded from this link https://gnuwin32.sourceforge.net/packages/make.htm

Set GnuWin32\bin folder on file path and add a system variable XDCTOOLS_JAVA_HOME to point to “c:\ti\ccsv6\eclipse\jre“

set PATH=<YOUR_PROCEEDING_PATH>\GnuWin32\bin;%PATH%

set XDCTOOLS_JAVA_HOME=c:\ti\ccsv6\eclipse\jre

1. Change to the example folder by entering: cd ~/ti/ipc_nn_nn_nn_nn/examples/DRA7xx_bios_elf/ex01_hello

2. Open readme.txt file and follow build instructions step-by-step. If build this example on Ubuntu PC, make sure there is no spaces between variable name and its value.

DEPOT (your depository folder ex: DEPOT=/Your_Ubuntu_home_folder/ti)

BIOS_INSTALL_DIR=$(DEPOT)/bios_n_nn_nn_nn

IPC_INSTALL_DIR=$(DEPOT)/ipc_n_nn_nn_nn

XDC_INSTALL_DIR=$(DEPOT)/xdctools_n_nn_nn_nn

gnu.targets.arm.A15F=$(DEPOT)/ccsv6/tools/compiler/gcc-arm-none-eabi-4_8-2014q3

ti.targets.elf.C66=$(DEPOT)/ccsv6/tools/compiler/c6000_7.4.14

ti.targets.arm.elf.M4=$(DEPOT)/ccsv6/tools/compiler/arm_5.2.4

ti.targets.arp32.elf.ARP32_far=$(DEPOT)/ccsv6/tools/compiler/arm_5.2.4

See the following example, and ensure you are using the latest version

of folder names present in ~/ti folder:

DEPOT=/home/Your_Ubuntu_home_folder/ti

# Use the following environment assignment (Note you must use 32 bit Java even in Ubuntu 14.04 64 bit OS environment)

export XDCTOOLS_JAVA_HOME=/home/Your_Ubuntu_home_folder/ti/ccsv6/eclipse/jre

#### BIOS-side dependencies ####

BIOS_INSTALL_DIR=$(DEPOT)/bios_6_41_04_54

IPC_INSTALL_DIR=$(DEPOT)/ipc_3_36_01_11

XDC_INSTALL_DIR=$(DEPOT)/xdctools_3_31_02_38

#### BIOS-side toolchains ####

gnu.targets.arm.A15F=$(DEPOT)/ccsv6/tools/compiler/gcc-arm-none-eabi-4_8-2014q3

ti.targets.elf.C66=$(DEPOT)/ti-cgt-c6000_8.0.3

ti.targets.arm.elf.M4=$(DEPOT)/ccsv6/tools/compiler/ti-cgt-arm_5.2.4

ti.targets.arp32.elf.ARP32_far=$(DEPOT)/ccsv6/tools/compiler/ti-cgt-arm_5.2.4

- Run make command in current folder to build DSP1 and DSP2 hello examples. Output files are created under debug sub folders.

- ex01_hello\dsp1\bin\debug

- ex01_hello\dsp2\bin\debug

- Launch target configurations.

- Right click CortexA15_0 and connect target.

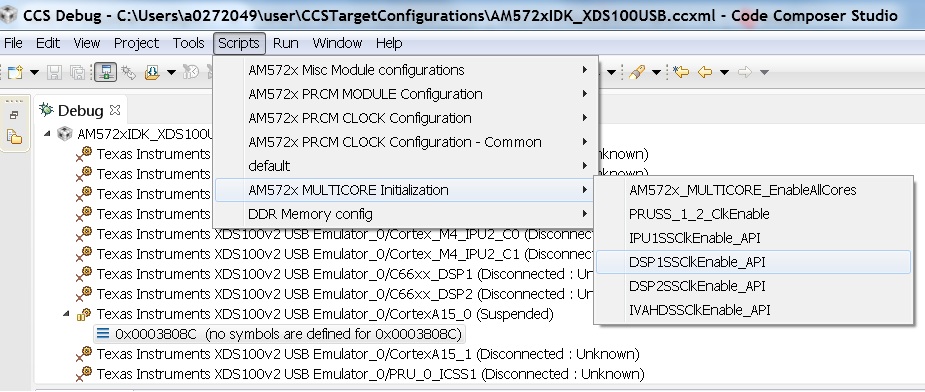

- On CCS –> Scripts –> AM572 Multicore Initialization –> Run AM572x Multicore EnableAllCore

- Initialize DDR configuration. On CCS –> Scripts –> DDR configurations –> AM572_DDR3_532MHz_config

- Load DSP1 Hello Example hello_dsp1.xe66 (writer)file on DSP1.

- Load DSP2 Hello Example hello_dsp2.xe66 (reader) file on DSP2.

- Run both DSP1 and DSP2.

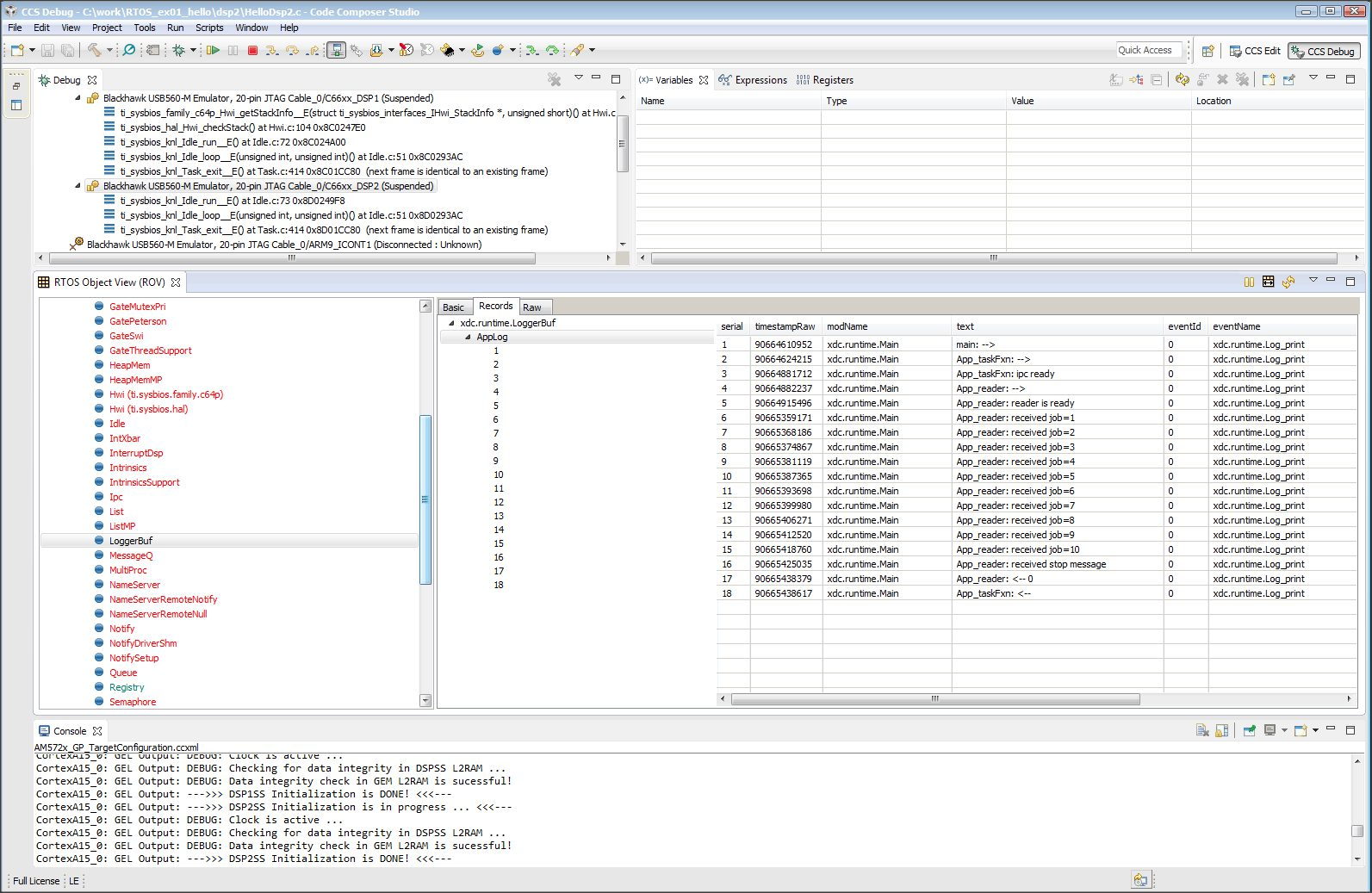

- On CCS –> Tools –> RTOS Object view (ROV).

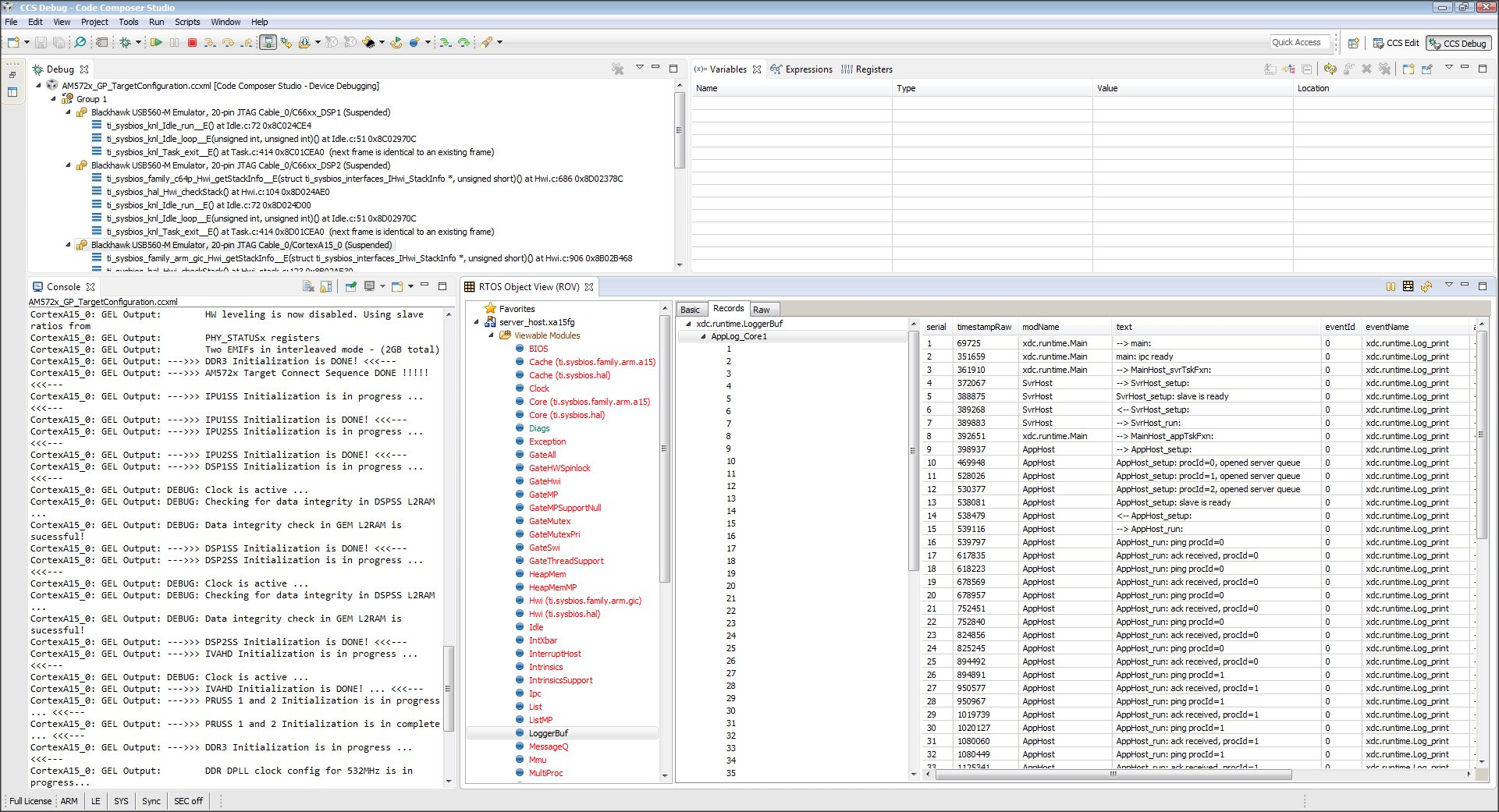

- Suspend (halt) DSP1 to view test messages on ROV Viewable Modules –>LoggerBuf Refer below image of ROV log messages.

- Suspend (halt) DSP2 and click on ROV icon to view log messages.

IPC Message Queue Example:

ex02_messageq

Message queue example sends round-trip message from client to server and back. MessageQ example uses client/server pattern. It is a two processors example: the HOST and DSP processors. Either DSP1 or DSP2 can be built for testing.

The DSP processor is configured as server. It creates a named message queue. The server does not open any queues because it extracts the return address from the message header. The server returns all messages to the sender. It does not access the message pool.

The HOST processor is configured as client application. The client creates an anonymous message queue. The client also creates and manages the message pool. The client’s return address is set in the message header for each message before sending it to the server.

- Change to messageQ folder example by enter:

cd ~/ti/ipc_nn_nn_nn_nn/examples/DRA7xx_bios_elf/ex02_messageQ

2. Open readme.txt file and follow build instructions step-by-step. Make sure there is no spaces between variable name and its value. See Hello World example environment varaible settings for reference.

- Run make command in current folder to build DSP1 and HOST hello examples. Output files are created under debug sub folders

- ex02_messageq\host\bin\debug : HOST A15 binary

- ex02_messageq\dsp1\bin\debug : C66x binary

- Launch target configurations. Note that BH560USB_M is emulator is used to connect to AM572X EVM.

- Right click CortexA15_0 and connect target.

- On CCS –> Scripts –> AM572 Multicore Initialization –> Run AM572x Multicore EnableAllCore

- Initialize DDR configuration. On CCS –> Scripts –> DDR configurations –> AM572_DDR3_532MHz_config

- Load DSP1 messageQ Example out file(server_dsp1.xe66) onto DSP1.

- Load HOST messageQ Example out file(app_host.xa15fg) onto ARM CortexA15_0.

- Run both DSP1 and HOST.

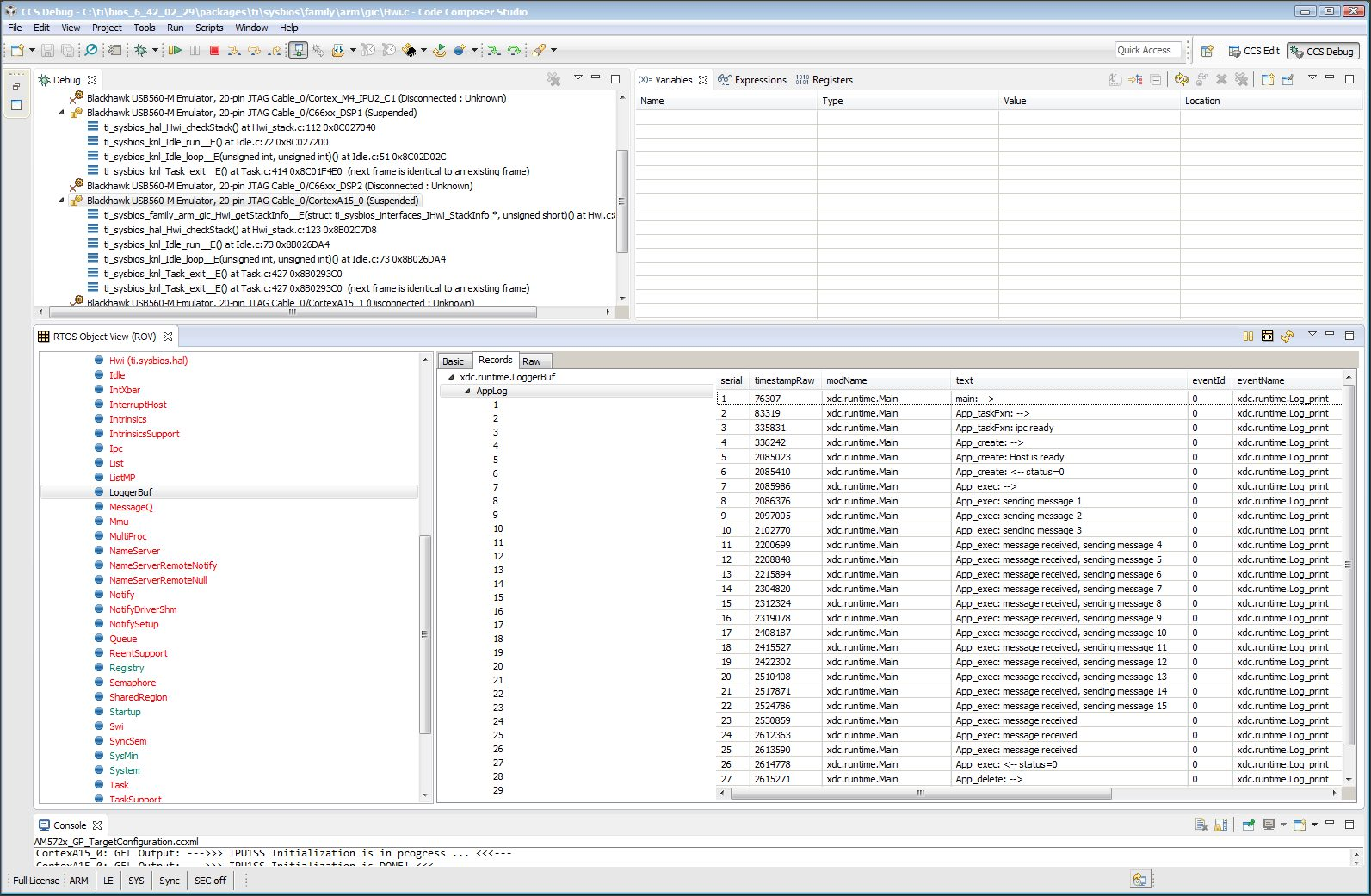

- On CCS –> Tools –> RTOS Object view (ROV).

- Suspend (halt) ARM Cortex_A15 to view test messages on ROV Viewable Modules –>LoggerBuf Refer the following ROV message queue screenshot

- Suspend (halt) DSP1 and click on ROV icon to view log messages.

IPC Notify Peer Example:

ex13_notifypeer

Notify peer example only uses notify to communicate to a peer processor. This is an example of IPC Scalability. It uses the client/server design pattern. Initially, the example builds only for two processors: HOST and DSP1. The client runs on HOST and the server runs on DSP1.

The client (HOST) creates an anonymous message queue. The client also creates and manages its own message pool. And it opens the server message queue using its name. The client initiates the data flow by allocating a message from the pool, placing its return address in the message header and sending the message to the server. It then waits for the message to be returned. When it receives the return message, the message is returned to the pool. The client repeats this in a loop.

The server (DSP1) creates a named message queue, then waits on it for messages. When a message arrives, the server performs the requested work. When the work is done, the server extracts the return address from the message header and sends the message back to the client. The server never opens any message queues and does not access the message pool.

Since DSP1 will need to wait on both the message queue and the notify queue, we introduce events. The SYS/BIOS event object can be used to wait on multiple input sources.

- Change to notify_peer folder example by enter: cd ~/ti/ipc_nn_nn_nn_nn/examples/DRA7xx_bios_elf/ex13_notifypeer

- Open readme.txt file and follow build instructions step-by-step. Make sure there is no spaces between variable name and its value.

- Run make command in current folder to build DSP1 and HOST notifypeer examples. Output files are created under debug subfolder.

- Launch target configurations. Note that BH560USB_M is emulator is used to connect to AM572X EVM.

- Right click CortexA15_0 and connect target.

- On CCS –> Scripts –> AM572 Multicore Initialization –> Run AM572x Multicore EnableAllCore

- Initialize DDR configuration. On CCS –> Scripts –> DDR configurations –> AM572_DDR3_532MHz_config

- Load DSP1 notifypeer Example out file on DSP1.

- Load HOST notifypeer Example out file on ARM CortexA15_0.

- Run both DSP1 and CortexA15_0.

- On CCS –> Tools –> RTOS Object view (ROV).

- Suspend (halt) ARM CortexA15_0 to view test messages on ROV Viewable Modules –>LoggerBuf. Refer the following image of ROV log messages

- Suspend (halt) DSP2 and click on ROV icon to view log messages.

IPC Ping Example:

ex11_ping

ping example sends a message between all cores in the system. This example is used to exercise every communication path between all processors in the system (including local delivery on the current processor). Ping example is also organized in a suitable manner to develop an application with different compute units on each processor.

Each executable will create two tasks: 1) the server task, and 2) the application task. The server task creates a message queue and then waits on that queue for incoming messages. When a message is received, the server task simply sends it back to the original sender.

The application task creates its own message queue and then opens every server message queue in the system (including the server queue on the local processor). The task sends a message to a server and waits for the message to be returned. This is repeated for each server in the system (including the local server).

Note

Note that presently EVE is not yet supported and therefore, DSP1/DSP2/HOST are built for testing.

1. Change to ping folder example by enter: cd ~/ti/ipc_nn_nn_nn_nn/examples/DRA7xx_bios_elf/ex11_ping

2. Open readme.txt file and follow build instructions step-by-step. Make sure there is no space between variable name and its value.

- Open makefile and remove EVE and IPU from PROC build list.

- Run make command in current folder to build DSP1, DSP2 and HOST ping examples. Output files are created under debug subfolder.

- Launch target configurations. Note that BH560USB_M is emulator is used to connect to AM572X EVM.

- Right click CortexA15_0 and connect target.

- On CCS –> Scripts –> AM572 Multicore Initialization –> Run AM572x Multicore EnableAllCore

- Initialize DDR configuration. On CCS –> Scripts –> DDR configurations –> AM572_DDR3_532MHz_config

- Load DSP1 Ping Example out file on DSP1.

- Load DSP2 Ping Example out file on DSP2.

- Load HOST ping Example onto ARM CortexA15_0

- Run DSP1, DSP2, and HOST images.

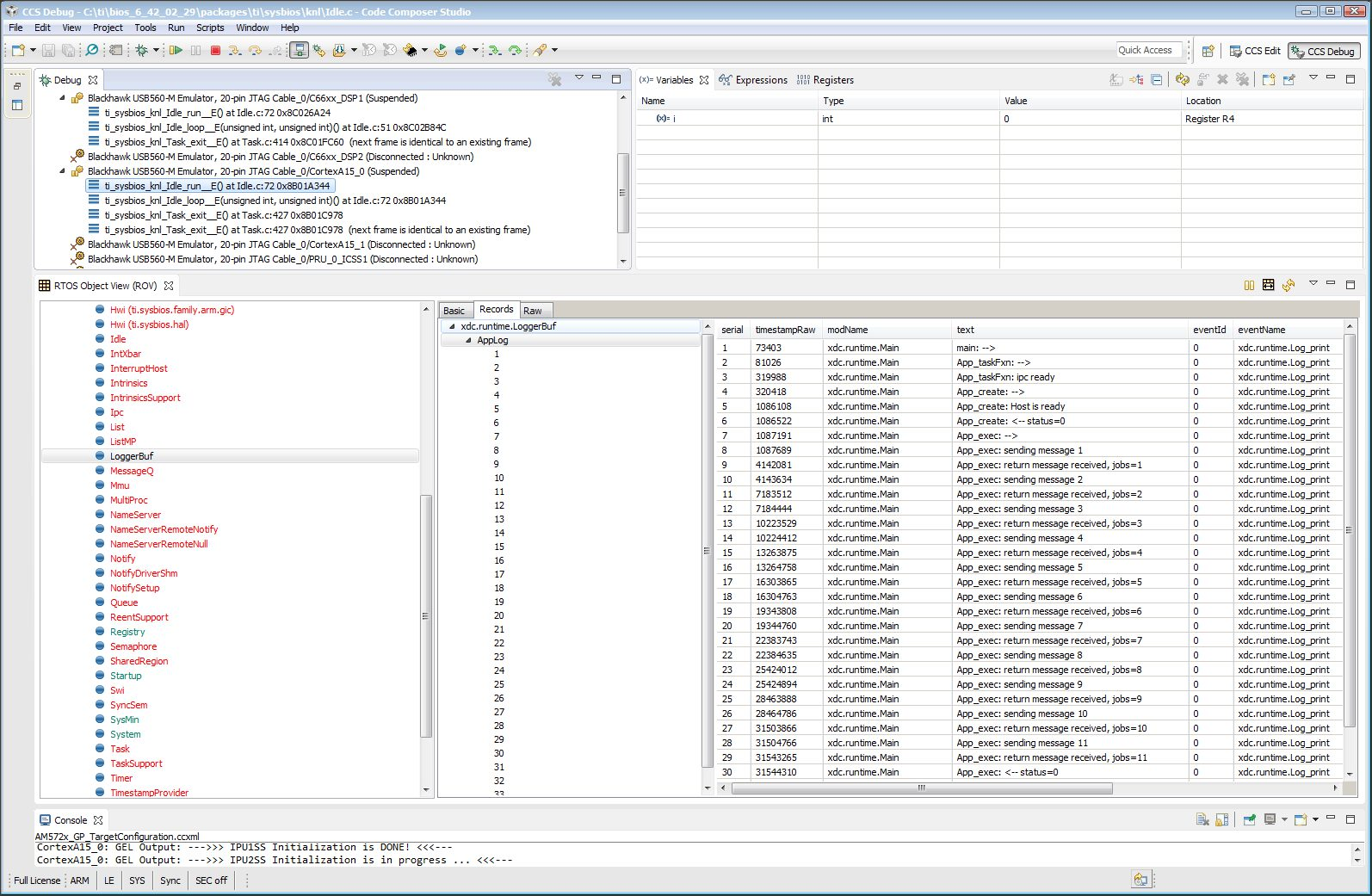

- On CCS –> Tools –> RTOS Object view (ROV).

- Halt DSP1 to view test messages on ROV Viewable Modules –>LoggerBuf Refer below image of ROV log messages

- Suspend (halt) DSP2 and click on ROV icon to view log messages.

- Suspend (halt) ARM CortexA15_0 and click on ROV icon to view log messages.

Expanding IPC Ping Example:

To demonstrate the flexibility of IPC architecture, you may include additional cores to the above example by modifying the make file. For example, you may add IPU1 in the list of processor in the make file as: DSP1, DSP2, IPU1, HOST. After a clean build, the appropriate configuration and output executable files will be generated that allow passing messages between DSP1, DSP2, IPU1 and Host. Procedures are the same as described in the previous example with the exception of additional steps to load the IPU1 core with the corresponding executable and running it in conjunction with DSP1, DSP2 and HOST.

Note

During build process using IPU1, you may encounter a message indicating rtsv7M4_T_le_eabi.lib library is missing. This is a know issue and is being tracked by SDCOM00118417 IR. However, you may create this missing library by going to the compiler installation’s lib directory and execute the following command to regenerate all required libraries:

./mklib --all

The following example depicts a typical host communications protocol with other IPC apps (dsp1, dsp2, ipu1) Note that the following HOST communications list has been rearranged to further clarify the type of communications between various cores. Typically these messages arrive at different intervals depending on each core processes execution time.

1 xdc.runtime.Main --> main:

2 xdc.runtime.Main main: ipc ready

3 xdc.runtime.Main MainHost_svrTskFxn:

4 SvrHost --> SvrHost_setup:

5 SvrHost SvrHost_setup: slave is ready

6 SvrHost <-- SvrHost_setup:

7 SvrHost --> SvrHost_run:

8 xdc.runtime.Main --> MainHost_appTskFxn:

9 AppHost --> AppHost_setup:

10 AppHost AppHost_setup: procId=0 opened server queue

11 AppHost AppHost_setup: procId=1 opened server queue

12 AppHost AppHost_setup: procId=2 opened server queue

28 AppHost AppHost_setup: procId=3 opened server queue

32 AppHost AppHost_run: ping procId=0

34 AppHost AppHost_run: ping procId=0

36 AppHost AppHost_run: ping procId=0

38 AppHost AppHost_run: ping procId=0

40 AppHost AppHost_run: ping procId=0

33 AppHost AppHost_run: ack received procId=0

35 AppHost AppHost_run: ack received procId=0

37 AppHost AppHost_run: ack received procId=0

39 AppHost AppHost_run: ack received procId=0

41 AppHost AppHost_run: ack received procId=0

13 SvrHost SvrHost_run: message received procId=0

14 SvrHost SvrHost_run: message received procId=0

15 SvrHost SvrHost_run: message received procId=0

16 SvrHost SvrHost_run: message received procId=0

17 SvrHost SvrHost_run: message received procId=0

42 AppHost AppHost_run: ping procId=1

44 AppHost AppHost_run: ping procId=1

46 AppHost AppHost_run: ping procId=1

48 AppHost AppHost_run: ping procId=1

50 AppHost AppHost_run: ping procId=1

43 AppHost AppHost_run: ack received procId=1

45 AppHost AppHost_run: ack received procId=1

47 AppHost AppHost_run: ack received procId=1

49 AppHost AppHost_run: ack received procId=1

51 AppHost AppHost_run: ack received procId=1

18 SvrHost SvrHost_run: message received procId=1

19 SvrHost SvrHost_run: message received procId=1

20 SvrHost SvrHost_run: message received procId=1

21 SvrHost SvrHost_run: message received procId=1

22 SvrHost SvrHost_run: message received procId=1

52 AppHost AppHost_run: ping procId=2

55 AppHost AppHost_run: ping procId=2

58 AppHost AppHost_run: ping procId=2

61 AppHost AppHost_run: ping procId=2

64 AppHost AppHost_run: ping procId=2

54 AppHost AppHost_run: ack received procId=2

57 AppHost AppHost_run: ack received procId=2

60 AppHost AppHost_run: ack received procId=2

63 AppHost AppHost_run: ack received procId=2

66 AppHost AppHost_run: ack received procId=2

53 SvrHost SvrHost_run: message received procId=2

56 SvrHost SvrHost_run: message received procId=2

59 SvrHost SvrHost_run: message received procId=2

62 SvrHost SvrHost_run: message received procId=2

65 SvrHost SvrHost_run: message received procId=2

67 AppHost AppHost_run: ping procId=3

69 AppHost AppHost_run: ping procId=3

71 AppHost AppHost_run: ping procId=3

73 AppHost AppHost_run: ping procId=3

75 AppHost AppHost_run: ping procId=3

68 AppHost AppHost_run: ack received procId=3

70 AppHost AppHost_run: ack received procId=3

72 AppHost AppHost_run: ack received procId=3

74 AppHost AppHost_run: ack received procId=3

76 AppHost AppHost_run: ack received procId=3

23 SvrHost SvrHost_run: message received procId=3

24 SvrHost SvrHost_run: message received procId=3

25 SvrHost SvrHost_run: message received procId=3

26 SvrHost SvrHost_run: message received procId=3

27 SvrHost SvrHost_run: message received procId=3

29 AppHost AppHost_setup: slave is ready

30 AppHost <-- AppHost_setup:

31 AppHost --> AppHost_run:

77 AppHost <-- AppHost_run: 0

78 AppHost --> AppHost_destroy:

79 AppHost <-- AppHost_destroy: status=0

80 xdc.runtime.Main <-- MainHost_appTskFxn: 0

81 xdc.runtime.Main MainHost_done:

10.1.2. Run IPC Examples on AM65XX¶

10.1.2.1. AM65xx IPC Examples¶

In the processor SDK release ipc examples can be built from the Processor SDK top level makefile.

See link for building IPC examples

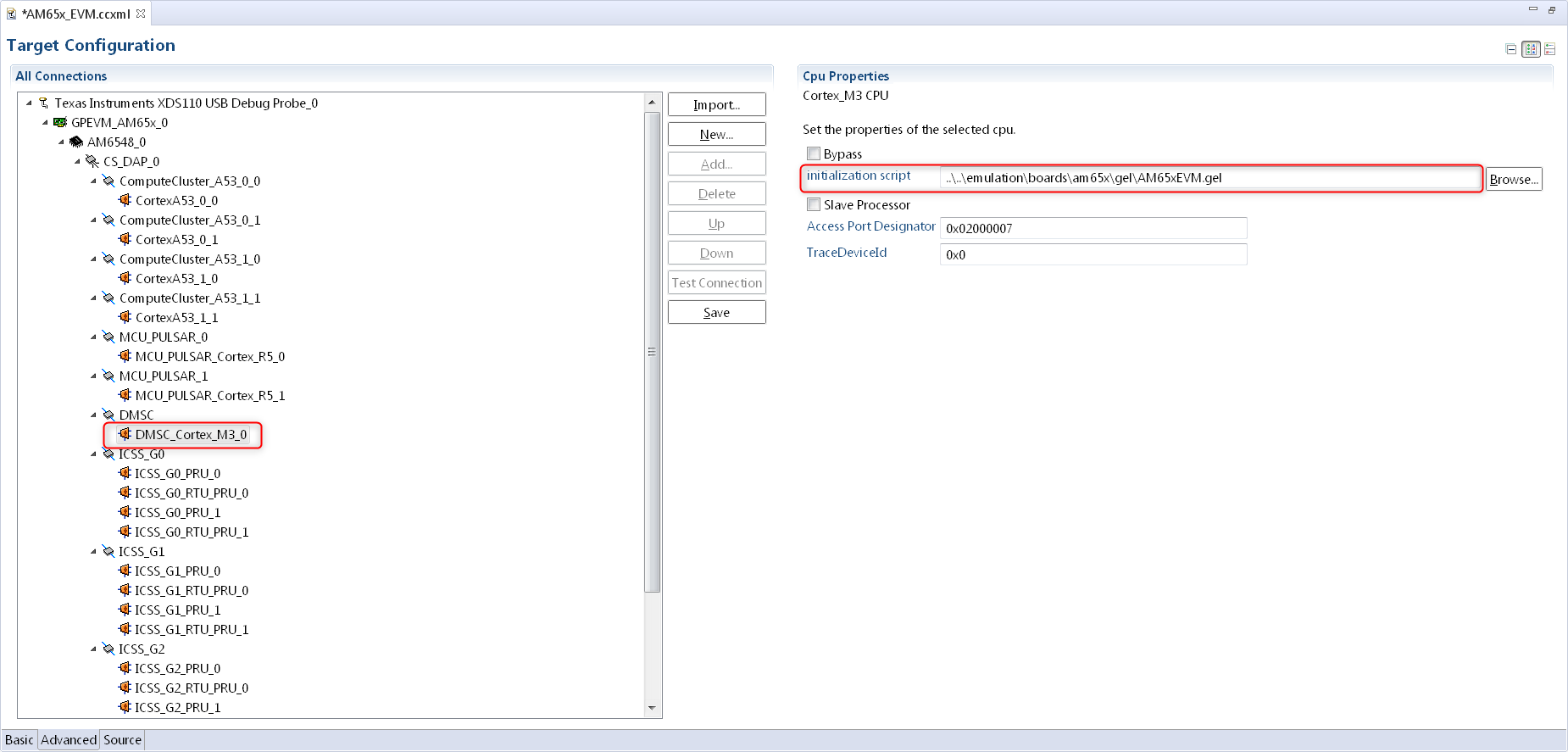

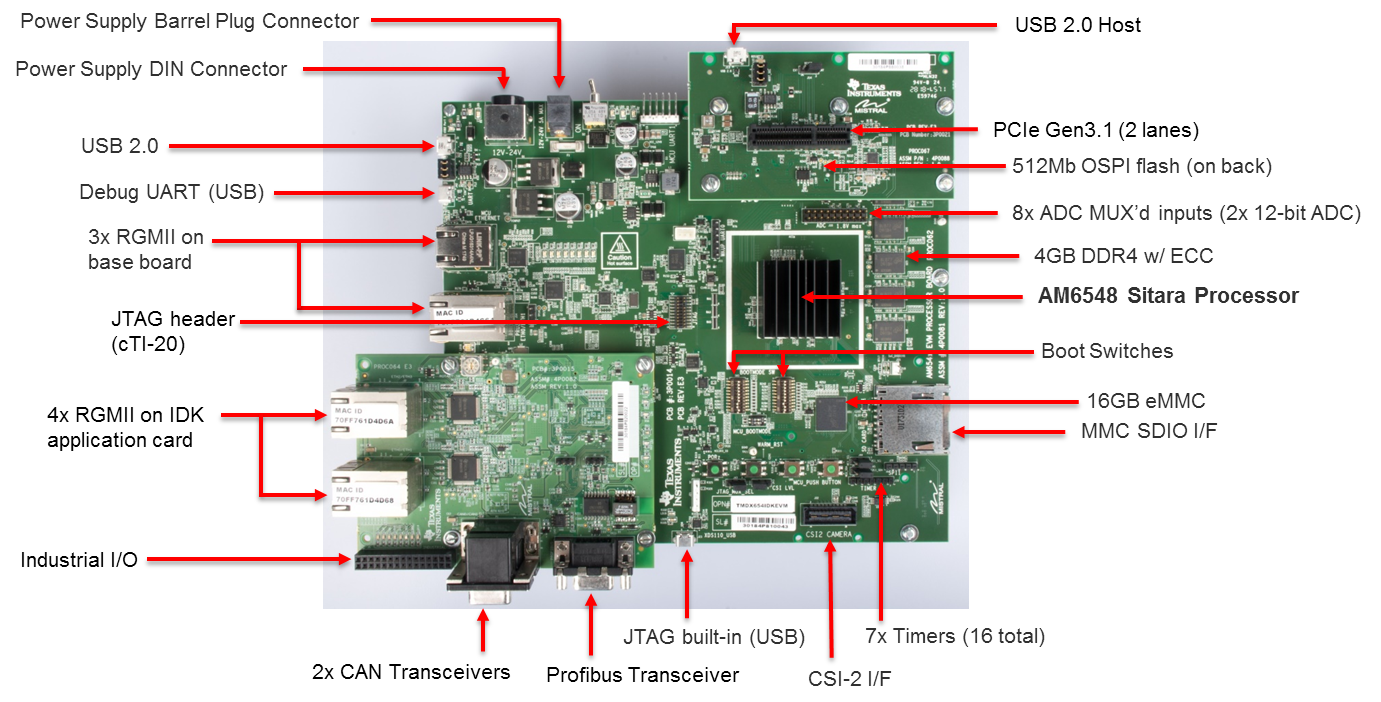

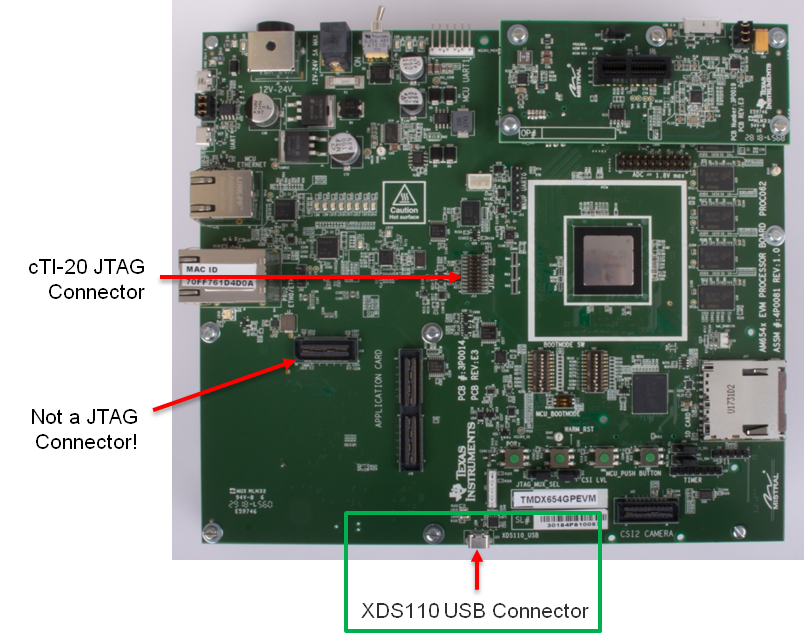

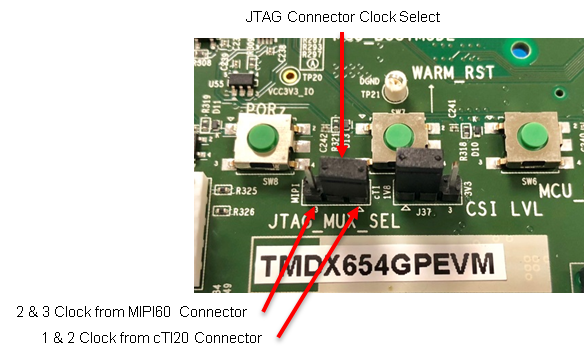

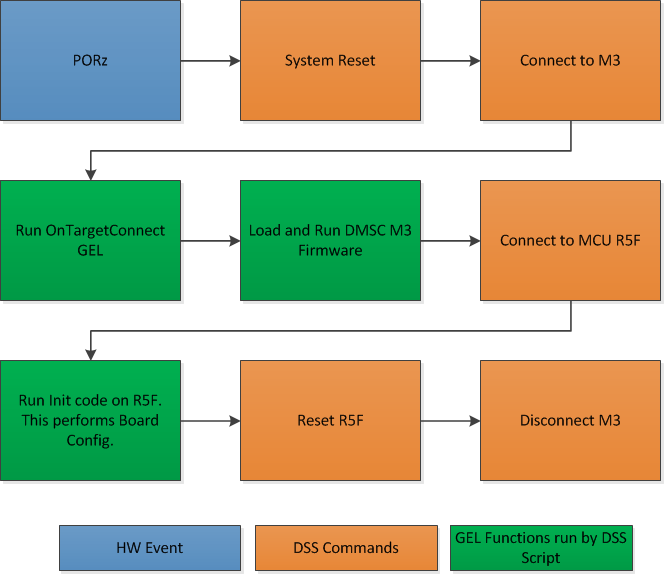

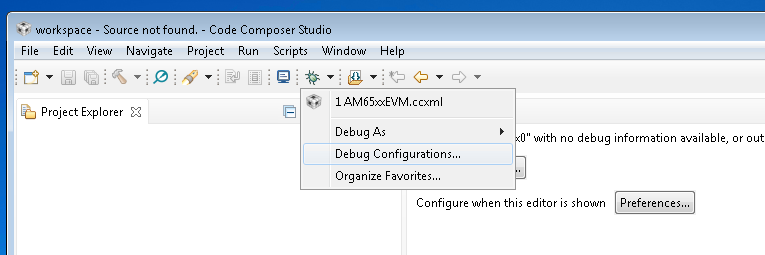

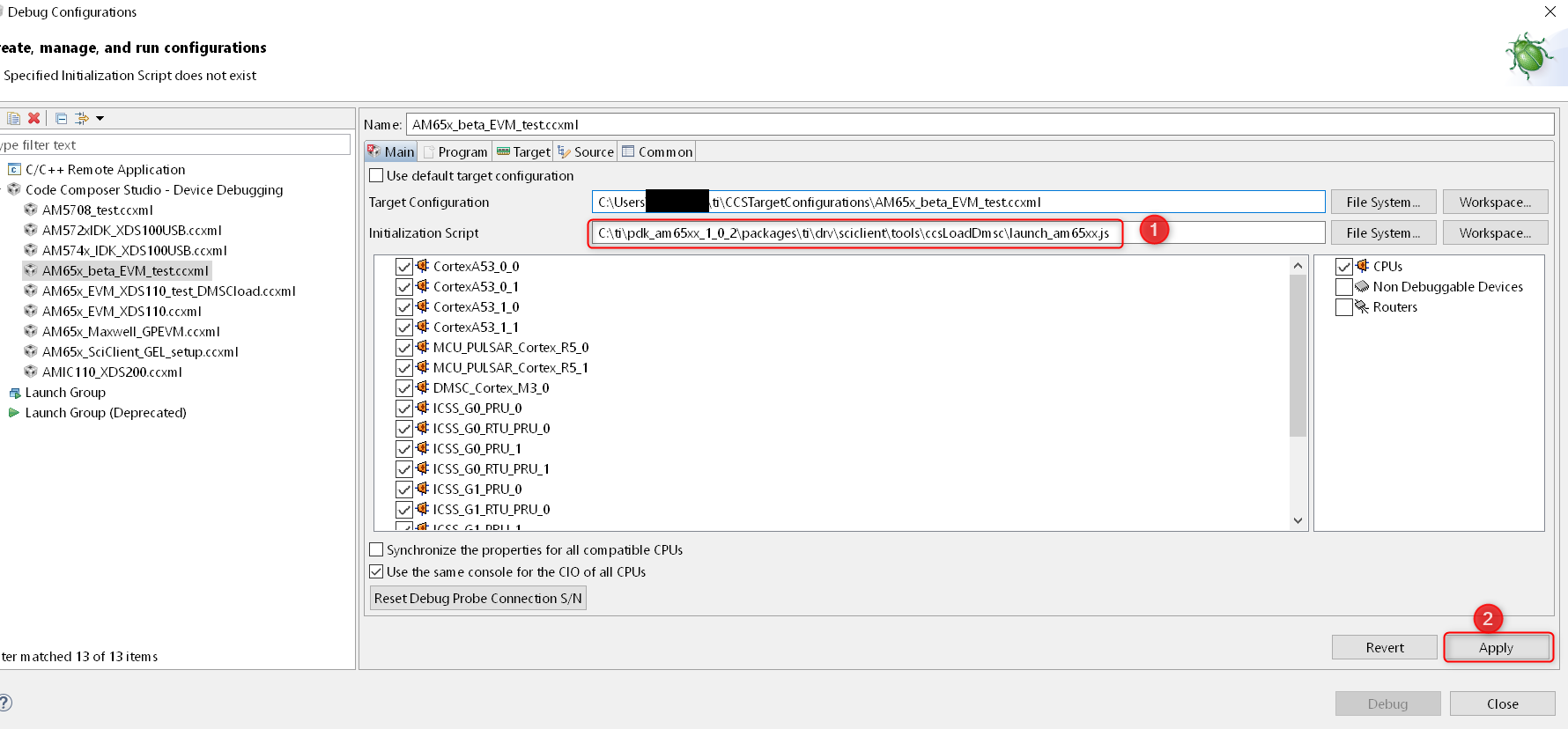

Once the examples are built, they can be run by loading and running the binaries using CCS through JTAG. Please refer to the section “Advanced AM65x Debug Setup with DMSC Firmware Load” of the TMDX654 EVM Hardware Setup Guide for setting up the JTAG.

Advanced AM65x Debug Setup with DMSC Firmware Load

IPC Message Queue Example:

ex02_messageq

Message queue example sends round-trip message from client to server and back. MessageQ example uses client/server pattern. It is a two processors example: the HOST and R5F-0 processor.

The R5F-0 processor is configured as server. It creates a named message queue. The server does not open any queues because it extracts the return address from the message header. The server returns all messages to the sender. It does not access the message pool.

The HOST processor is configured as client application. The client creates an anonymous message queue. The client also creates and manages the message pool. The client’s return address is set in the message header for each message before sending it to the server.

Here are the steps to run the example.

- Follow instructions above to build the IPC examples. The build will create the R5F-0 and HOST binaries under debug and release sub folders For example

- AM65XX_bios_elf\ex02_messageq\host\bin\debug\app_host.xa53fg : HOST A15 binary

- AM65XX_bios_elfex02_messageq\r5f-0\bin\debug\server_r5f-0.xer5fg : R5 binary

- Follow procedure to initialize platform and launch target configuration through steps outlined in the hardware setup guide referred above.

- Right click R5 core 0 and connect target.

- Load R5F-0 messageQ Example out file(server_r5f-0.xer5fg) onto R5F core 0.

- Right click CortexA53_0 and connect target.

- Load HOST messageQ Example out file(app_host.xa53fg) onto ARM CortexA53_0.

- Run both R5F-0 and HOST.

- On CCS –> Tools –> RTOS Object view (ROV).

- Suspend (halt) ARM Cortex_53 to view test messages on ROV Viewable Modules –>LoggerBuf

- Suspend (halt) R5F-0 and click on ROV icon to view log messages.

10.1.3. Taking the C66x Out Of Reset with Linux Running on the ARM A15¶

10.1.3.1. How to take the C66x DSP out of reset with Linux running on A15¶

This document describes the procedure to bring the C66x core out of reset after booting Linux, or at the u-boot prompt.These steps are necessary in to order to load an application on the C66x core, without interfering with the operation of Linux running on the A15.

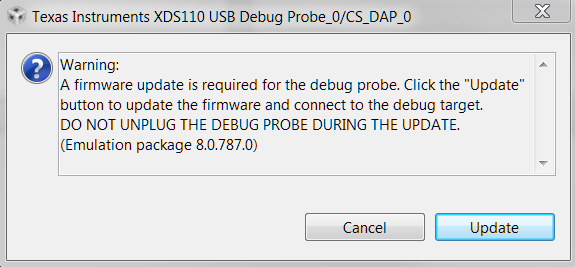

Note

Prior to proceeding with the below instructions, please ensure that the latest Emulation Package is downloaded/installed through CCS. This will ensure the GEL files in your machine has the reset routines described below.

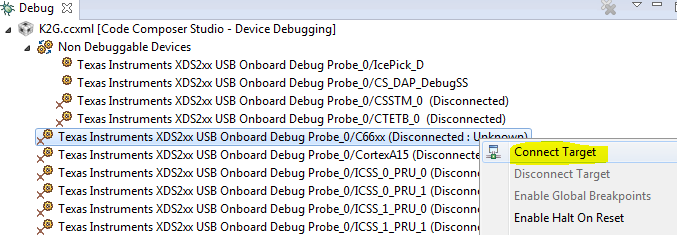

- Once Linux has booted, launch the target configuration.

- With the target configuration launched, right click on K2x.ccxml and select “Show all cores”

- This will bring up the Non-Debuggable Devices section. Right click and connect the CS_DAP_Debug_SS core.

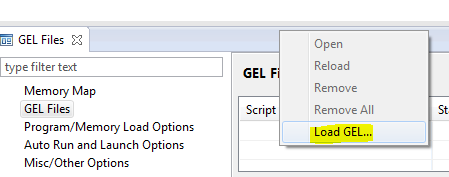

- Go to Tools>GEL files and load the evmk2x.gel file by right clicking on the GEL file window. The Gel file would typically be located in the CCS installation under \ccsv6\ccs_base\emulation\boards\evmk2x\gel\

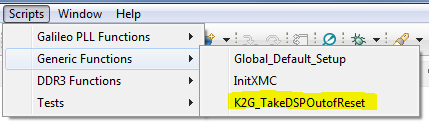

- Once the GEL has been successfully loaded, go to Scripts>default and select K2x_TakeDSPOutofReset.

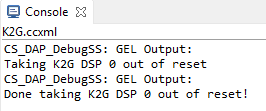

- At this point the console would indicate that the DSP is out of reset.

- Now the DSP cores can be right-clicked and connected successfully.

10.1.3.2. Target Configuration¶

Note

Once the DSP core is connected following the above out of reset routine, the DDR and PLL settings done by u-boot would be overwritten by what’s in the GEL. In order to avoid this, please ensure that the gel is NOT preloaded on the DSP core in the ccxml by leaving the initialization script blank.

10.2. Host¶

10.2.1. Setup¶

10.2.1.1. Setup CCS for EVM and Processor-SDK RTOS¶

10.2.1.1.1. Overview¶

This page provides information on configuring CCS to work with both the EVM and the Processor-SDK for RTOS.

10.2.1.1.2. Discovering SDK products¶

10.2.1.1.2.1. CCS and SDK installed in same directory¶

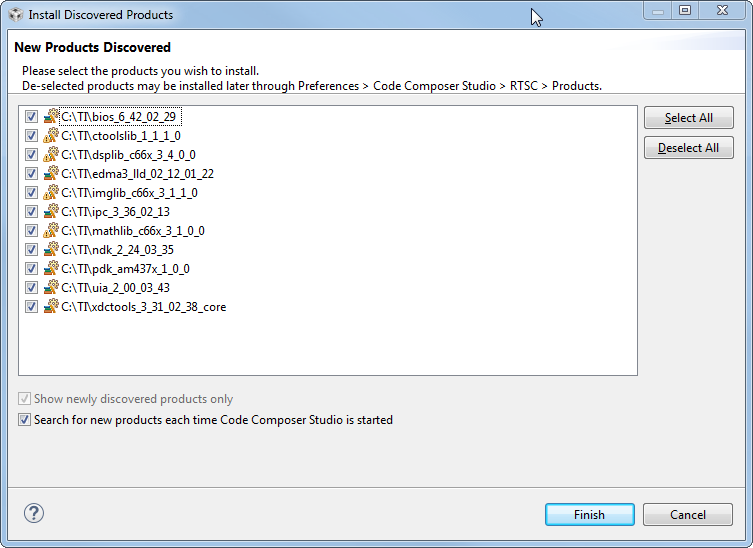

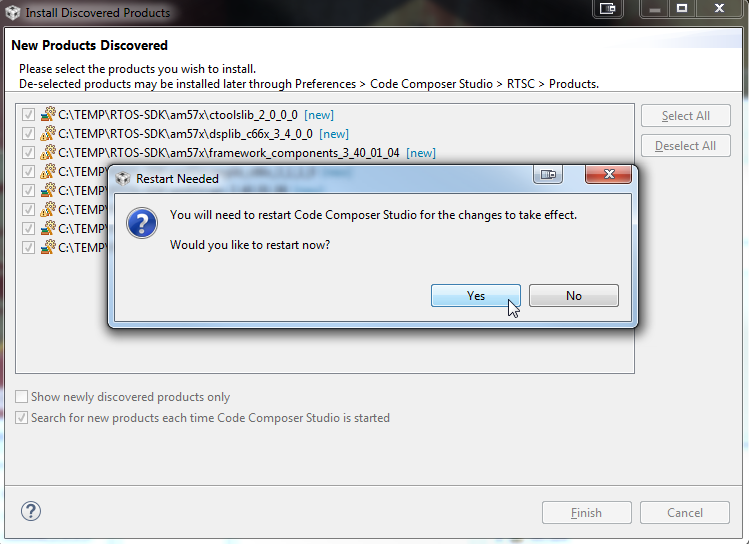

After installing the Processor-SDK RTOS, start CCS and it will automatically detect the newly installed components (products):

10.2.1.1.2.2. CCS and SDK installed in different directories¶

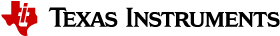

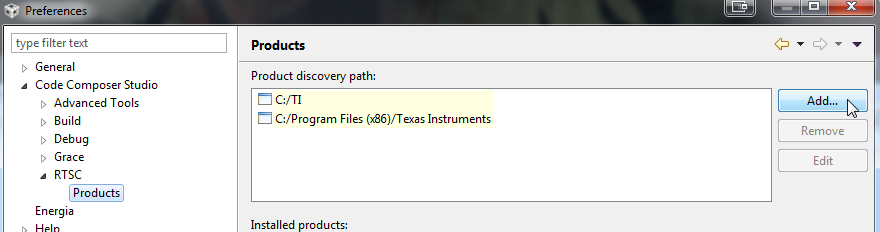

If you chose to install the SDK package in a different folder from where CCS is installed (e.g. C:\TEMP\RTOS-SDK\am57x), then you will need to add the path to the search path for CCS to locate the new packages. The screenshots below demonstrate the process to setup the CCS environment; the sequence for a Linux host is the same.

In the Preferences window, select “Code Composer Studio -> RTSC -> Products” in the panel on the left. Then, press the “Add” button on the panel on the right:

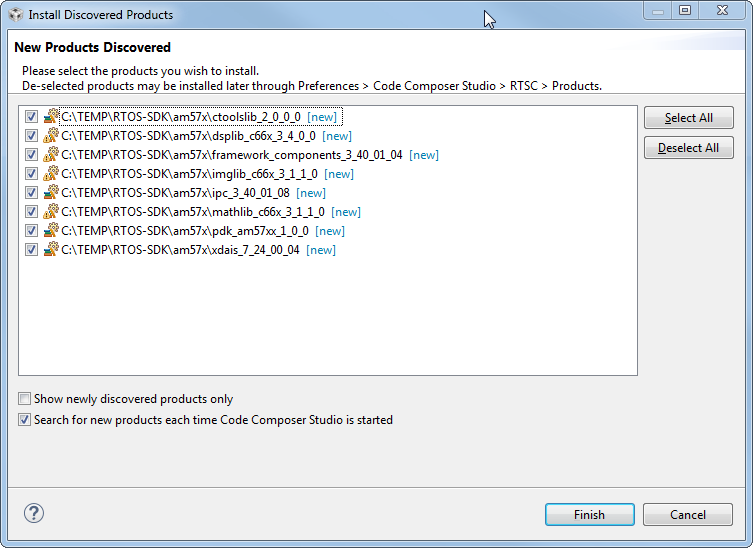

Next, verify the newly discovered products. If everything is correct, press the “Finish” button on the bottom:

When prompted, restart CCS for changes to take effect. You will see newly discovered products from the custom path.

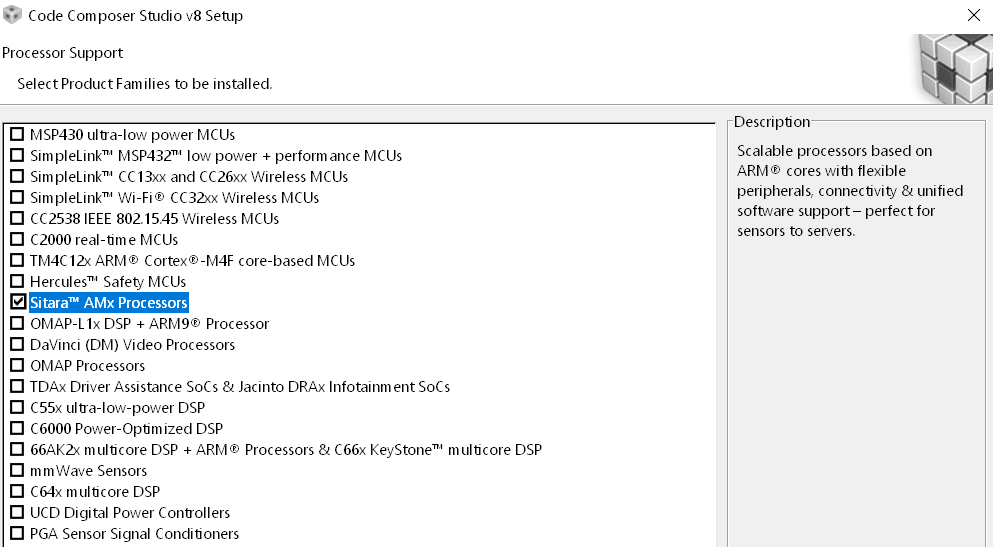

10.2.1.1.2.3. Install Latest Emulation Package and Sitara Device Support Package¶

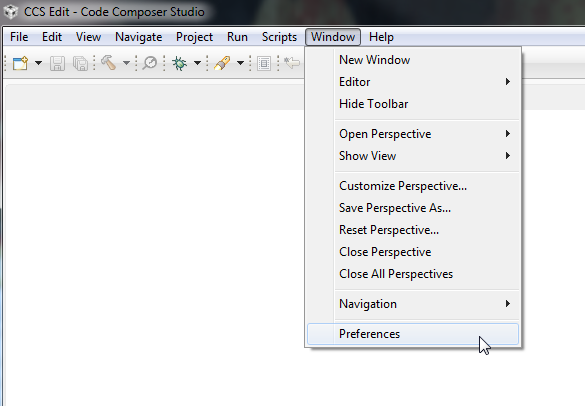

1. In CCS, navigate to Help -> Check for Updates and select “Sitara device support” and “TI Emulators” and click Next.

2. Click “Next” again, select “I accept the terms of the license agreements” and click Finish to begin the installation.

3. You may be prompted to restart CCS for the updates to take effect. Click “Restart Now” when prompted to complete the installation.

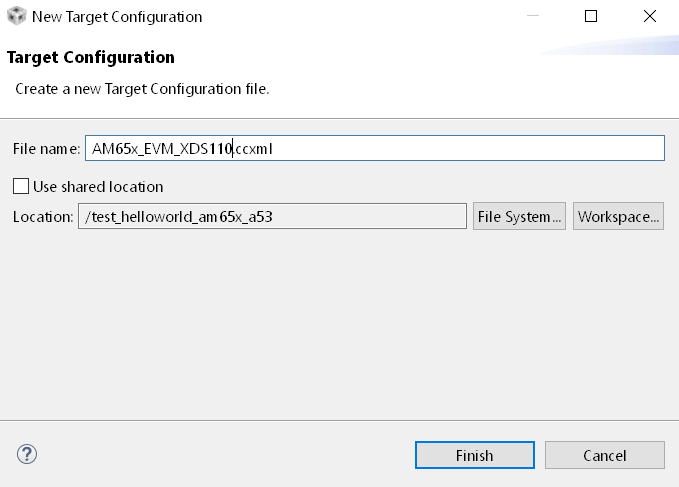

10.2.1.1.2.4. Create Target Configuration File for EVM¶

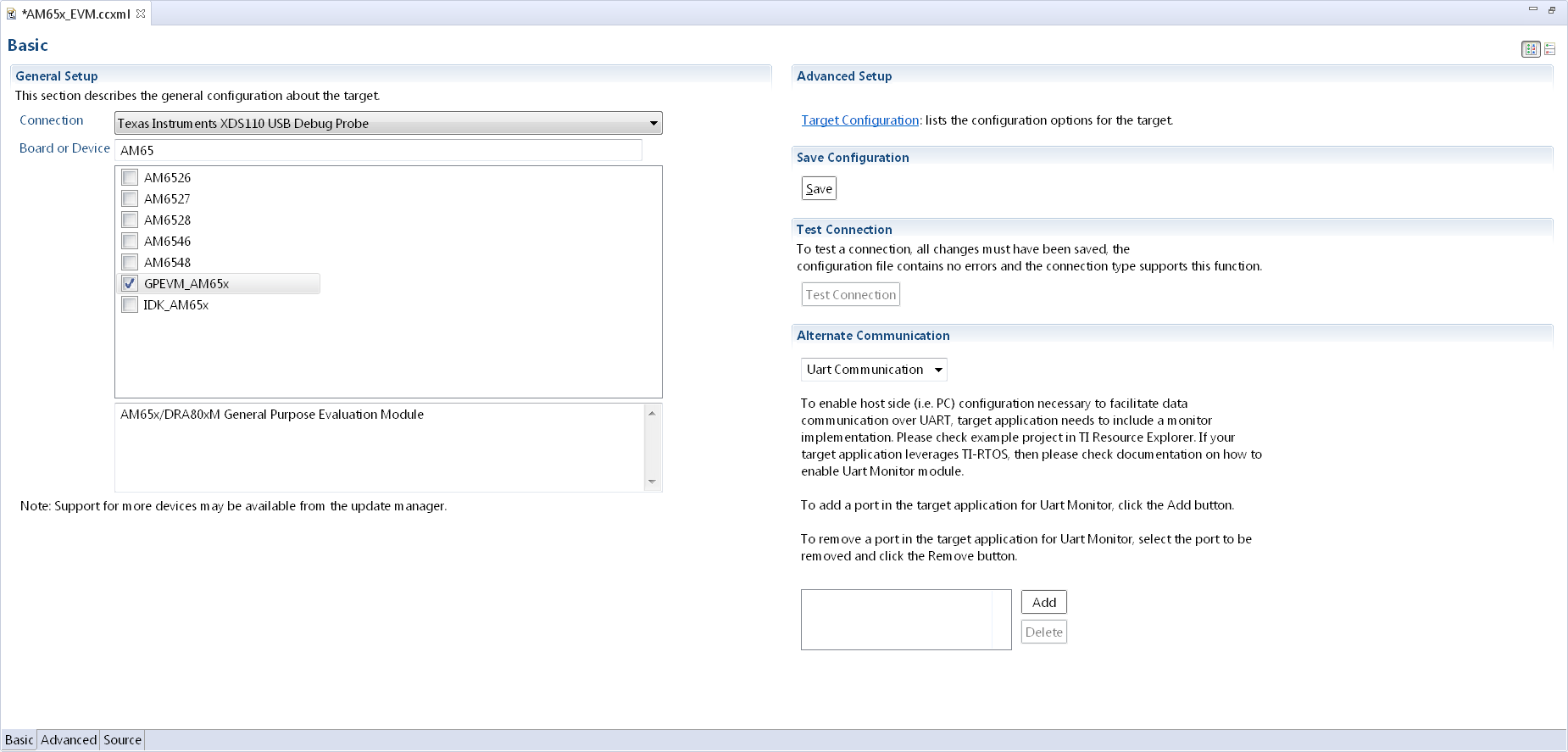

In CCS, you need to create a Target Configuration for your EVM to be able to connect to the target. This configuration defines your:

- Connection to the target (XDS, FET, etc.)

- Target device (AM437x GP EVM, AM57x GP EVM, etc.)

- GEL file for hardware initialization. A GEL file is basically a “batch file” that sets up the CCS debug environment including memory map, PLL, clock, etc.

CCS comes with basic configuration that can be used to configure your particular setup. In the example below, we provide details for a GP AM437x EVM; configuration information for other supported EVMs are also provided as needed.

For EVM specific instructions, refer to the Hardware User’s Guide for your EVM

Note

Note for K2G devices: If using CCS v6.1.2 and Keystone2 device support v1.1.7, 66AK2G02 would not show up in the list of devices when creating the target configuration. This is due to an incompatibility in the XML parser in CCS v6.1.2 with the K2G device xml. In order to work-around this issue, make the change in 66AK2G02.xml as illustrated below in order to have 66AK2G02 display in the device list. This problem does not exist in CCS v6.1.3 onwards as the XML parser has been updated.

C:\ti\ccsv6\ccs_base\common\targetdb\devices\66AK2G02.xml

Line #1

<?xml version="1.1" encoding="UTF-8" standalone="no"?>

to

<?xml version="1.0" encoding="UTF-8" standalone="no"?>

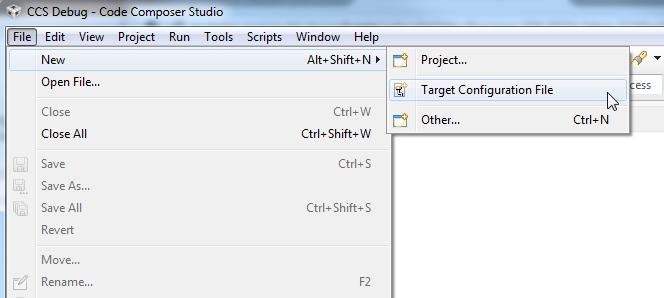

From CCS, select “File -> New -> Target Configuration File”:

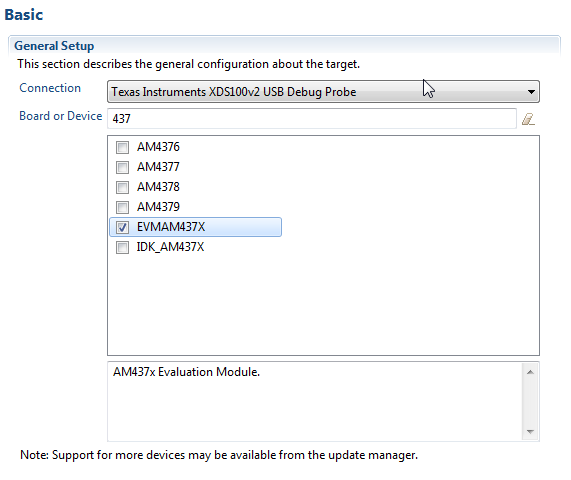

The AM437x GP EVM supports embedded XDS100V2 USB Emulation through the MicroUSB AB connector. Select

- Connection: Texas Instruments XDS100v2 USB Debug Probe

- Board or Device: EVMAM437X

Useful Tip

If you enter the starting numbers of your device in the Board or Device field, the list will show the relevant subset.

Here is a table showing configuration information for all supported EVMs in the Processor-SDK RTOS:

| EVM | Connection | Board |

|---|---|---|

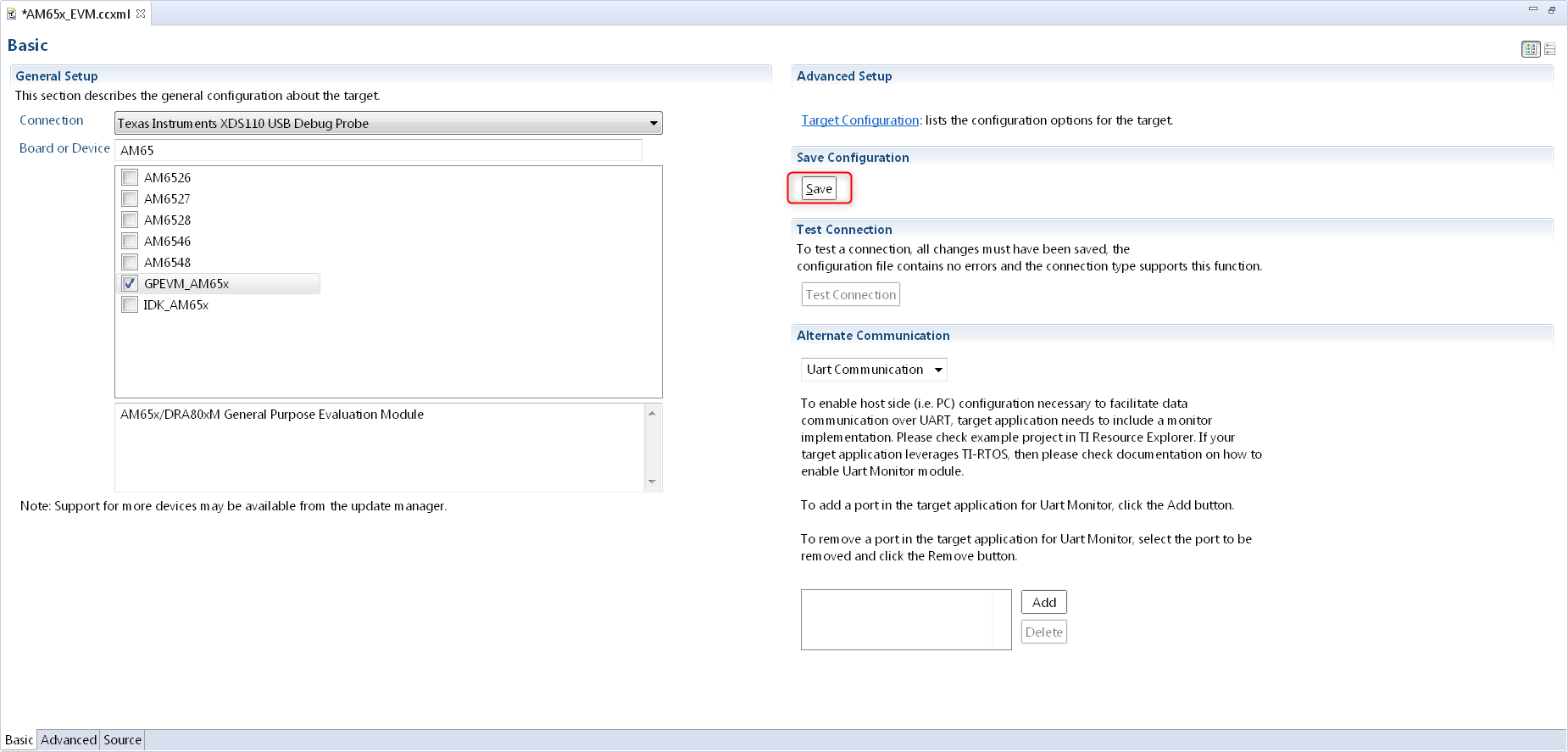

| AM65x EVM | Texas Instruments XDS110 USB Debug Probe | GPEVM_AM65x |

| AM65x IDK | Texas Instruments XDS110 USB Debug Probe | IDK_AM65x |

| GP335x | External Emulator Supplied by User. EVM includes a TI 20 pin JTAG connector. | EVMAM3358 |

| ICE335x | Texas Instruments XDS100v2 USB Debug Probe | ICE_AM3359 |

| SK335x | Texas Instruments XDS100v2 USB Debug Probe | SK_AM3358 |

| BBB | External Emulator Supplied by User. EVM includes a TI 20 pin JTAG connector. | BeagleBone_Black |

| GP437x | Texas Instruments XDS100v2 USB Debug Probe | EVMAM437X |

| IDK437x | Texas Instruments XDS100v2 USB Debug Probe | IDK_AM437X |

| GP572x | External Emulator Supplied by User. EVM includes a TI 20 pin JTAG connector. | GPEVM_AM572X |

| X15 | External Emulator Supplied by User. EVM includes a TI 20 pin JTAG connector. | GPEVM_AM572X |

| IDK572x/IDK574x | Texas Instruments XDS100V2 USB Debug Probe External Emulator Supplied by User. EVM includes a 60-pin MIPI JTAG connector | IDK_AM572X/IDK_AM574X |

| C665x EVM | Texas Instruments XDS2xx USB Onboard Debug Probe | TMS320C6657 |

| C667x EVM | L w/ XDC100: Texas Instruments XDS100v1 USB Emulator LE/LXE with XDS560: Blackhawk XDS560v2-USB Mezzanine Emulator | TMS320C6678 |

| K2E EVM | Texas Instruments XDS2xx USB Onboard Debug Probe | 66AK2E05 |

| K2H EVM | Texas Instruments XDS2xx USB Onboard Debug Probe | 66AK2H12 |

| K2L EVM | Texas Instruments XDS2xx USB Onboard Debug Probe | TCI6630K2L |

| K2G GP EVM | Texas Instruments XDS2xx USB Onboard Debug Probe | 66AK2G02 |

| OMAPL137 EVM | Spectrum Digital XDS510USB Emulator | OMAPL137SK |

| OMAPL138 LCDK | External Emulator Supplied by User. EVM includes a TI 14 pin JTAG connector. | OMAPL138LCDK |

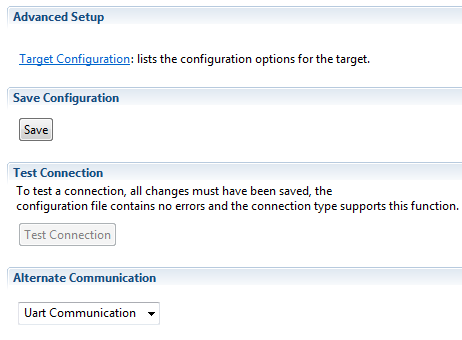

Next, save the target configuration by pressing the Save button:

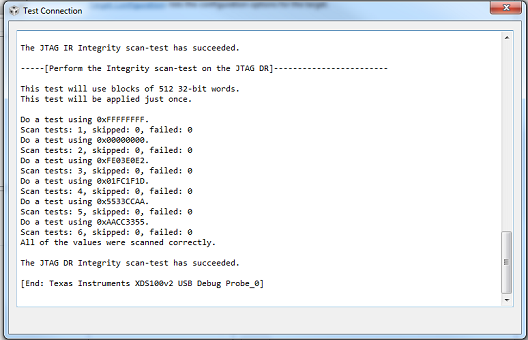

Next, test the target configuration by pressing the Test Connection button. This will confirm that you have successfully created an emulator connection with your board.

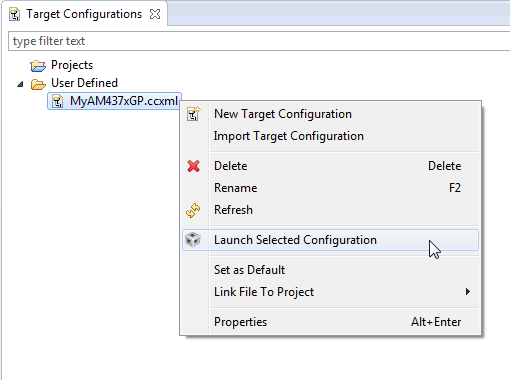

Open “User Defined” list and right click on the target configuration file that was just saved and select “Launch Selected Configuration”:

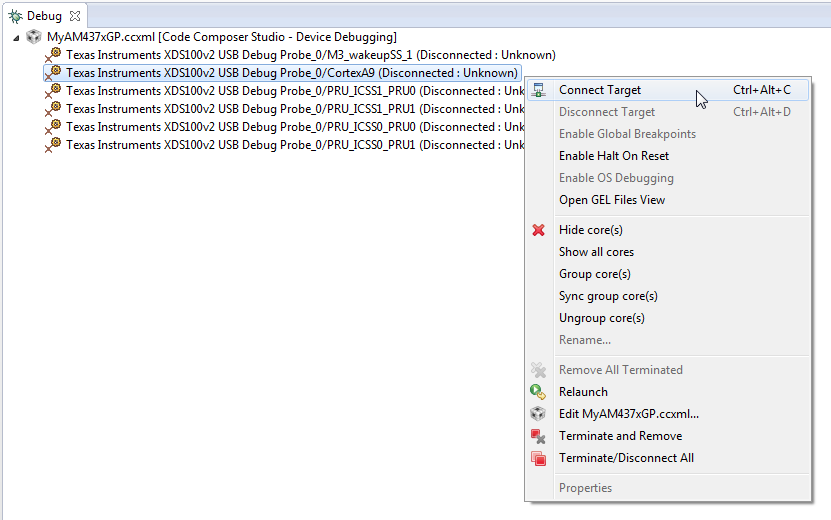

After launch, you can connect to a core. For GP AM437x EVM, select Cortex A9 and select “Connect Target”:

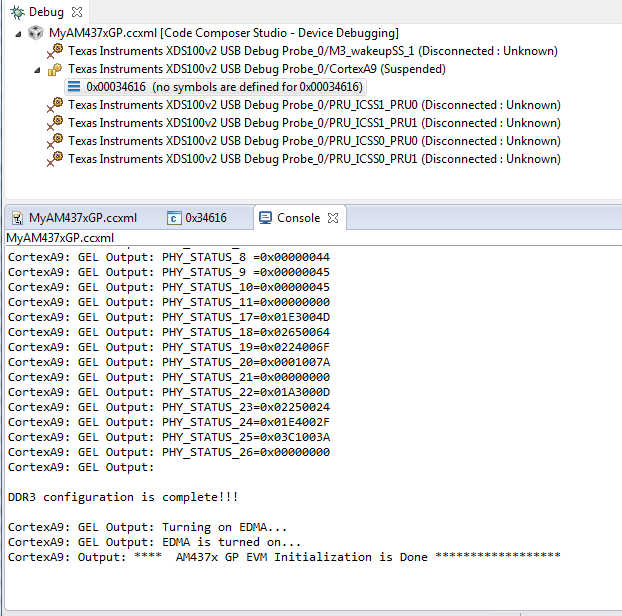

After connecting to target, check the console for status. Typically, the end of the configuration will indicate success or failure. For GP AM437x EVM, you will see the message “AM437x GP EVM Initialization is Done”:

10.2.1.1.2.5. Additional Notes for AM57x¶

After connecting to the boot master core – typically the ARM core – you may need to connect to a slave core in order to run code. Depending on your SOC, the slave core can be

- DSP C66x

- ARM M4

- PRUSS

- IVAHD

Typically the slave cores will wait in reset state until the master core

wakes up the slave core to run code. To connect to the slave core on

AM57x, go to Scripts menu in CCS Debug View and under AM572x

MULTICORE Initialization enable the corresponding sub system clock.

For example, enable DSP11SSClkEnable_API for the first DSP core.

After running the clock enable option, you can connect to the core.

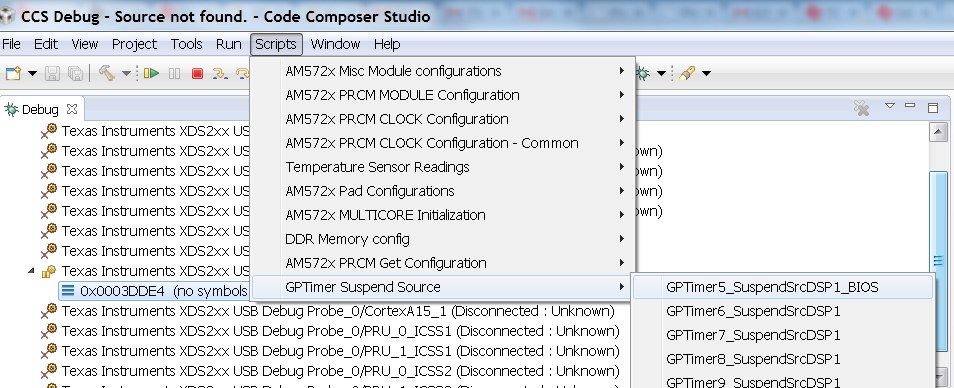

On AM57xx devices, all the timers on the chip have their suspend control signal routed to the A15 core. Which means that if any of the slave cores are using these timers, the timers will continue to run even when the slave core has been paused. The timer will only pause when the A15 core is halted.

This is confusing while debugging code on slave cores if you are relying on timer for logging, inserting delays or if the timer keeps firing interrupts even when the core is halted. One such scenario occurs with GPtimer5 when DSP developers are using SYS/BIOS. The OS uses GPtimer5 on the DSP and forces a frequency check to confirm the timer configuration, however the OS can’t gain access to the timer due to the hook up of the suspend control signals.

Due to this issue the SYS/BIOS developers will need to configure an additional CCS configuration check to connect the GPTimer suspend control signal to the DSP as shown in the image below:

10.2.1.1.2.6. Troubleshooting¶

If you face any problems, first check these basic items:

- Power cycle your target.

- Check the USB cable. One simple way to do this is to connect another device to the USB and ensure the cable works.

- Check host driver. Even with CCS turned off, your host should list the TI XDS as a USB device. If this does not work, try a different USB port.

- Latest emulation package. Ensure that you have the latest emulation files as specified in the Getting Started Guide.

If this does not resolve your problem, see these additional resources:

10.2.1.2. Update environment when installing to a custom path¶

10.2.1.2.1. Overview¶

This page will provide configuration information if the SDK is installed in a custom path.

Useful Tip

To avoid changing environment variable for each new shell, modify environment variable file directly. This file is the setupenv file located in the SDK root directory.

10.2.1.2.2. Changes to CCS Configuration¶

Installing the SDK in a folder other than where CCS is installed will require modifications to CCS to be able to discover the SDK. See the Setup CCS How To page explaining how to update CCS configuration.

10.2.1.2.3. Rebuilding the SDK RTOS¶

Installing the SDK in a folder other than the default (C:\TI for

Windows, /home/[user]/ti for Linux) requires modifications to SDK

RTOS scripts in order for recompilation and example/test creation to

work properly.

In all the commands below, replace [version] with the appropriate version of the software/tool.

10.2.1.2.3.1. CCS in Custom Path and SDK RTOS in Default Path¶

CCS installation and toolchain paths can be customized by setting the TOOLS_INSTALL_PATH environment variable prior to running the SDK level setupenv script. This feature is used if CCS and the toolchains are installed somewhere other than the default C:\ti location.

For example, environment configuration assuming CCS is installed to [os_base]\ti_temp and SDK RTOS has been installed to default path, [os_base]\ti :

- Windows

C:\> set TOOLS_INSTALL_PATH=C:\ti_temp

C:\> cd C:\ti\processor_sdk_rtos_[soc]_[version]

C:\ti\processor_sdk_rtos_[soc]_[version]> setupenv.bat

Gives the output:

Optional parameter not configured : CG_XML_BIN_INSTALL_PATH

REQUIRED for xdc release build

Example: set CG_XML_BIN_INSTALL_PATH=C:/ti/cg_xml/bin

Optional parameter not configured : DOXYGEN_INSTALL_PATH

REQUIRED for xdc release build

Example: set DOXYGEN_INSTALL_PATH=C:/ti/Doxygen/doxygen/1.5.1-p1/bin

**************************************************************************

Environment Configuration:

PDK Directory : /ti/PDK_AM~3/packages/

CGTOOL INSTALL Directory : C:/ti_temp/ccsv6/tools/compiler/ti-cgt-c6000_[version]

TOOLCHAIN A15 Directory : C:/ti_temp/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A8 Directory : C:/ti_temp/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A9 Directory : C:/ti_temp/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN M4 Directory : C:/ti_temp/ccsv6/tools/compiler/ti-cgt-arm_[version]

FPULIB_PATH : C:/ti_temp/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]/lib/gcc/arm-none-eabi/[version]/fpu

CROSS_TOOL_PRFX : arm-none-eabi-

XDC_INSTALL_PATH : C:/ti/xdctools_[version]_core

BIOS_INSTALL_PATH : C:/ti/bios_[version]

IPC_INSTALL_PATH : C:/ti/ipc_[version]

EDMA3LLD_BIOS6_INSTALLDIR : C:/ti/edma3_lld_[version]

NDK_INSTALL_PATH : C:/ti/ndk_[version]

IMGLIB_INSTALL_PATH : C:/ti/imglib_c66x_[version]

UIA_INSTALL_PATH : C:/ti/uia_[version]

PROC_SDK_INSTALL_PATH : C:/ti/processor_sdk_rtos_[soc]_[version]

**************************************************************************

Changing to short name to support directory names containing spaces

current directory: C:/ti/processor_sdk_rtos_[soc]_[version]

PROCESSOR SDK BUILD ENVIRONMENT CONFIGURED

**************************************************************************

- Linux

$ export TOOLS_INSTALL_PATH=~/ti_temp

$ cd ~/ti/processor_sdk_rtos_[soc]_[version]/

~/ti/processor_sdk_rtos_[soc]_[version]$ source setupenv.sh

Gives the output:

Optional parameter not configured : CG_XML_BIN_INSTALL_PATH

REQUIRED for xdc release build

Example: export CG_XML_BIN_INSTALL_PATH="~/ti/cg_xml/bin"

Optional parameter not configured : DOXYGEN_INSTALL_PATH

REQUIRED for xdc release build

Example: export DOXYGEN_INSTALL_PATH="~/ti/Doxygen/doxygen/1.5.1-p1/bin"

**************************************************************************

Environment Configuration:

PDK Directory : /home/[user]/ti/pdk_[soc]_[version]/packages

CGTOOL INSTALL Directory : /home/[user]/ti_temp/ccsv6/tools/compiler/ti-cgt-c6000_[version]

TOOLCHAIN A15 Directory : /home/[user]/ti_temp/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A8 Directory : /home/[user]/ti_temp/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A9 Directory : /home/[user]/ti_temp/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN M4 Directory : /home/[user]/ti_temp/ccsv6/tools/compiler/ti-cgt-arm_[version]

FPULIB_PATH : /home/[user]/ti_temp/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]/lib/gcc/arm-none-eabi/[version]/fpu

CROSS_TOOL_PRFX : arm-none-eabi-

XDC_INSTALL_PATH : /home/[user]/ti/xdctools_[version]_core

BIOS_INSTALL_PATH : /home/[user]/ti/bios_[version]

IPC_INSTALL_PATH : /home/[user]/ti/ipc_[version]

EDMA3LLD_BIOS6_INSTALLDIR : /home/[user]/ti/edma3_lld_[version]

NDK_INSTALL_PATH : /home/[user]/ti/ndk_[version]

IMGLIB_INSTALL_PATH : /home/[user]/ti/imglib_c66x_[version]

UIA_INSTALL_PATH : /home/[user]/ti/uia_[version]

PROC_SDK_INSTALL_PATH : /home/[user]/ti/processor_sdk_rtos_[soc]_[version]

PROCESSOR SDK BUILD ENVIRONMENT CONFIGURED

*******************************************************************************

The RTOS SDK top level Makefile can now be used to rebuild SDK RTOS components with CCS and toolchains installed in a custom installation path.

10.2.1.2.3.2. CCS in Default Path and SDK RTOS in Custom Path¶

SDK RTOS component installation paths can be customized by setting the

SDK_INSTALL_PATH variable prior to running the SDK level setupenv

script. This feature is used if the SDK is installed somewhere other

than the default C:\ti location.

For example, environment configuration assuming CCS is installed to the

default path, [os_base]\ti and SDK RTOS has been installed to

[os_base]\ti_temp:

- Windows

C:\> set SDK_INSTALL_PATH=C:/ti_temp

C:\> cd C:\ti_temp\processor_sdk_rtos_[soc]_[version]

C:\ti_temp\processor_sdk_rtos_[soc]_[version]> setupenv.bat

Gives the output:

Optional parameter not configured : CG_XML_BIN_INSTALL_PATH

REQUIRED for xdc release build

Example: set CG_XML_BIN_INSTALL_PATH=C:/ti/cg_xml/bin

Optional parameter not configured : DOXYGEN_INSTALL_PATH

REQUIRED for xdc release build

Example: set DOXYGEN_INSTALL_PATH=C:/ti/Doxygen/doxygen/1.5.1-p1/bin

**************************************************************************

Environment Configuration:

PDK Directory : /ti_temp/PDK_AM~3/packages/

CGTOOL INSTALL Directory : C:/ti/ccsv6/tools/compiler/ti-cgt-c6000_[version]

TOOLCHAIN A15 Directory : C:/ti/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A8 Directory : C:/ti/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A9 Directory : C:/ti/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN M4 Directory : C:/ti/ccsv6/tools/compiler/ti-cgt-arm_[version]

FPULIB_PATH : C:/ti/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]/lib/gcc/arm-none-eabi/[version]/fpu

CROSS_TOOL_PRFX : arm-none-eabi-

XDC_INSTALL_PATH : C:/ti_temp/xdctools_[version]_core

BIOS_INSTALL_PATH : C:/ti_temp/bios_[version]

IPC_INSTALL_PATH : C:/ti_temp/ipc_[version]

EDMA3LLD_BIOS6_INSTALLDIR : C:/ti_temp/edma3_lld_[version]

NDK_INSTALL_PATH : C:/ti_temp/ndk_[version]

IMGLIB_INSTALL_PATH : C:/ti_temp/imglib_c66x_[version]

UIA_INSTALL_PATH : C:/ti_temp/uia_[version]

PROC_SDK_INSTALL_PATH : C:/ti_temp/processor_sdk_rtos_[soc]_[version]

**************************************************************************

Changing to short name to support directory names containing spaces

current directory: C:/ti_temp/processor_sdk_rtos_[soc]_[version]

PROCESSOR SDK BUILD ENVIRONMENT CONFIGURED

**************************************************************************

- Linux

$ export SDK_INSTALL_PATH=~/ti_temp

$ cd ~/ti_temp/processor_sdk_rtos_[soc]_[version]/

~/ti_temp/processor_sdk_rtos_[soc]_[version]$ source setupenv.sh

Gives the output:

Optional parameter not configured : CG_XML_BIN_INSTALL_PATH

REQUIRED for xdc release build

Example: export CG_XML_BIN_INSTALL_PATH="~/ti/cg_xml/bin"

Optional parameter not configured : DOXYGEN_INSTALL_PATH

REQUIRED for xdc release build

Example: export DOXYGEN_INSTALL_PATH="~/ti/Doxygen/doxygen/1.5.1-p1/bin"

**************************************************************************

Environment Configuration:

PDK Directory : /home/[user]/ti_temp/pdk_[soc]_[version]/packages

CGTOOL INSTALL Directory : /home/[user]/ti/ccsv6/tools/compiler/ti-cgt-c6000_[version]

TOOLCHAIN A15 Directory : /home/[user]/ti/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A8 Directory : /home/[user]/ti/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A9 Directory : /home/[user]/ti/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN M4 Directory : /home/[user]/ti/ccsv6/tools/compiler/ti-cgt-arm_[version]

FPULIB_PATH : /home/[user]/ti/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]/lib/gcc/arm-none-eabi/[version]/fpu

CROSS_TOOL_PRFX : arm-none-eabi-

XDC_INSTALL_PATH : /home/[user]/ti_temp/xdctools_[version]_core

BIOS_INSTALL_PATH : /home/[user]/ti_temp/bios_[version]

IPC_INSTALL_PATH : /home/[user]/ti_temp/ipc_[version]

EDMA3LLD_BIOS6_INSTALLDIR : /home/[user]/ti_temp/edma3_lld_[version]

NDK_INSTALL_PATH : /home/[user]/ti_temp/ndk_[version]

IMGLIB_INSTALL_PATH : /home/[user]/ti_temp/imglib_c66x_[version]

UIA_INSTALL_PATH : /home/[user]/ti_temp/uia_[version]

PROC_SDK_INSTALL_PATH : /home/[user]/ti_temp/processor_sdk_rtos_[soc]_[version]

PROCESSOR SDK BUILD ENVIRONMENT CONFIGURED

*******************************************************************************

The RTOS SDK top level Makefile can now be used to rebuild SDK RTOS components installed in the custom installation path.

Note

The following known issue impacts this step: PRSDK-1263: PDK AM437x: Make fails on Windows if CCS is installed in custom path. Workaround: Edit the UTILS_INSTALL_DIR variable in <pdk_root_dir>/packages/ti/starterware/Rules.make to point to the CCS installation on your Windows PC.

10.2.1.2.3.3. CCS and SDK RTOS in Custom Path¶

When CCS and the SDK RTOS are both installed to custom paths the SDK can be rebuilt by setting the SDK_INSTALL_PATH and TOOLS_INSTALL_PATH variables prior to running the SDK RTOS top level environment setup script. The Windows and Linux environment setup scripts can be found in the following locations, respectively:

- Windows - C:\custom\install\path\processor_sdk_rtos_[soc]_[version]\setupenv.bat

- Linux - /home/[user]/custom/install/path/processor_sdk_rtos_[soc]_[version]/setupenv.sh

The SDK_INSTALL_PATH and TOOLS_INSTALL_PATH environment variables must be set to the custom install path prior to running the environment setup script.

For example, environment configuration assuming CCS and the SDK have been installed to [os_base]\new_sdk_release\ :

- Windows

C:\> set SDK_INSTALL_PATH=C:\new_sdk_release

C:\> set TOOLS_INSTALL_PATH=C:\new_sdk_release

C:\> cd C:\new_sdk_release\processor_sdk_rtos_[soc]_[version]

C:\new_sdk_release\processor_sdk_rtos_[soc]_[version]> setupenv.bat

Gives the output:

Optional parameter not configured : CG_XML_BIN_INSTALL_PATH

REQUIRED for xdc release build

Example: set CG_XML_BIN_INSTALL_PATH=C:/ti/cg_xml/bin

Optional parameter not configured : DOXYGEN_INSTALL_PATH

REQUIRED for xdc release build

Example: set DOXYGEN_INSTALL_PATH=C:/ti/Doxygen/doxygen/1.5.1-p1/bin

**************************************************************************

Environment Configuration:

PDK Directory : /NEW_SD~1/PDK_AM~1/packages/

CGTOOL INSTALL Directory : C:/new_sdk_release/ccsv6/tools/compiler/ti-cgt-c6000_[version]

TOOLCHAIN A15 Directory : C:/new_sdk_release/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A8 Directory : C:/new_sdk_release/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A9 Directory : C:/new_sdk_release/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN M4 Directory : C:/new_sdk_release/ccsv6/tools/compiler/ti-cgt-arm_[version]

FPULIB_PATH : C:/new_sdk_release/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]/lib/gcc/arm-none-eabi/[version]/fpu

CROSS_TOOL_PRFX : arm-none-eabi-

XDC_INSTALL_PATH : C:/new_sdk_release/xdctools_[version]_core

BIOS_INSTALL_PATH : C:/new_sdk_release/bios_[version]

IPC_INSTALL_PATH : C:/new_sdk_release/ipc_[version]

EDMA3LLD_BIOS6_INSTALLDIR : C:/new_sdk_release/edma3_lld_[version]

NDK_INSTALL_PATH : C:/new_sdk_release/ndk_[version]

IMGLIB_INSTALL_PATH : C:/new_sdk_release/imglib_c66x_[version]

UIA_INSTALL_PATH : C:/new_sdk_release/uia_[version]

PROC_SDK_INSTALL_PATH : C:/new_sdk_release/processor_sdk_rtos_[soc]_[version]

**************************************************************************

Changing to short name to support directory names containing spaces

current directory: C:/new_sdk_release/processor_sdk_rtos_[soc]_[version]

PROCESSOR SDK BUILD ENVIRONMENT CONFIGURED

**************************************************************************

- Linux

$ export SDK_INSTALL_PATH=~/new_sdk_release

$ export TOOLS_INSTALL_PATH=~/new_sdk_release

$ cd ~/new_sdk_release/processor_sdk_rtos_[soc]_[version]/

~/new_sdk_release/processor_sdk_rtos_[soc]_[version]$ source setupenv.sh

Gives the output:

Optional parameter not configured : CG_XML_BIN_INSTALL_PATH

REQUIRED for xdc release build

Example: export CG_XML_BIN_INSTALL_PATH="~/ti/cg_xml/bin"

Optional parameter not configured : DOXYGEN_INSTALL_PATH

REQUIRED for xdc release build

Example: export DOXYGEN_INSTALL_PATH="~/ti/Doxygen/doxygen/1.5.1-p1/bin"

**************************************************************************

Environment Configuration:

PDK Directory : /home/[user]/new_sdk_release/pdk_[soc]_[version]/packages

CGTOOL INSTALL Directory : /home/[user]/new_sdk_release/ccsv6/tools/compiler/ti-cgt-c6000_[version]

TOOLCHAIN A15 Directory : /home/[user]/new_sdk_release/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A8 Directory : /home/[user]/new_sdk_release/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN A9 Directory : /home/[user]/new_sdk_release/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]

TOOLCHAIN M4 Directory : /home/[user]/new_sdk_release/ccsv6/tools/compiler/ti-cgt-arm_[version]

FPULIB_PATH : /home/[user]/new_sdk_release/ccsv6/tools/compiler/gcc-arm-none-eabi-[version]/lib/gcc/arm-none-eabi/[version]/fpu

CROSS_TOOL_PRFX : arm-none-eabi-

XDC_INSTALL_PATH : /home/[user]/new_sdk_release/xdctools_[version]_core

BIOS_INSTALL_PATH : /home/[user]/new_sdk_release/bios_[version]

IPC_INSTALL_PATH : /home/[user]/new_sdk_release/ipc_[version]

EDMA3LLD_BIOS6_INSTALLDIR : /home/[user]/new_sdk_release/edma3_lld_[version]

NDK_INSTALL_PATH : /home/[user]/new_sdk_release/ndk_[version]

IMGLIB_INSTALL_PATH : /home/[user]/new_sdk_release/imglib_c66x_[version]

UIA_INSTALL_PATH : /home/[user]/new_sdk_release/uia_[version]

PROC_SDK_INSTALL_PATH : /home/[user]/new_sdk_release/processor_sdk_rtos_[soc]_[version]

PROCESSOR SDK BUILD ENVIRONMENT CONFIGURED

*******************************************************************************

The RTOS SDK top level Makefile can now be used to rebuild SDK RTOS components installed in the custom installation path using CCS and toolchains installed in a custom path as well.

10.2.1.2.4. Rebuilding the PDK¶

Installing the PDK in a folder other than the default (C:TI for Windows, /home/[user]/ti for Linux) requires modifications to PDK scripts in order for recompilation and example/test creation to work properly.

10.2.1.2.4.1. CCS in Custom Path and PDK in Default Path¶

The instructions provided in the CCS in Custom Path and SDK RTOS in Default Path section can be used to rebuild components at the PDK level. The only difference is the PDK level setup script should be used instead of the SDK RTOS level setup script. The PDK level setup scripts are found in the following locations on Windows and Linux, respectively:

- Windows - C:\custom\install\path\pdk_[soc]_[version]\packages\pdksetupenv.bat

- Linux - /home/[user]/custom/install/path/pdk_[soc]_[version]/packages/pdksetupenv.sh

10.2.1.2.4.2. CCS in Default Path and PDK in Custom Path¶

The instructions provided in the CCS in Default Path and SDK RTOS in Custom Path section can be used to rebuild components at the PDK level. The only difference is the PDK level setup script should be used instead of the SDK RTOS level setup script. The PDK level setup scripts are found in the following locations on Windows and Linux, respectively:

- Windows - C:\custom\install\path\pdk_[soc]_[version]\packages\pdksetupenv.bat

- Linux - /home/[user]/custom/install/path/pdk_[soc]_[version]/packages/pdksetupenv.sh

10.2.1.2.4.3. CCS and PDK in Custom Path¶

The instructions provided in the CCS and SDK RTOS in Custom Path section can be used to rebuild components at the PDK level. The only difference is the PDK level setup script should be used instead of the SDK RTOS level setup script. The PDK level setup scripts are found in the following locations on Windows and Linux, respectively:

- Windows - C:\custom\install\path\pdk_[soc]_[version]\packages\pdksetupenv.bat

- Linux - /home/[user]/custom/install/path/pdk_[soc]_[version]/packages/pdksetupenv.sh

10.2.1.2.5. Creating PDK Example/Test Projects When CCS is Installed to Custom Path¶

The pdkProjectCreate scripts must be modified in order to build PDK example and test projects only if CCS has been installed to a custom path. The modification is the same for both Windows and Linux. Inside the pdkProjectCreate scripts is a CCS_INSTALL_PATH variable which points to the Code Composer Studio root directory. This variable must be redefined to the new location of the CCS root directory if CCS is installed to a custom path.

- Windows

REM Install Location for CCS

set CCS_INSTALL_PATH="C:\ti\ccsv6"

- Linux

# Install Location for CCS

export CCS_INSTALL_PATH=~/ti/ccsv6

Note

Prior to invoking the pdkProjectCreate script, make sure to start CCS and register the SDK RTOS components installed. Project creation will fail if the RTOS SDK components installed to the custom path have not been registered with CCS. Please see CCS and SDK installed in different directories for instructions on how to register SDK RTOS components installed to a custom path with CCS

10.2.1.3. Prevent BeagleBone board reset on JTAG Connect¶

https://elinux.org/Beagleboard:BeagleBone#Board_Reset_on_JTAG_Connect.28A3.2CA4.2CA5.29

10.2.1.4. Rebuild drivers from PDK directory¶

Refer Rebuilding the PDK for details on rebuilding the PDK components.

10.2.2. Flashing and Boot¶

10.2.2.1. Flash bootable images (C66x, K2H/K2E/K2L only)¶

10.2.2.1.1. Overview¶

The Processor SDK RTOS for C6657, C6678, K2H, K2E, and K2L EVMs includes a script in the directory

[SDK Install Path]/processor_sdk_rtos_<platform>_<version>/bin

named program_evm.js. The purpose of this script is to automatically flash bootable images onto your EVM.

The following sections will describe how to use this script and the default flashable binaries in the Processor SDK RTOS.

10.2.2.1.2. Requirements¶

- A Windows or Linux PC

- Processor SDK RTOS installed on your PC. The version to install must match the SOC you plan to use

- Code Composer Studio installed on your PC

- An USB connection to your EVM emulator

Note

Your board should be set to NO-BOOT mode. Please refer to the boot mode dip switch settings for different boot modes on your EVM Hardware User Guide. See this page for a link to all supported EVM information.

10.2.2.1.3. Directory Structure¶

The files used are in the Processor SDK RTOS directory. Expanded below are the relevant files and directories for flashing the bootable images for C667x, but a similar structure is used for C665x.

├── bin

│ ├── configs

│ │ └── evm6678l

│ │ ├── evm6678l.ccxml

│ │ ├── evm6678le.ccxml

│ │ ├── evm6678le-linuxhost.ccxml

│ │ └── evm6678l-linuxhost.ccxml

│ ├── logs

│ └── program_evm.js

└── prebuilt-images

├── eeprom50.bin

├── eeprom51.bin

├── eepromwriter_evm6678l.out

├── eepromwriter_input50.txt

├── eepromwriter_input51.txt

├── eepromwriter_input.txt

├── nandwriter_evm6678l.out

├── nand_writer_input.txt

├── norwriter_evm6678l.out

└── nor_writer_input.txt

Below is the expanded tree for K2H. Similarly, this also applies to K2E and K2L EVMs.

├── bin

│ ├── configs

│ │ └── evmk2h

│ │ ├── evmk2h.ccxml

│ │ ├── evmk2h-linuxhost.ccxml

│ │ └── program_evm_config

│ ├── logs

│ └── program_evm.js

└── prebuilt-images

├── app

├── config

├── MLO

└── spi_flash_writer.out

10.2.2.1.4. Default Binaries and Setup¶

Processor SDK RTOS provides the basic CCXML files to connect to your SOC. There is a separate CCXML file for each SOC, emulator, and host OS combination. These CCXML files are located in:

[SDK Install Path]/processor_sdk_rtos_<platform>_<version>/bin/config/<SOC>

Users can choose to use their own CCXML file by setting the environment variable, PROGRAM_EVM_TARGET_CONFIG_FILE, to point to their CCXML file in their terminal or command prompt.

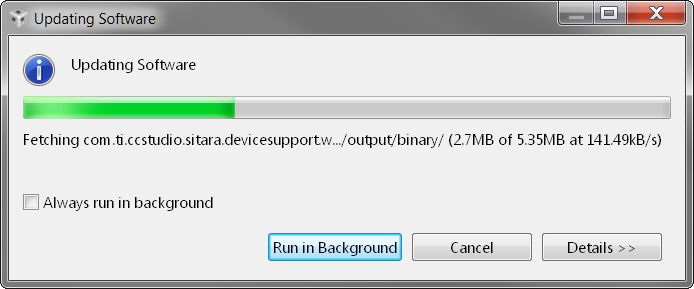

You can create your own CCXML file by opening CCSv6 –> View –> Target Configurations, and right-clicking on the Target Configuration pane to select New Target Configuration. After selecting your SOC and emulator, remember to set the appropriate GEL file in the advance options for Core 0. The GEL file is used to do basic SOC initialization upon connecting to the core.

Processor SDK RTOS also provides the basic binaries needed to perform flashing. These are separated into two categories - flashwriters and flash images.

Flashwriters

- [C66x] eepromwriter_<SOC>.out - writes content to your EVM EEPROM flash memory

- [C66x] norwriter_<SOC>.out - writes content to your EVM NOR flash memory

- [C66x] nandwriter_<SOC>.out - writes content to your EVM NAND flash memory

- [K2H/E/L] spi_flash_writer.out - writes multiple images to your NOR flash memory

Flash images

- [C66x] eeprom50.bin - eeprom binary for address 0x50. The default for C66x is the POST application.

- [C66x] eeprom51.bin - eeprom binary for address 0x51. The default for C66x is the Intermediate Boot Loader (IBL).

- [C66x] nor.bin - nor binary to be used for NOR boot. May not be provided for every EVM or release version.

- [C66x] nand.bin - nand binary to be used for NAND boot. May not be provided for every EVM or release version.

- [K2H/K2E/K2L] app - NOR binary to be booted by Secondary Bootloader. The default for Keystone 2 is the POST application

- [K2H/K2E/K2L] MLO - Secondary Bootloader. The default flash location is in SPI NOR flash memory at offset 0.

10.2.2.1.5. Usage¶

For Windows users:

> cd [SDK Install Path]\processor_sdk_rtos_<platform>_<version>\bin

> set DSS_SCRIPT_DIR=[CCS Install Path]\ccsv6\ccs_base\scripting\bin

> %DSS_SCRIPT_DIR%\dss.bat program_evm.js [tmdx|tmds]evm(6678|6657|k2h|k2e|k2l)[l|le|ls][-le|-be]

For Linux users:

> cd [SDK Install Path]/processor_sdk_rtos_<platform>_<version>/bin

> export DSS_SCRIPT_DIR=[CCS Install Path]/ccsv6/ccs_base/scripting/bin

> $DSS_SCRIPT_DIR/dss.sh program_evm.js [tmdx|tmds]evm(6678|6657|k2h|k2e|k2l)[l|le|ls][-le|-be]

The last argument depends on the SOC that you have, concatenated with the options to select emulator and endianness:

- l: EVM uses XDS100 on-board Emulator

- le: EVM uses 560 Mezzanine Emulator daughter card

- ls: EVM uses XDS200 Emulator card

- -le: Little Endian

- -be: Big Endian

Note

- By default, the images provided are little endian.

- Also by default, Keystone 2 EVMs are expected to only use the XDS2xx Emulator. You do not have to supply the emulator in the parameter for K2H/K2E/K2L.

Some examples are:

TMDXEVM6678LE little endian

> $DSS_SCRIPT_DIR/dss.sh program_evm.js tmdxevm6678le-le

TMDSEVM6657LS little endian

> $DSS_SCRIPT_DIR/dss.sh program_evm.js tmdxevm6657ls-le

EVMK2H little endian

> $DSS_SCRIPT_DIR/dss.sh program_evm.js tmdsevmk2h

EVMK2E little endian

> $DSS_SCRIPT_DIR/dss.sh program_evm.js tmdsevmk2e

10.2.2.1.6. Sample Output¶

C:\ti\processor_sdk_rtos_c665x_2_00_01_07\bin>%DSS_SCRIPT_DIR%\dss.bat program_evm.js tmdxevm6657ls-le

board: evm6657l

endian: Little

emulation: XDS200 emulator

binaries: ../prebuilt-images/

ccxml: C:\ti\processor_sdk_rtos_c665x_2_00_01_07\bin/configs/evm6657l/evm6657ls.ccxml

C66xx_0: GEL Output:

Connecting Target...

C66xx_0: GEL Output: DSP core #0

C66xx_0: GEL Output: C6657L GEL file Ver is 1.006

C66xx_0: GEL Output: Global Default Setup...

C66xx_0: GEL Output: Setup Cache...

C66xx_0: GEL Output: L1P = 32K

C66xx_0: GEL Output: L1D = 32K

C66xx_0: GEL Output: L2 = ALL SRAM

C66xx_0: GEL Output: Setup Cache... Done.

C66xx_0: GEL Output: Main PLL (PLL1) Setup ...

C66xx_0: GEL Output: PLL in Bypass ...

C66xx_0: GEL Output: PLL1 Setup for DSP @ 1000.0 MHz.

C66xx_0: GEL Output: SYSCLK2 = 333.3333 MHz, SYSCLK5 = 200.0 MHz.

C66xx_0: GEL Output: SYSCLK8 = 15.625 MHz.

C66xx_0: GEL Output: PLL1 Setup... Done.

C66xx_0: GEL Output: Power on all PSC modules and DSP domains...

C66xx_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=12, md=4!

C66xx_0: GEL Output: Power on all PSC modules and DSP domains... Done.

C66xx_0: GEL Output: DDR3 PLL (PLL2) Setup ...

C66xx_0: GEL Output: DDR3 PLL Setup... Done.

C66xx_0: GEL Output: DDR3 Init begin (1333 auto)

C66xx_0: GEL Output: XMC Setup ... Done

C66xx_0: GEL Output: IFRDY bit is SET: DDR3 Interface Ready

C66xx_0: GEL Output:

DDR3 initialization is complete.

C66xx_0: GEL Output: DDR3 Init done

C66xx_0: GEL Output: DDR3 memory test... Started

C66xx_0: GEL Output: DDR3 memory test... Passed

C66xx_0: GEL Output: PLL and DDR3 Initialization completed(0) ...

C66xx_0: GEL Output: configSGMIISerdes Setup... Begin

C66xx_0: GEL Output: SGMII SERDES has been configured.

C66xx_0: GEL Output: Enabling EDC ...

C66xx_0: GEL Output: L1P error detection logic is enabled.

C66xx_0: GEL Output: L2 error detection/correction logic is enabled.

C66xx_0: GEL Output: MSMC error detection/correction logic is enabled.

C66xx_0: GEL Output: Enabling EDC ...Done

C66xx_0: GEL Output: Global Default Setup... Done.

Start writing eeprom50

Writer:../prebuilt-images/eepromwriter_evm6657l.out

Image:../prebuilt-images/eeprom50.bin

C66xx_0: GEL Output: Invalidate All Cache...

C66xx_0: GEL Output: Invalidate All Cache... Done.

C66xx_0: GEL Output: GEL Reset...

C66xx_0: GEL Output: GEL Reset... Done.

C66xx_0: GEL Output: Disable all EDMA3 interrupts and events.

EEPROM Writer Utility Version 01.00.00.05

Writing 57432 bytes from DSP memory address 0x0c000000 to EEPROM bus address 0x0050 starting from device address 0x0000

...

Reading 57432 bytes from EEPROM bus address 0x0050 to DSP memory address 0x0c010000 starting from device address 0x0000

...

Verifying data read ...

EEPROM programming completed successfully

Start writing eeprom51

Writer:../prebuilt-images/eepromwriter_evm6657l.out

Image:../prebuilt-images/eeprom51.bin

C66xx_0: GEL Output: Invalidate All Cache...

C66xx_0: GEL Output: Invalidate All Cache... Done.

C66xx_0: GEL Output: GEL Reset...

C66xx_0: GEL Output: GEL Reset... Done.

C66xx_0: GEL Output: Disable all EDMA3 interrupts and events.

EEPROM Writer Utility Version 01.00.00.05

Writing 47888 bytes from DSP memory address 0x0c000000 to EEPROM bus address 0x0051 starting from device address 0x0000

...

Reading 47888 bytes from EEPROM bus address 0x0051 to DSP memory address 0x0c010000 starting from device address 0x0000

...

Verifying data read ...

EEPROM programming completed successfully

Writer:../prebuilt-images/nandwriter_evm6657l.out

NAND:../prebuilt-images/nand.bin

Required NAND files does not exist in ../prebuilt-images/

Writer:../prebuilt-images/norwriter_evm6657l.out

NOR:../prebuilt-images/nor.bin

Required NOR files does not exist in ../prebuilt-images/

In the above example, nothing was flashed to NAND or NOR since there were no nand.bin or nor.bin binaries to flash.

10.2.3. Porting¶

10.2.3.1. Adding Custom Board_Library Target to Processor SDK RTOS makefiles¶

10.2.3.1.1. Introduction¶

The following article describes how a custom Board can be added to the Processor SDK RTOS. The scope of this article is to only describe how to modify the build files in the PDK to add build steps for your custom board library. The article does not describe modification of source files to reflect changes to clocking, DDR and pinmux setup for the custom board.

The instructions provided in this article uses example of AM572x custom board but the instructions apply to all the processors supported in Processor SDK RTOS. Note that the instructions on this wiki were created using Processor SDK RTOS v3.2 and PDK_AM57xx_1_0_5 and are subject to change. Also the wiki was created specifically for the newer board variants like evmAM572x, idkAM572x and evmK2G. For AM335x and AM437x variant board library has several dependencies on legacy starterware package, hence additional steps are required and not covered in the wiki.

10.2.3.1.2. Instructions to add custom Board to the PDK build¶

Step 1: Creating new directory for custom board library

In pdk_am57xx_x_x_x/packages/ti/board/src, Create new directory myCustomBoard and copy files from existing board library package. We recommend that you copy files from the board which closely matches your custom board design. In this case, we assume that the custom board is based on the design of evmAM572x so we copy over the files from that directory into myCustomBoard folder.

Step 2: Updating names and makefile inside the customBoard package

In pdk_am57xx_x_x_x/packages/ti/board/src/myCustomBoard, Rename file src_files_evmAM572x.mk to src_files_myCustomBoard.mk. This file will need a bit of work depending on what elements of board you need for your platform. We have left all the files evmAM572x_*.c but you can modify as needed.

Step 3: Adding MACRO based inclusion of updated board_cfg.h corresponding to custom Board

In packages/ti/board/board_cfg.h, add the lines pointing to board_cfg.h file in your customBoard package so that updated peripheral instances and board specific defines can be picked up

#if defined (myCustomBoard)

#include <ti/board/src/myCustomBoard/include/board_cfg.h>

#endif

Step 4: Update top level board package makefile to include build for customBoard Library The makefile is used to include all relevant make files for including Low level driver(LLD), source files relevant to board and the common board.c file

- In packages/ti/board/build/makefile.mk, add board.c to the customBoard build :

ifeq ($(BOARD),$(filter $(BOARD),evmAM335x icev2AM335x skAM335x bbbAM335x evmAM437x idkAM437x skAM437x myCustomBoard evmAM572x idkAM571x idkAM572x evmK2H evmK2K evmK2E evmK2L evmK2G iceK2G evmC6678 evmC6657))

# Common source files across all platforms and cores

SRCS_COMMON += board.c

endif

- Add board library source files and LLD files to the customBoard build

In packages/ti/board/build/makefile.mk, change

ifeq ($(BOARD),$(filter $(BOARD), evmAM572x idkAM571x idkAM572x))

include $(PDK_BOARD_COMP_PATH)/src/$(BOARD)/src_files_$(BOARD).mk

include $(PDK_BOARD_COMP_PATH)/src/src_files_lld.mk

CFLAGS_LOCAL_$(BOARD) += -D$(BOARD)

endif

to

ifeq ($(BOARD),$(filter $(BOARD), myCustomBoard evmAM572x idkAM571x idkAM572x))

include $(PDK_BOARD_COMP_PATH)/src/$(BOARD)/src_files_$(BOARD).mk

include $(PDK_BOARD_COMP_PATH)/src/src_files_lld.mk

CFLAGS_LOCAL_$(BOARD) += -D$(BOARD)

endif

Step 5: Update Global makerules

build_config.mk defines the global CFLAGS used to compile different PDK components. Add the following line in the BOARD Specific configurations.

CFLAGS_GLOBAL_customAM572x = -DSOC_AM572x -DevmAM572x

The SOC_AM572x macro ensures that the CSL aplicable to this SOC will be included in the build and evmAM572x define will ensure all evmAM572x specific includes that apply to the customAM572x are part of the build.

Optional step to update RTSC platform definition If you have a custom RTSC platform definition for your custom board that updates the memory and platform configuration using RTSC Tool then you need to update the platform.mk file that associates the RTSC platfom with the corresponding board library

In packages/ti/buildmakerules/platform.mk, add the following lines:

ifeq ($(BOARD),$(filter $(BOARD), evmAM572x))

PLATFORM_XDC = "ti.platforms.evmAM572X"

endif

ifeq ($(BOARD),$(filter $(BOARD), myCustomBoard))

PLATFORM_XDC = "evmAM572XCustom"

endif

Note

The SYSBIOS platforms follow the convention to consolidate all platform definitions under SYSBIOS_INSTALL_PATH/packages/ti/platforms/* hence the convention ti.platorms.<platformName> but for custom platform, users are not required to follow this convention.

Step 6: Update source files corresponding to drivers used in board library. src_files_lld.mk file adds source files corresponding to LLD drivers used in the board library. Usually most boards utilitize control driver like I2C (for programming the PMIC or reading EEPROM), UART drivers (for IO) and boot media drivers like (SPI/QSPI, MMC or NAND). In the example below, we assume that the custom Board library has dependency on I2C, SPI and UART LLD drivers. Since the LLD drivers will be linked to the application along with board library, board library only needs <driver>_soc.c corresponding to SOC used on the custom Board.

In packages/ti/board/src/src_files_lld.mk, add the following lines:

ifeq ($(BOARD),$(filter $(BOARD), myCustomBoard))

SRCDIR += $(PDK_INSTALL_PATH)/ti/drv/i2c/soc/am572x \

$(PDK_INSTALL_PATH)/ti/drv/uart/soc/am572x \

$(PDK_INSTALL_PATH)/ti/drv/spi/soc/am572x

INCDIR += $(PDK_INSTALL_PATH)/ti/drv/i2c/soc/am572x \

$(PDK_INSTALL_PATH)/ti/drv/uart/soc/am572x \

$(PDK_INSTALL_PATH)/ti/drv/spi/soc/am572x

# Common source files across all platforms and cores

SRCS_COMMON += I2C_soc.c UART_soc.c SPI_soc.c

endif

Note

For all LLD drivers linked to the board library you need to include corresponding <drv>_soc.c file. For example if you include GPIO driver for setting board mux then GPIO_soc.c needs to be added to LLD source files.

Step 7: Add custom Board to BOARDLIST and update CORELIST

In packages/ti/board/board_component.mk, modify the build to add your custom board and specify the cores for which you want to build the board library. Example to build board library for only A15 and C66x cores, limit the build by specify only a15_0 and C66x in the CORELIST

board_lib_BOARDLIST = myCustomBoard evmAM335x icev2AM335x skAM335x bbbAM335x evmAM437x idkAM437x skAM437x evmAM572x idkAM571x idkAM572x evmK2H evmK2K evmK2E evmK2L evmK2G iceK2G \

#board_lib_am572x_CORELIST = c66x a15_0 ipu1_0

board_lib_am572x_CORELIST = a15_0 c66x

Step 8: Update .bld files for XDCTOOL based build steps.

Make corresponding changes in packages/ti/board/config.bld, by adding the following lines:

var myCustomBoard = {

name: "myCustomBoard",

ccOpts: "-DevmAM572x -DSOC_AM572x",

targets: [C66LE,A15LE ]

lldFiles: [ "$(PDK_INSTALL_PATH)/ti/drv/i2c/soc/am572x/I2C_soc.c",

"$(PDK_INSTALL_PATH)/ti/drv/uart/soc/am572x/UART_soc.c",

"$(PDK_INSTALL_PATH)/ti/drv/spi/soc/am572x/SPI_soc.c"]

}

var boards = [ evmAM335x, icev2AM335x, skAM335x, bbbAM335x, evmAM437x, idkAM437x, skAM437x, myCustomBoard, evmAM572x, idkAM571x, idkAM572x, evmK2H, evmK2K, evmK2E, evmK2L, evmK2G, evmC6678, evmC6657 ];

Also, in packages/ti/board/package.bld, I added the following line:

Pkg.otherFiles[Pkg.otherFiles.length++] = "src/myCustomBoard/src_files_myCustomBoard.mk";

Step 9: Setup Top level PDK build files to add the Custom board to setup environment.

Final setup involves updating the top level setup file for PDK package to update to setup the build environment to include the custom Board in setup. This can be done by commenting out the top line and adding in the bottom line in pdksetupenv.bat:

@REM if not defined LIMIT_BOARDS set LIMIT_BOARDS=evmAM572x idkAM571x idkAM572x

if not defined LIMIT_BOARDS set LIMIT_BOARDS=myCustomBoard

Alternative: Invoke the build using command line options to limit the build to specific board, specific SOC and specific CORE. For example, if you want to build the A15 version of board library for AM572x EVM, you can invoke the build using:

gmake board_lib LIMIT_SOCS=am572x LIMIT_BOARDS=customAM572x LIMIT_CORES=a15_0

Step 10 : Building the custom board with the updated settings

To build package change directory to <SDK_INSTALL_PATH>/pdk_am57xx_x_x_x/packages, first run pdksetupenv.bat

To make just the board library: gmake board_lib

10.2.3.1.3. Example custom Board library for reference¶

The package provided below provides updated files for building customBoard “customAM572x” following all steps described above. Please compare the files to the evmAM57xx board library files to follow the steps to add your own board library.

File:Pdk packages ti board customAM572x.zip

Note

Due to software distribution policy on the wiki, we have removed the file linked here. Users can refer to the discussion and zipped package linked from E2E post provided below:

10.2.3.1.4. Additional steps for AM335x/AM437x users¶

Note

Currently the AM335x and AM437x board libraries re-use the board support that was used in legacy starterware software. AM335x and AM437x users will need to additionally modify build files in starterware to build their custom board library. Additional steps required for AM335x/AM437x will be added to this article soon in this section

10.2.3.2. Processor SDK RTOS Porting Guide for AM571x/AM570x Speed Grades¶

10.2.3.2.1. Description¶

The AM57x Family of Processors includes a wide range of operating performance to meet the needs of a number of broad applications. Among these options are a variety of speed grades to meet different performance points. These devices have a number of specialized cores to provide applications specific computation capabilities. These cores can be run at different speeds to fine tune the processor to the needs of the application, power budget, thermal characteristics, etc.

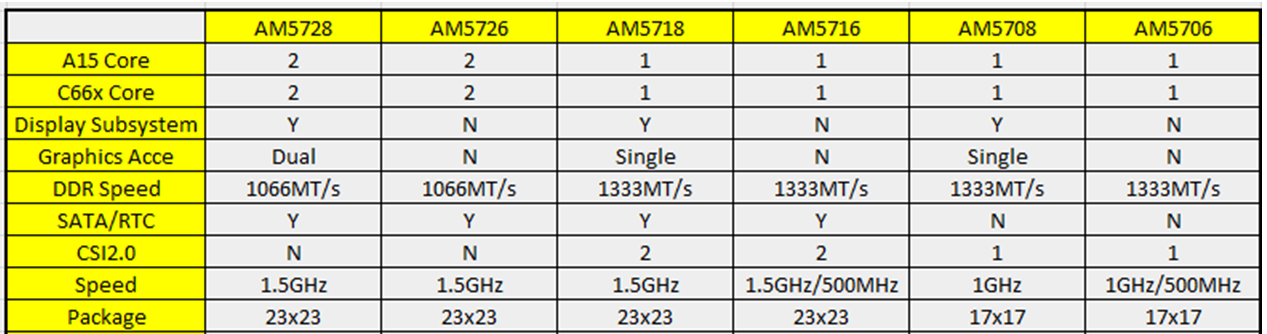

The Processor SDK for RTOS is a software development package provided to speed development by providing a software reference. This package now includes support for then entire AM57x family of processors which can be broken down into the AM572x, AM571x, and AM570x sets of devices or sub-familes. Most of the devices in this family are supported by the Processor SDK for RTOS right out of the box. This support is tested and validated on TI designed EVMs. These EVMs use the highest performance devices in the family in order to allow users to evaluate the entire spectrum of performance.

The AM571X and AM570x supports several lower power speed grades. If one of these devices is being used on the custom board, the GEL file and the board library needs to be changed to account for this difference. If this change is not made, the device could be running out of specification. These changes may reach across other cores and clocks on the device as well, depending on what speeds they need to operate at. This document is not an exhaustive list of all the changes needed for a proper board port as it focused on the changes needed to enable different speed grades.

10.2.3.2.2. Comparison of AM572x, AM571x and AM570x devices¶

Quick Feature Set comparison between devices in Sitara AM57xx family :

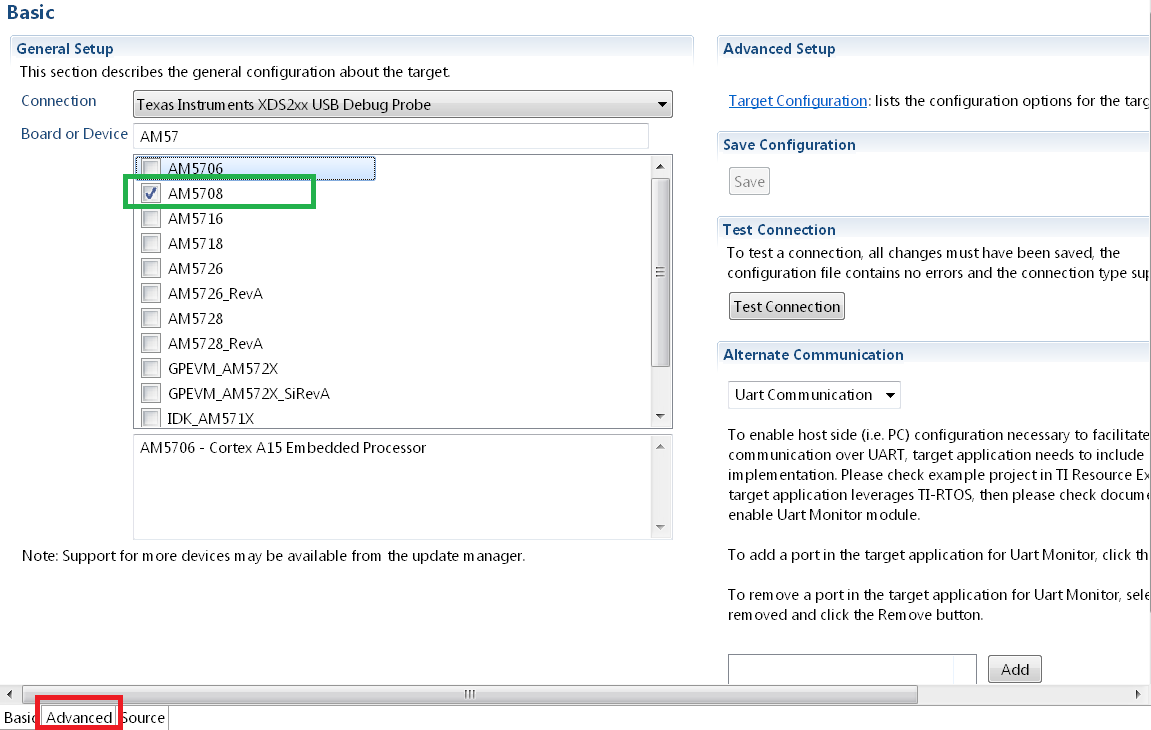

10.2.3.2.3. Code Composer Studio (CCS) and Emulation support¶

TI Supports following evaluation platform for AM57xx class of devices:

When developer selects any of the above platforms in Code composer Studio, the target configuration automatically brings in the required initialization files and GEL files to configure the clocks, slave cores, external memory.

If you are using a custom platform or AM5708 device that is not available on a TI Evaluation platform, you can follow the steps provided below to connect to the SOC by reusing the GEL files that are provided for TI evaluation platforms. For example, here we demonstrate how you can create a target configuration for AM570x and connect to the device if your board design is based of one of TI evalauation platforms listed below. The assumption here is that the custom board is based off AM571X IDK platform

Note

Support for AM5708 was added to Sitara Chip Support Package 1.3.4 in Code composer Studio. If you don`t see the device definition in CCS, then you can update the Sitara Chip Support package by going to Help->Check Updates

Step 1: Select the AM570x part number that is populated on your custom platform:

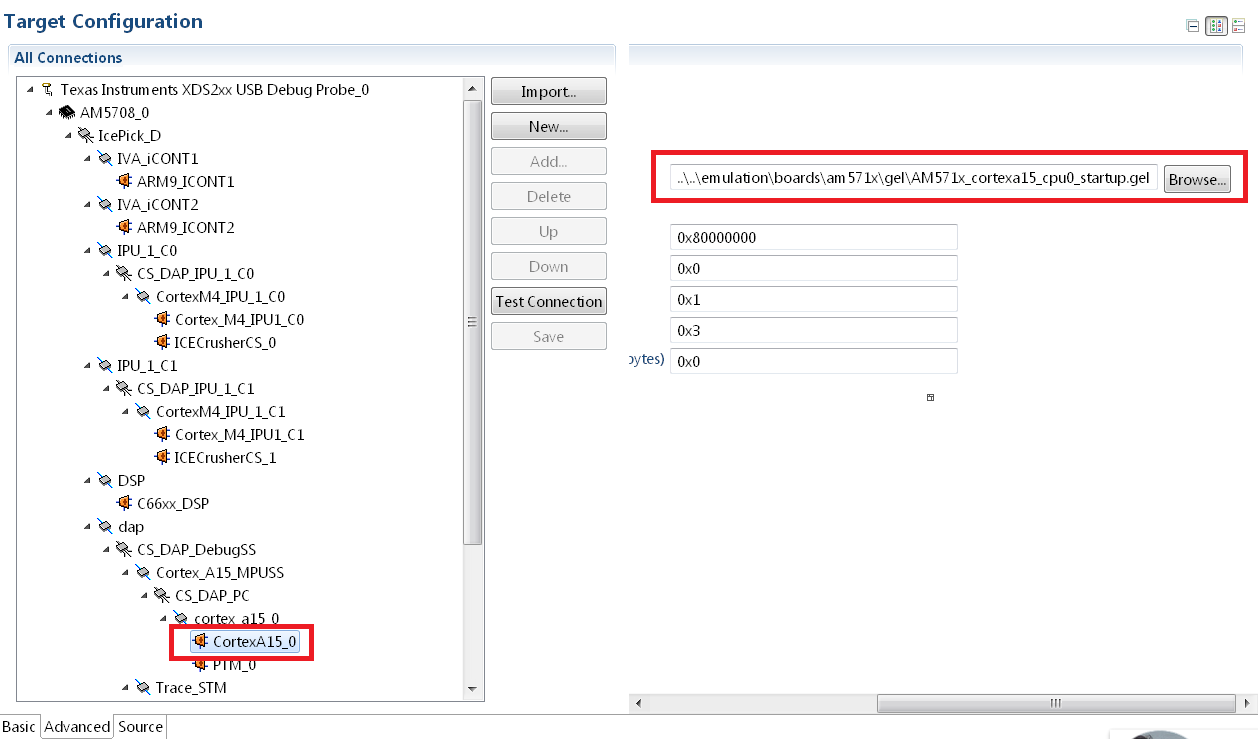

Step 2: Setup the GEL files for the SOC Go to the Advanced Tab as shown in the previous screenshot and update startup GEL file in the A15 Core as shown in the screenshot below

10.2.3.2.4. Board Library Changes to Consider for Using Processor SDK RTOS¶

10.2.3.2.4.1. Clock and PRCM Updates to consider¶

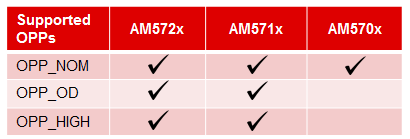

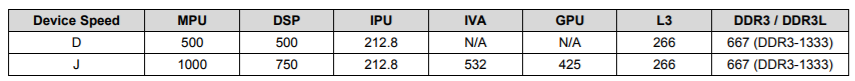

The board library provides setting for OPP_NOM, OPP_OD and OPP_HIGH in the PLL settings using 20 MHz input clock that has been used on the AM572x GP EVM as well as the AM571x IDK platform. This allows customers to setup the MPU to 1.5, 1.176 and 1GHz. For AM570x devices, we support the “J” and the “D” variant which support the following max speeds on the DPLLs:

When using the “J” speed grade, ensure that the DPLLs in the board set the DPLL to OPP_NOM and not for OPP_OD or OPP_HIGH.

To do this, you can invoke the Board_Init from your application using either

Board_initCfg boardCfg;

boardCfg = BOARD_INIT_PLL_OPP_NOM;

boardCfg |= BOARD_INIT_UNLOCK_MMR |

BOARD_INIT_MODULE_CLOCK |

BOARD_INIT_PINMUX_CONFIG |

BOARD_INIT_DDR |

BOARD_INIT_UART_STDIO |

BOARD_INIT_WATCHDOG_DISABLE;

/* Board Library Init. */

Board_init(boardCfg);

Note

When bootloading direct from flash media, this change may also be required in the SBL code

When using “D” rated parts that run at 500 MHz, in addition to the above configuration, you will also need to modify OPP_NOM settings in the board library by updating the DPLL setting for MPU and DSP in the file <BoardName>_pll.c as shown below:

Step1 : Update MPU, DSP, IVA and GPU DPLL setting

- MPU DPLL Changes:

/* Default to OPP_NOM */

/* 500MHz at 20MHz sys_clk */

mpuPllcParam.mult = 250U;

mpuPllcParam.div = 9U;

mpuPllcParam.dccEnable = 0U;

mpuPllcParam.divM2 = 1U;

- DSP DPLL Changes:

/* 500MHz at 20MHz sys_clk */

dspPllcParam.mult = 130U;

dspPllcParam.div = 3U;

dspPllcParam.divM2 = 1U;

dspPllcParam.divM3 = 3U;

- Remove IVA and GPU PLL settings

Since IVA and GPU modules are not available on the device, we recommend removing the ivaPLL and gpuPLL settings in board.

/* Default to OPP_NOM */

/* 388.3MHz at 20MHz sys_clk */

- ivaPllcParam.mult = 233U;

- ivaPllcParam.div = 3U;

- ivaPllcParam.divM2 = 3U;

/* Default to OPP_NOM */

/* 425MHz at 20MHz sys_clk */

- gpuPllcParam.mult = 170U;

- gpuPllcParam.div = 3U;

- gpuPllcParam.divM2 = 2U;

Step 2 : Disable clocks configuration and wakeup for IVA in PRCM

- Remove IVA wakeup and Module configuration

The following updates need to be made in the file <BoardName>_clock.c to remove IVA wakeup and clock configuration

- CSL_FINST(ivaCmReg->CM_IVA_CLKSTCTRL_REG,

- IVA_CM_CORE_CM_IVA_CLKSTCTRL_REG_CLKTRCTRL, SW_WKUP);

/* PRCM Specialized module mode setting functions */

- CSL_FINST(ivaCmReg->CM_IVA_SL2_CLKCTRL_REG,

- IVA_CM_CORE_CM_IVA_SL2_CLKCTRL_REG_MODULEMODE, AUTO);

- while(CSL_IVA_CM_CORE_CM_IVA_SL2_CLKCTRL_REG_IDLEST_DISABLE ==

- CSL_FEXT(ivaCmReg->CM_IVA_SL2_CLKCTRL_REG,

- IVA_CM_CORE_CM_IVA_SL2_CLKCTRL_REG_IDLEST));

- CSL_FINST(ivaCmReg->CM_IVA_IVA_CLKCTRL_REG,

- IVA_CM_CORE_CM_IVA_IVA_CLKCTRL_REG_MODULEMODE, AUTO);

- while(CSL_IVA_CM_CORE_CM_IVA_IVA_CLKCTRL_REG_IDLEST_DISABLE ==

- CSL_FEXT(ivaCmReg->CM_IVA_IVA_CLKCTRL_REG,

- IVA_CM_CORE_CM_IVA_IVA_CLKCTRL_REG_IDLEST));

10.2.3.2.5. Configure DDR Interfaces¶

An important one to consider is the speed of the DDR memory. The clock for the DDR is selected using the same dplls structure. Some higher speed grade parts support a 667 MHz DDR clock, but some of the lower speed grade parts only support a 533 MHz DDR3 clock. Make sure to choose the appropriate DDR clock for the device on the custom board.

Over in the board/src/<BoardName>/<BoardName_ddr>.c file, make sure that the EMIF is being configured correctly for the appropriate speed, and that the appropriate number of EMIFs is being selected to match the part being used. AM572x part has 2 DDR interfaces running at 533 MHz and the AM571x (and AM570x) only have one running at 667 MHz. This code can be kept or removed by the board port. As changes are made, the code must make sure to configure the new board correctly, with the appropriate number of DDR interfaces and speed configuration.

For AM571x and AM570x, make sure to use the code for the AM571x IDK in board/src/<BoardName>/<BoardName_ddr>.c to select 1 EMIF:

/* MA_LISA_MAP_i */

hMampuLsm->MAP_0 = 0x80600100U;

/* DMM_LISA_MAP_i */

hDmmCfg->LISA_MAP[0U] = 0x80600100U;

For AM572x, this is mapped as following

/* MA_LISA_MAP_i */

hMampuLsm->MAP_0 = 0x80740300;

hMampuLsm->MAP_1 = 0x80740300;

/* DMM_LISA_MAP_i */

hDmmCfg->LISA_MAP[0U] = 0x80740300;

hDmmCfg->LISA_MAP[1U] = 0x80740300;

Note

Processor SDK RTOS provides am570x_ddr.c file in the idkAM571x board library for reference for configuring DDR on AM570x parts

10.2.3.2.6. Pinmux Changes to Consider¶

- For part number where the Display subsystem or SATA is not available, the pins can be configured to any other pin functionality that may be required in the system. If you don`t need to use these pins, we recommend that you leave these pins in default MUXMODE and terminate the pinmux as recommended in the Schematics Checklist.

- There is no pinmux setting for CSI2 module so you can leave the MUXMODE=0 on those pins if there is no instance of the peripheral

Note

Processor SDK RTOS provides board/src/idkAM571x/include/am570x_pinmux.h file in the idkAM571x board library for reference for configuring pinmux on AM570x based hardware platform

10.2.3.2.7. Driver SOC Module clock changes¶

Some control drivers use default Module input clock frequency settings in <module>_soc.c file that gets used by the Low level drivers to configure the peripheral clocks. The default module input clock frequency is set to the OPP_NOM values that are available on the superset variant of the device so if you are using lower speed grades. Ensure you change the default to match the module clock on the 500 MHz settings or you can use the following sequence to update the settings. Code below describes how the SPI driver module input clock frequency can be modified

SPI_v1_HWAttrs spi_cfg;

/* Get the default SPI init configurations */

SPI_socGetInitCfg(TEST_SPI_PORT, &spi_cfg);

/* Modify the default SPI configurations if necessary */

spi_cfg.inputClkFreq = 24000000;

/* Set the default SPI init configurations */

SPI_socSetInitCfg(TEST_SPI_PORT, &spi_cfg);

10.2.3.2.9. Support¶

For any questions related Usage of AM572x, AM571x and AM570x devices, please post your question on TI E2E Forums

10.2.4. System Integration¶

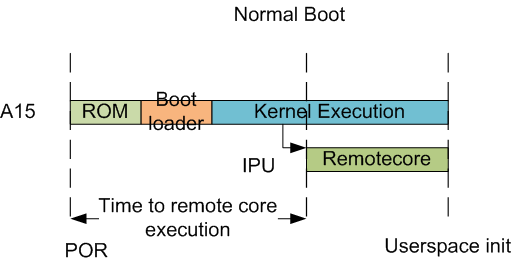

10.2.4.1. Create DSP and IPU firmware using PDK drivers and IPC to load from ARM Linux on AM57xx devices¶

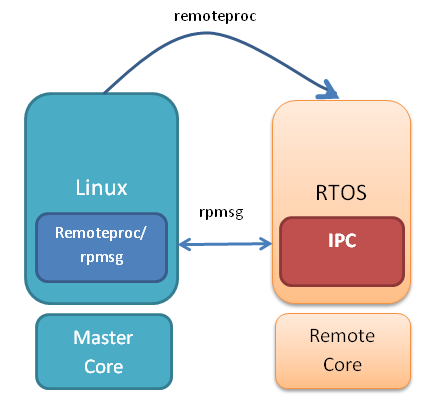

10.2.4.1.1. Introduction¶

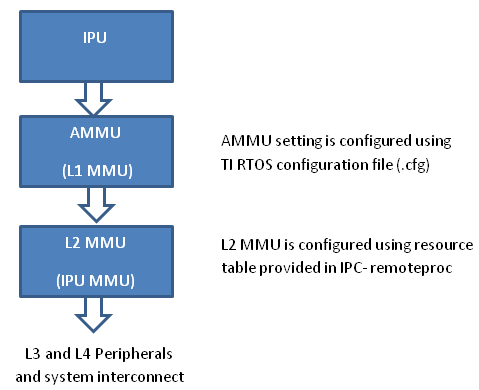

This article is geared toward AM57xx users that are running Linux on the Cortex A15. The goal is to help users understand how to gain entitlement to the DSP (c66x) and IPU (Cortex M4) subsystems of the AM57xx.