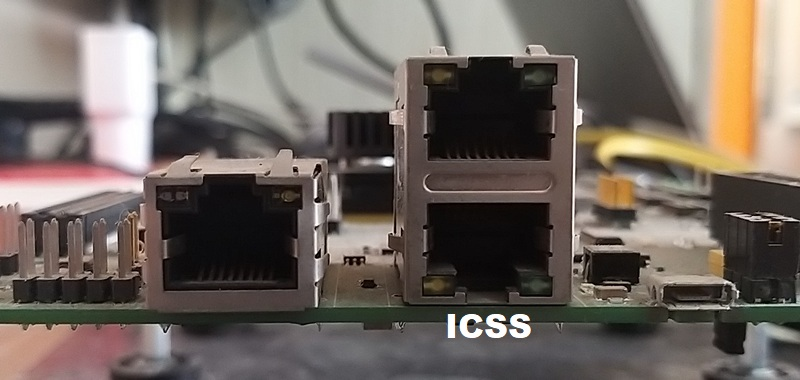

This layer 2 icssg example demonstrates the usage of Enet with ICSSG peripheral operation.

==========================

MULTIPORT TEST

==========================

Init all peripheral clocks

----------------------------------------------

Enabling clocks!

Open all peripherals

----------------------------------------------

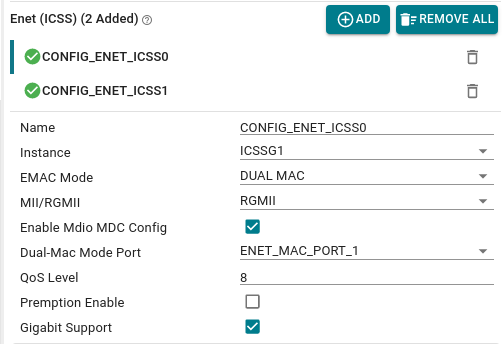

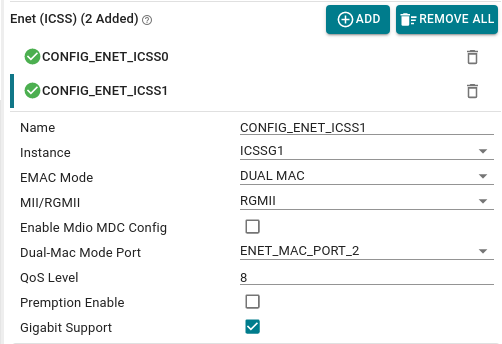

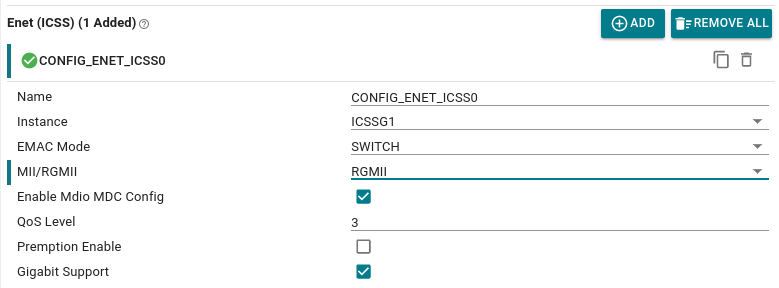

Init configs EnetType:2, InstId :1

----------------------------------------------

icssg1: Open port 1

icssg1: Open port 2

EnetPhy_bindDriver:

PHY 3 is alive

PHY 15 is alive

icssg1: Register async IOCTL callback

icssg1: Register TX timestamp callback

Attach core id 1 on all peripherals

----------------------------------------------

icssg1: Attach core

Create RX tasks

----------------------------------------------

icssg1: Create RX task

icssg1: Waiting for link up...

Enet Multiport Menu:

'T' - Enable timestamp prints

't' - Disable timestamp prints

's' - Print statistics

'r' - Reset statistics

'm' - Show allocated MAC addresses

'd' - Enable dscp based priority mapping

'x' - Stop the test

EnetPhy_bindDriver:

Icssg_handleLinkUp:

Icssg_handleLinkUp:

icssg1: Port 1 link is up

icssg1: Set port state to 'Forward'

icssg1: Async IOCTL completed

icssg1: Async IOCTL completed

icssg1: Port 2 link is up

icssg1: Set port state to 'Forward'

icssg1: Async IOCTL completed

icssg1: Async IOCTL completed

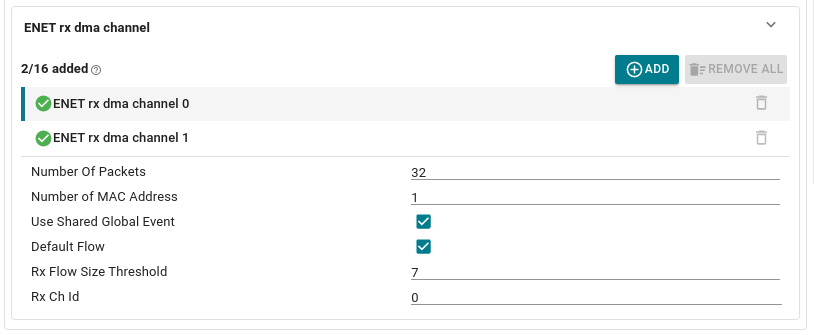

icssg1: Open DMA

initQs() txFreePktInfoQ initialized with 8 pkts

icssg1: Set MAC addr: 70:ff:76:1d:92:c1

icssg1: MAC port addr: 70:ff:76:1d:92:c1

Invalid option, try again...

Enet Multiport Menu:

'T' - Enable timestamp prints

't' - Disable timestamp prints

's' - Print statistics

'r' - Reset statistics

'm' - Show allocated MAC addresses

'd' - Enable dscp based priority mapping

'x' - Stop the test

s

Print statistics

----------------------------------------------

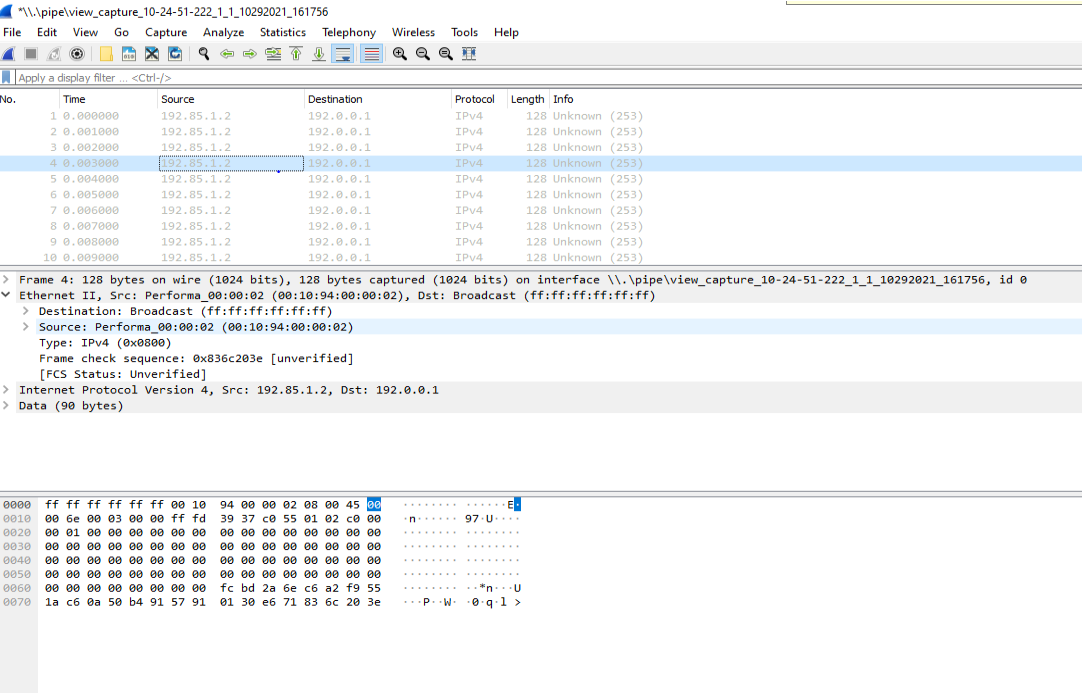

icssg1 - PA statistics

--------------------------------

port1Q0Overflow = 234

icssg1 - Port 1 statistics

--------------------------------

rxGoodFrames = 25337838

rxClass8 = 25337838

rxClass9 = 25337838

rxBucket2SizedFrame = 65535

rxTotalByte = 3243243264

rxTxTotalByte = 4294967295

txGoodFrame = 25337838

txBucket3SizedFrame = 65535

txTotalByte = 3445945968

icssg1 - Port 2 statistics

--------------------------------

rxGoodFrames = 25337838

rxClass8 = 25337838

rxClass9 = 25337838

rxBucket2SizedFrame = 65535

rxTotalByte = 3243243264

rxTxTotalByte = 4294967295

txGoodFrame = 25337604

txBucket3SizedFrame = 65535

txTotalByte = 3445914144