This ethernet TSN example illustrates the usage of gPTP IEEE 802.1AS stack with CPSW peripheral, in gPTP End-Point time_receiver mode (i.e. slave mode). However, the application used here supports all the below modes:

In this example, connected Host PC is configured to force gPTP grand master role, so that the DUT becomes time_receiver (i.e. gPTP slave) mode. Yang based configuration is also supported. Currently File System is not supported, will be added in future releases.

PPS output is a square wave signal generated by the device. It is used for comparison between the TT (master) and TR( slave) nodes when they are time synchronized. On the device, PPS is generated on the SYNC_OUT signal pin from CPTS (Common Platform Time Synchronization) of CPSW.

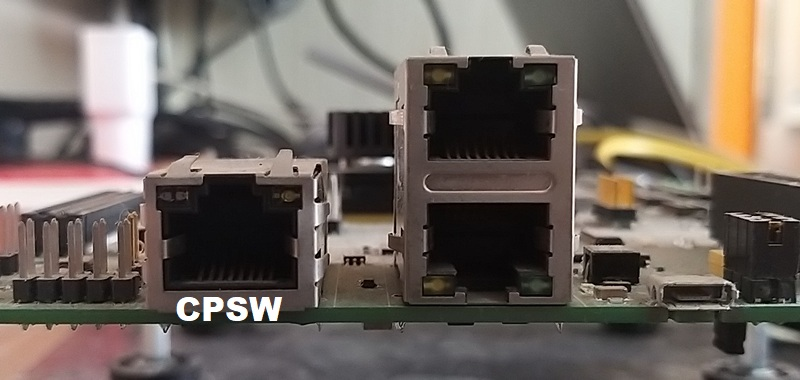

EVM and PC has to connected directly as shown below using CAT6 or CAT5 cable. If there is ethernet switch placed in between, make sure the switch is gPTP capable.

PORT1 instead of PORT0 on EVM can be used as well.

==========================

gPTP App

==========================

Enabling clocks!

sitara-cpsw: Create RX task for regular traffic

start to open driver.

EnetAppUtils_reduceCoreMacAllocation: Reduced Mac Address Allocation for CoreId:1 From 4 To 2

Init all configs

----------------------------------------------

sitara-cpsw: init config

Mdio_open:294

sitara-cpsw: Open port 1

EnetPhy_bindDriver:1717

sitara-cpsw: Open port 2

EnetPhy_bindDriver:1717

PHY 3 is alive

PHY 15 is alive

initQs() txFreePktInfoQ initialized with 16 pkts

MAC port addr: f4:84:4c:fb:c0:42

unibase-1.1.5

app_start:gptp start done!

INF:def04:simpledb_open:no data is imported

INF:def04:uc_hwal_open:

INF:cbase:cb_rawsock_open:dmaTxChId=0 dmaRxChId=0 nTxPkts=16 nRxPkts=32 pktSize=1536

INF:cbase:Mac addr has not been allocated

INF:def04:000000-082218:uniconf_main:uniconf started

gptp_task: started.

gptp_task: dbname=INF:def04:get_exmodid_in_db:first xl4gptp:exmodid=0

INF:gptp:gptpman_run:max_domains=1, max_ports=2

INF:cbase:cb_rawsock_open:dmaTxChId=1 dmaRxChId=1 nTxPkts=16 nRxPkts=32 pktSize=1536

INF:cbase:Mac addr has not been allocated

INF:gptp:dev:tilld0 open success

INF:gptp:dev:tilld1 open success

INF:gptp:gptpnet_init:Open lldtsync OK!

INF:gptp:IEEE1588-2019 performance monitoring enabled.

INF:gptp:onenet_activate:tilld0 status=0, duplex=0, speed=0Mbps

INF:gptp:onenet_activate:tilld1 status=0, duplex=0, speed=0Mbps

INF:gptp:000000-250075:domainIndex=0, GM changed old=00:00:00:00:00:00:00:00, new=F4:84:4C:FF:FE:FB:C0:42

INF:gptp:gptpclock_set_gmsync:gptpInstanceIndex=0, domainIndex=0, gmstate=2

INF:gptp:set_phase_offsetGM:domainIndex=0, New adjustment(New GM?)

Cpsw_handleLinkUp:1449

MAC Port 1: link up

INF:gptp:index=1 speed=1000, duplex=full, ptpdev=tilld0

WRN:gptp:000003-754416:waiting_for_pdelay_resp_condition:sequenceId doesn't match, expected=19314, received=19313

WRN:gptp:000003-763396:waiting_for_pdelay_resp_condition:Discard this RESP and wait for the next one, this could be because of SM Reset. SeqId: expected=19314, received=19313

WRN:gptp:000003-778684:waiting_for_pdelay_resp_follow_up_condition:portIndex=1, sequenceId doesn't match, expected=19314, received=19313

WRN:gptp:000003-790751:waiting_for_pdelay_resp_follow_up_condition:portIndex=1, PdelayResp comes twice for the same PdelayReq, sequenceId=19314

INF:gptp:md_pdelay_resp_sm_recv_req:port=1, set receivedNonCMLDSPdelayReq=1

WRN:gptp:000004-749940:waiting_for_pdelay_interval_timer_proc:portIndex=1, sourcePortIdentity=68:05:CA:FF:FE:C8:7A:C2, thisClock=F4:84:4C:FF:FE:FB:C0:42, neighborPropDelay=202

INF:gptp:waiting_for_pdelay_interval_timer_proc:portIndex=1, not asCapable

5. 60s : CPU load = 5.53 %

INF:gptp:waiting_for_pdelay_interval_timer_proc:set asCapableAcrossDomains, portIndex=1

INF:gptp:set asCapable for domainIndex=0, portIndex=1

INF:gptp:000005-759595:gptpgcfg_set_asCapable:domainInde=0, portIndex=1, ascapable=1

INF:gptp:000005-767807:gm_stable:gm_unstable_proc:domainIndex=0

INF:gptp:gptpclock_set_gmsync:gptpInstanceIndex=0, domainIndex=0, gmstate=1

INF:gptp:000005-779397:gm_stable:gm_unstable_proc:domainIndex=0

INF:gptp:000005-874392:setSyncTwoStep_txSync:domainIndex=0, portIndex=1, sync gap=5874msec

INF:gptp:000005-879954:setFollowUp_txFollowUp:domainIndex=0, portIndex=1, fup gap=5879msec

INF:gptp:000006-775705:domainIndex=0, GM changed old=F4:84:4C:FF:FE:FB:C0:42, new=68:05:CA:FF:FE:C8:7A:C2

INF:gptp:gptpclock_set_gmsync:gptpInstanceIndex=0, domainIndex=0, gmstate=0

INF:gptp:000006-789098:gm_stable:gm_stable_proc:domainIndex=0

INF:gptp:000006-794316:gm_stable:gm_unstable_proc:domainIndex=0

INF:gptp:gptpclock_set_gmsync:gptpInstanceIndex=0, domainIndex=0, gmstate=1

INF:gptp:set_phase_offsetGM:domainIndex=0, New adjustment(New GM?)

INF:gptp:set_phase_offsetGM:domainIndex=0, offset adjustment, diff=475406949

INF:gptp:set_phase_offsetGM:domainIndex=0, stable

INF:gptp:clock_master_sync_receive:computeGmRateRatio:domainIndex=0 unstable rate=1944ppb (timeleap_future)

IFV:gptp:domainIndex=0, clock_master_sync_receive:the master clock rate to 3323ppb, GMdiff=13790nsec

IFV:gptp:domainIndex=0, clock_master_sync_receive:the master clock rate to 6646ppb, GMdiff=17036nsec

domain=0, offset=0nsec, hw-adjrate=6646ppb

gmsync=true, last_setts64=0nsec

...

...

25. 64s : CPU load = 4.40 %

IFV:gptp:domainIndex=0, clock_master_sync_receive:the master clock rate to 28683ppb, GMdiff=3809nsec

IFV:gptp:domainIndex=0, clock_master_sync_receive:the master clock rate to 27958ppb, GMdiff=1963nsec

IFV:gptp:domainIndex=0, clock_master_sync_receive:the master clock rate to 27135ppb, GMdiff=262nsec

IFV:gptp:domainIndex=0, clock_master_sync_receive:the master clock rate to 26240ppb, GMdiff=-1277nsec

domain=0, offset=0nsec, hw-adjrate=26240ppb

gmsync=true, last_setts64=0nsec