This example shows a application running in XIP (eXecute In Place) mode. This example can be used to check and evaluate the performance of the SOC when running in XIP mode.

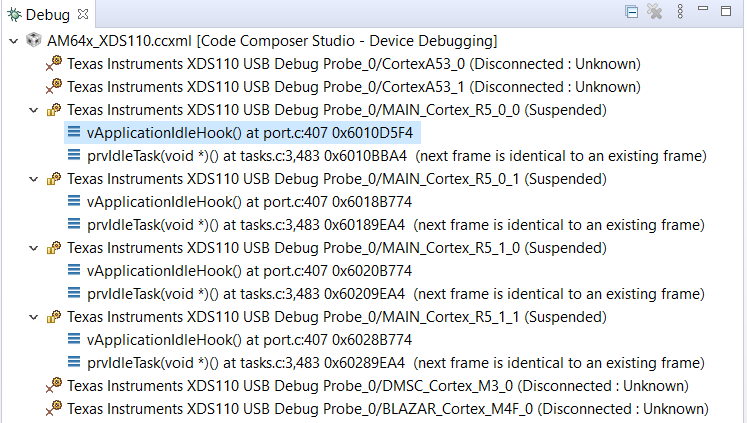

Shown below is a screenshot, after R5F is halted and symbols loaded, on AM64x. You can see the code execution is at flash region (0x60xxxxxx).

Starting OSPI Bootloader ...

DMSC Firmware Version 21.1.1--v2021.01a (Terrific Lla

DMSC Firmware revision 0x15

DMSC ABI revision 3.1

INFO: Bootloader_loadSelfCpu:203: CPU r5f0-0 is initialized to 800000000 Hz !!!

INFO: Bootloader_loadSelfCpu:203: CPU r5f0-1 is initialized to 800000000 Hz !!!

INFO: Bootloader_runCpu:151: CPU m4f0-0 is initialized to 400000000 Hz !!!

INFO: Bootloader_runCpu:151: CPU r5f1-0 is initialized to 800000000 Hz !!!

INFO: Bootloader_runCpu:151: CPU r5f1-1 is initialized to 800000000 Hz !!!

INFO: Bootloader_runSelfCpu:215: All done, reseting self ...

### XIP benchmark ###

[r5f0-1] 0.000387s :

[r5f0-1] 0.000450s : ### XIP benchmark ###

[r5f0-1] 0.000871s : FIR:

[r5f0-1] 0.000880s : 26721 cycles (code/data fully cached) ,

[r5f0-1] 0.000895s : 59814 cycles (code/data not cached) ,

[r5f0-1] 0.000908s : 30033 cycles (code/data not-cached 1 of 10 iterations)

[r5f0-1] 0.000960s : MEMCPY:

[r5f0-1] 0.000966s : 1564 cycles (code/data fully cached) ,

[r5f0-1] 0.000979s : 5073 cycles (code/data not cached) ,

[r5f0-1] 0.000992s : 1919 cycles (code/data not-cached 1 of 10 iterations)

[r5f0-1] 0.001018s : All tests have passed!!

[r5f0-1] 0.001029s :

[r5f1-0] 0.000386s :

[r5f1-0] 0.000449s : ### XIP benchmark ###

[r5f1-0] 0.000871s : FIR:

[r5f1-0] 0.000878s : 26721 cycles (code/data fully cached) ,

[r5f1-0] 0.000893s : 60349 cycles (code/data not cached) ,

[r5f1-0] 0.000906s : 30086 cycles (code/data not-cached 1 of 10 iterations)

[r5f1-0] 0.000958s : MEMCPY:

[r5f1-0] 0.000966s : 1564 cycles (code/data fully cached) ,

[r5f1-0] 0.000979s : 5002 cycles (code/data not cached) ,

[r5f1-0] 0.000991s : 1911 cycles (code/data not-cached 1 of 10 iterations)

[r5f1-0] 0.001017s : All tests have passed!!

[r5f1-0] 0.001027s :

[r5f1-1] 0.000384s :

[r5f1-1] 0.000446s : ### XIP benchmark ###

[r5f1-1] 0.000869s : FIR:

[r5f1-1] 0.000876s : 26721 cycles (code/data fully cached) ,

[r5f1-1] 0.000891s : 60298 cycles (code/data not cached) ,

[r5f1-1] 0.000904s : 30081 cycles (code/data not-cached 1 of 10 iterations)

[r5f1-1] 0.000956s : MEMCPY:

[r5f1-1] 0.000963s : 1564 cycles (code/data fully cached) ,

[r5f1-1] 0.000976s : 5057 cycles (code/data not cached) ,

[r5f1-1] 0.000988s : 1916 cycles (code/data not-cached 1 of 10 iterations)

[r5f1-1] 0.001014s : All tests have passed!!

[r5f1-1] 0.001024s :

FIR:

26721 cycles (code/data fully cached) ,

58646 cycles (code/data not cached) ,

30119 cycles (code/data not-cached 1 of 10 iterations)

MEMCPY:

1564 cycles (code/data fully cached) ,

4179 cycles (code/data not cached) ,

1830 cycles (code/data not-cached 1 of 10 iterations)

All tests have passed!!