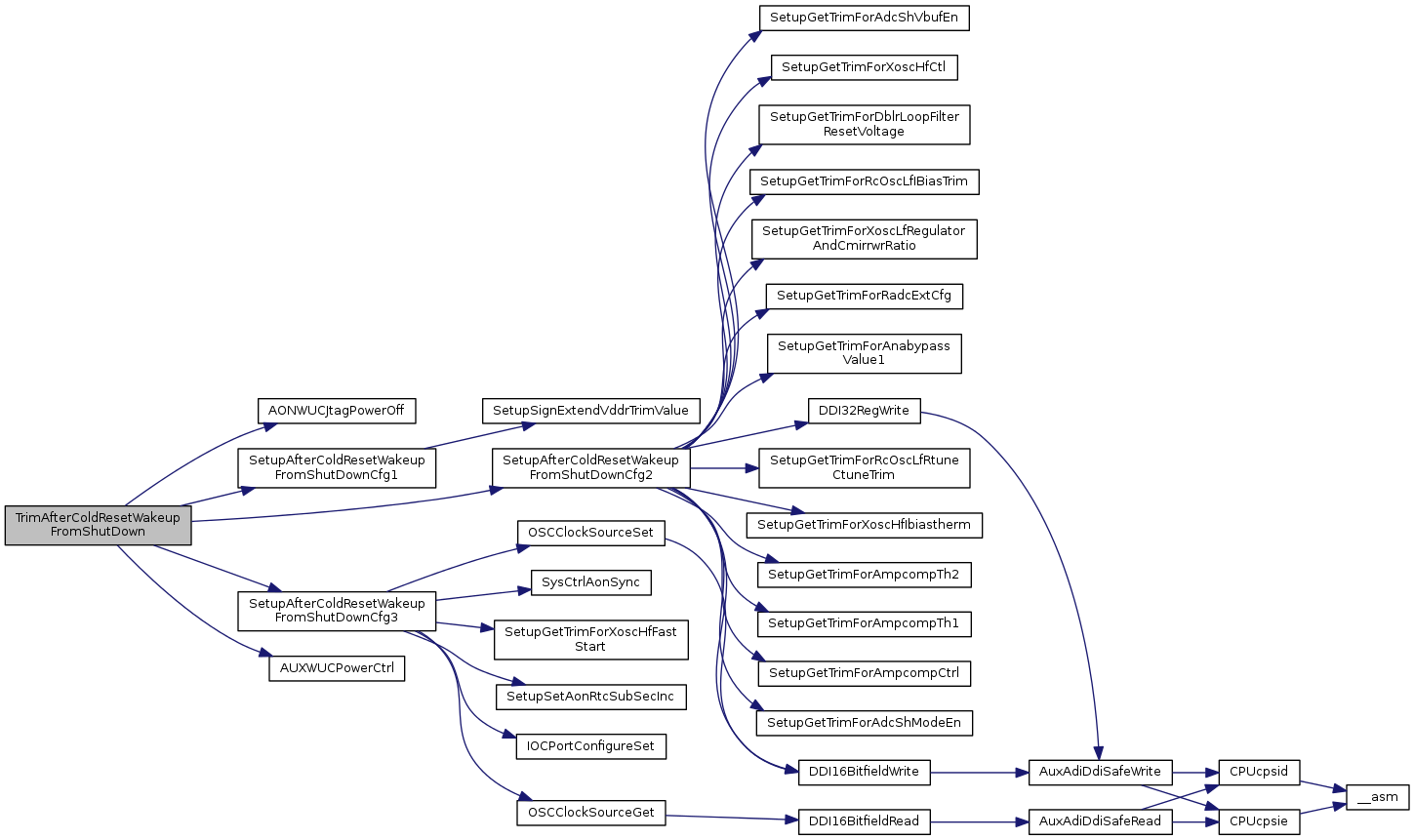

Trims to be applied when coming from SHUTDOWN (also called when coming from PIN_RESET).

251 uint32_t ccfg_ModeConfReg ;

258 HWREG(AON_WUC_BASE + AON_WUC_O_AUXCTL) = AON_WUC_AUXCTL_AUX_FORCE_ON;

261 while( ! ( HWREGBITW( AON_WUC_BASE + AON_WUC_O_PWRSTAT, AON_WUC_PWRSTAT_AUX_PD_ON_BITN )));

264 HWREG(AUX_WUC_BASE + AUX_WUC_O_MODCLKEN0) = AUX_WUC_MODCLKEN0_AUX_DDI0_OSC |

265 AUX_WUC_MODCLKEN0_AUX_ADI4;

270 if (( HWREG( CCFG_BASE + CCFG_O_SIZE_AND_DIS_FLAGS ) & CCFG_SIZE_AND_DIS_FLAGS_DIS_ALT_DCDC_SETTING ) == 0 ) {

274 HWREGB( ADI3_BASE + ADI_O_MASK4B + ( ADI_3_REFSYS_O_DCDCCTL5 * 2 )) = ( 0xF0 |

275 ( HWREG( CCFG_BASE + CCFG_O_MODE_CONF_1 ) >> CCFG_MODE_CONF_1_ALT_DCDC_IPEAK_S ));

278 HWREGB( ADI3_BASE + ADI_O_MASK4B + ( ADI_3_REFSYS_O_DCDCCTL5 * 2 )) = 0x72;

286 ccfg_ModeConfReg = HWREG( CCFG_BASE + CCFG_O_MODE_CONF );

295 #if ( CCFG_BASE == CCFG_BASE_DEFAULT )

298 NOROM_SetupAfterColdResetWakeupFromShutDownCfg2( ui32Fcfg1Revision, ccfg_ModeConfReg );

305 mp1rev = (( HWREG( FCFG1_BASE + FCFG1_O_TRIM_CAL_REVISION ) & FCFG1_TRIM_CAL_REVISION_MP1_M ) >>

306 FCFG1_TRIM_CAL_REVISION_MP1_S ) ;

307 if ( mp1rev < 527 ) {

308 uint32_t ldoTrimReg = HWREG( FCFG1_BASE + FCFG1_O_BAT_RC_LDO_TRIM );

309 uint32_t vtrim_bod = (( ldoTrimReg & FCFG1_BAT_RC_LDO_TRIM_VTRIM_BOD_M ) >>

310 FCFG1_BAT_RC_LDO_TRIM_VTRIM_BOD_S );

311 uint32_t vtrim_udig = (( ldoTrimReg & FCFG1_BAT_RC_LDO_TRIM_VTRIM_UDIG_M ) >>

312 FCFG1_BAT_RC_LDO_TRIM_VTRIM_UDIG_S );

313 if ( vtrim_bod > 0 ) {

316 if ( vtrim_udig != 7 ) {

317 if ( vtrim_udig == 6 ) {

320 vtrim_udig = (( vtrim_udig + 2 ) & 0xF );

323 HWREGB( ADI2_BASE + ADI_2_REFSYS_O_SOCLDOCTL0 ) =

324 ( vtrim_udig << ADI_2_REFSYS_SOCLDOCTL0_VTRIM_UDIG_S ) |

325 ( vtrim_bod << ADI_2_REFSYS_SOCLDOCTL0_VTRIM_BOD_S ) ;

331 #if ( CCFG_BASE == CCFG_BASE_DEFAULT )

334 NOROM_SetupAfterColdResetWakeupFromShutDownCfg3( ccfg_ModeConfReg );

342 HWREG( AUX_WUC_BASE + AUX_WUC_O_MODCLKEN0 ) = AUX_WUC_MODCLKEN0_AUX_DDI0_OSC;

345 HWREGBITW( FLASH_BASE + FLASH_O_CFG, FLASH_CFG_DIS_EFUSECLK_BITN ) = 1;

void SetupAfterColdResetWakeupFromShutDownCfg3(uint32_t ccfg_ModeConfReg)

Third part of configuration required when waking up from shutdown.

Definition: setup_rom.c:283

#define AUX_WUC_POWER_DOWN

Definition: aux_wuc.h:95

void AUXWUCPowerCtrl(uint32_t ui32PowerMode)

Control the power to the AUX domain.

Definition: aux_wuc.c:254

void SetupAfterColdResetWakeupFromShutDownCfg1(uint32_t ccfg_ModeConfReg)

First part of configuration required when waking up from shutdown.

Definition: setup_rom.c:123

void SetupAfterColdResetWakeupFromShutDownCfg2(uint32_t ui32Fcfg1Revision, uint32_t ccfg_ModeConfReg)

Second part of configuration required when waking up from shutdown.

Definition: setup_rom.c:178

static void AONWUCJtagPowerOff(void)

Request power off of the JTAG domain.

Definition: aon_wuc.h:792