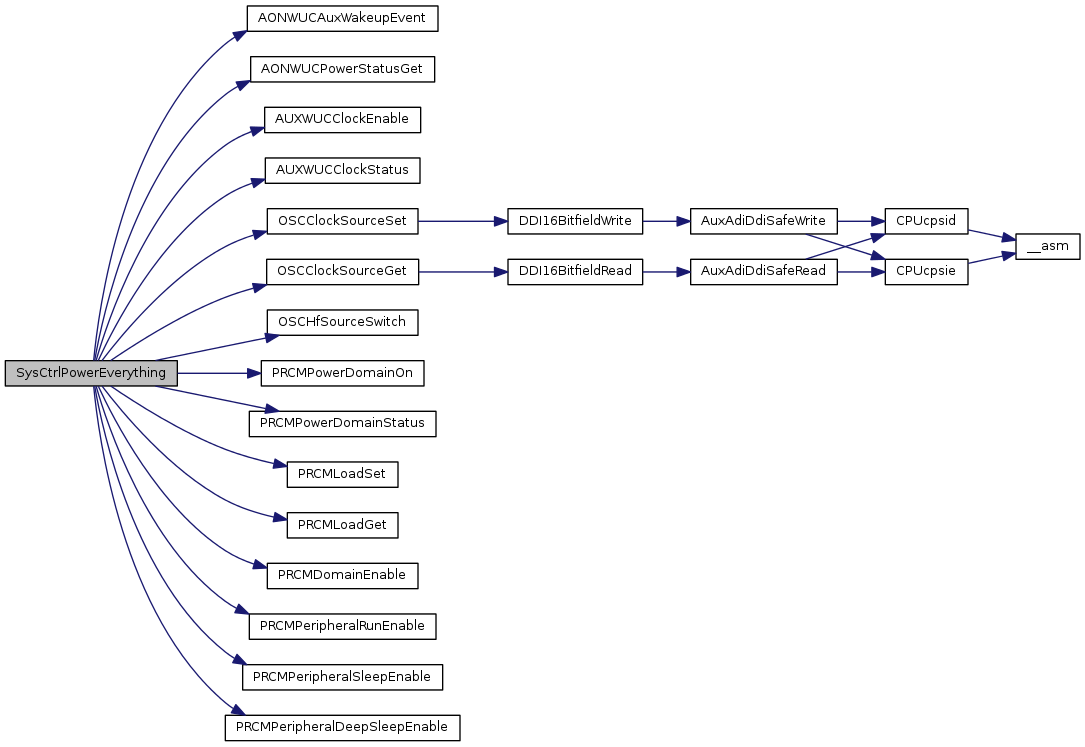

Power up everything.

123 uint32_t ui32AuxClocks;

#define AUX_WUC_TDC_CLOCK

Definition: aux_wuc.h:113

static void AONWUCAuxWakeupEvent(uint32_t ui32Mode)

Control the wake up procedure of the AUX domain.

Definition: aon_wuc.h:462

static uint32_t AONWUCPowerStatusGet(void)

Get the power status of the device.

Definition: aon_wuc.h:542

static void OSCHfSourceSwitch(void)

Switch the high frequency clock.

Definition: osc.h:314

void AUXWUCClockEnable(uint32_t ui32Clocks)

Enable clocks for peripherals in the AUX domain.

Definition: aux_wuc.c:64

#define OSC_SRC_CLK_MF

Definition: osc.h:113

static const uint32_t g_pui32ModuleCG[]

Definition: sys_ctrl.c:97

#define AUX_WUC_OSCCTRL_CLOCK

Definition: aux_wuc.h:109

uint32_t AUXWUCClockStatus(uint32_t ui32Clocks)

Get the status of a clock.

Definition: aux_wuc.c:150

uint32_t OSCClockSourceGet(uint32_t ui32SrcClk)

Get the source clock settings.

Definition: osc.c:147

uint32_t PRCMPowerDomainStatus(uint32_t ui32Domains)

Get the status for a specific power domain.

Definition: prcm.c:539

#define AUX_WUC_CLOCK_READY

Definition: aux_wuc.h:119

#define PRCM_DOMAIN_VIMS

Definition: prcm.h:142

#define AUX_WUC_AIODIO0_CLOCK

Definition: aux_wuc.h:104

#define AUX_WUC_ADI_CLOCK

Definition: aux_wuc.h:110

#define AONWUC_AUX_POWER_ON

Definition: aon_wuc.h:172

#define OSC_SRC_CLK_HF

Definition: osc.h:112

void PRCMPeripheralSleepEnable(uint32_t ui32Peripheral)

Enables a peripheral in sleep mode.

Definition: prcm.c:475

#define AUX_WUC_AIODIO1_CLOCK

Definition: aux_wuc.h:105

#define PRCM_DOMAIN_PERIPH

Definition: prcm.h:138

static bool PRCMLoadGet(void)

Check if any of the load sensitive register has been updated.

Definition: prcm.h:566

#define OSC_XOSC_HF

Definition: osc.h:117

#define AONWUC_AUX_WAKEUP

Definition: aon_wuc.h:152

#define OSC_SRC_CLK_LF

Definition: osc.h:114

#define AUX_WUC_SMPH_CLOCK

Definition: aux_wuc.h:103

#define AUX_WUC_REF_CLOCK

Definition: aux_wuc.h:115

#define AUX_WUC_TDCIF_CLOCK

Definition: aux_wuc.h:108

static void PRCMDomainEnable(uint32_t ui32Domains)

Enable clock domains in the MCU voltage domain.

Definition: prcm.h:594

#define PRCM_DOMAIN_POWER_ON

Definition: prcm.h:153

void PRCMPowerDomainOn(uint32_t ui32Domains)

Turn power on in power domains in the MCU domain.

Definition: prcm.c:359

#define AUX_WUC_ANAIF_CLOCK

Definition: aux_wuc.h:107

#define PRCM_DOMAIN_SERIAL

Definition: prcm.h:136

#define PRCM_DOMAIN_RFCORE

Definition: prcm.h:134

static void PRCMLoadSet(void)

Use this function to synchronize the load settings.

Definition: prcm.h:548

void PRCMPeripheralRunEnable(uint32_t ui32Peripheral)

Enables a peripheral in Run mode.

Definition: prcm.c:443

void PRCMPeripheralDeepSleepEnable(uint32_t ui32Peripheral)

Enables a peripheral in deep-sleep mode.

Definition: prcm.c:507

#define AUX_WUC_ADC_CLOCK

Definition: aux_wuc.h:114

void OSCClockSourceSet(uint32_t ui32SrcClk, uint32_t ui32Osc)

Configure the oscillator input to the a source clock.

Definition: osc.c:100

#define OSC_XOSC_LF

Definition: osc.h:119

#define AUX_WUC_TIMER_CLOCK

Definition: aux_wuc.h:106