|

|

SPI driver implementation for a CC32XX SPI controller using the micro DMA controller.

The SPI header file should be included in an application as follows:

Refer to SPI.h for a complete description of APIs & example of use.

This SPI driver implementation is designed to operate on a CC32XX SPI controller using a micro DMA controller.

This SPI controller supports 4 phase & polarity formats. Refer to the device specific data sheets & technical reference manuals for specifics on each format.

This SPI controller supports a hardware chip select pin. Refer to the device's user manual on how this hardware chip select pin behaves in regards to the SPI frame format.

| Chip select type | SPI_MASTER mode | SPI_SLAVE mode |

|---|---|---|

| Hardware chip select | No action is needed by the application to select the peripheral. | See the device documentation on it's chip select requirements. |

| Software chip select | The application is responsible to ensure that correct SPI slave is selected before performing a SPI_transfer(). | See the device documentation on it's chip select requirements. |

SPI data frames can be any size from 4-bits to 32-bits. The SPI data frame size is set in SPI_Params.dataSize passed to SPI_open. The SPICC32XXDMA driver implementation makes assumptions on the element size of the SPI_Transaction txBuf and rxBuf arrays, based on the data frame size. If the data frame size is less than or equal to 8 bits, txBuf and rxBuf are assumed to be arrays of 8-bit uint8_t elements. If the data frame size is greater than 8 bits, but less than or equal to 16 bits, txBuf and rxBuf are assumed to be arrays of 16-bit uint16_t elements. Otherwise, txBuf and rxBuf are assumed to point to 32-bit uint32_t elements.

| data frame size | buffer element size |

|---|---|

| 4-8 bits | uint8_t |

| 9-16 bits | uint16_t |

| 17-32 bits | uint32_t |

Data buffers in transactions (rxBuf & txBuf) must be address aligned according to the data frame size. For example, if data frame is 9-bit (driver assumes buffers are uint16_t) rxBuf & txBuf must be aligned on a 16-bit address boundary, if data frame is 20-bit (driver assumes buffers are uint32_t) rxBuf & txBuf must be aligned on a 32-bit address boundary.

This driver is designed to operate with the micro DMA. The micro DMA generates an interrupt on the perpheral's interrupt vector. This implementation automatically installs a DMA aware hardware ISR to service the assigned micro DMA channels.

This driver utilizes DMA channels in ping pong mode (see device TRM) in order to overcome the 1024 item DMA channel limit. This means the driver can execute multi kilo-item transactions without pausing to reconfigure the DMA and causing gaps in transmission. In addition, the driver also allows the user to queue up transfers when opened in SPI_MODE_CALLBACK by calling SPI_transfer() multiple times. Note that each transaction's SPI_Transaction struct must still be persistent and unmodified until that transaction is complete.

Below is an example of queueing three transactions

As this driver uses uDMA to transfer data/from data buffers, it is the responsibility of the application to ensure that these buffers reside in memory that is accessible by the DMA.

A uint32_t scratch buffer is used to allow SPI_transfers where txBuf or rxBuf are NULL. Rather than requiring txBuf or rxBuf to have a dummy buffer of size of the transfer count, a single DMA accessible uint32_t scratch buffer is used. When rxBuf is NULL, the uDMA will transfer all the SPI data receives into the scratch buffer as a "bit-bucket". When txBuf is NULL, the scratch buffer is initialized to defaultTxBufValue so the uDMA will send some known value. Each SPI driver instance must have its own scratch buffer.

When used in blocking mode small SPI transfers are can be done by polling the peripheral & sending data frame-by-frame. This will not block the task which requested the transfer, but instead immediately perform the transfer & return. The minDmaTransferSize field in the hardware attributes is the threshold; if the transaction count is below the threshold a polling transfer is performed; otherwise a DMA transfer is done. This is intended to reduce the overhead of setting up a DMA transfer to only send a few data frames. Keep in mind that during polling transfers the current task is still being executed; there is no context switch to another task.

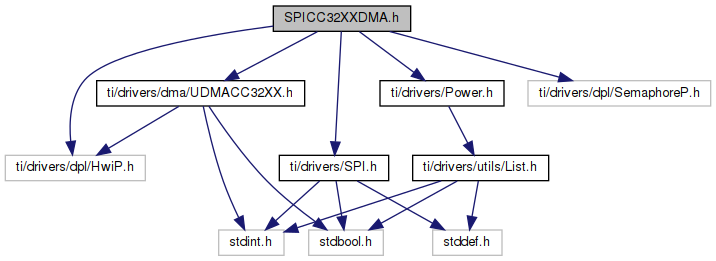

#include <ti/drivers/dpl/HwiP.h>#include <ti/drivers/dpl/SemaphoreP.h>#include <ti/drivers/Power.h>#include <ti/drivers/SPI.h>#include <ti/drivers/dma/UDMACC32XX.h>

Go to the source code of this file.

Data Structures | |

| struct | SPICC32XXDMA_HWAttrsV1 |

| SPICC32XXDMA Hardware attributes. More... | |

| struct | SPICC32XXDMA_Object |

| SPICC32XXDMA Object. More... | |

Macros | |

| #define | SPICC32XXDMA_PIN_NO_CONFIG 0xFFFF |

| Indicates a pin is not to be configured by the SPICC32XXDMA driver. More... | |

Typedefs | |

| typedef struct SPICC32XXDMA_Object * | SPICC32XXDMA_Handle |

Variables | |

| const SPI_FxnTable | SPICC32XXDMA_fxnTable |

| #define SPICC32XXDMA_PIN_NO_CONFIG 0xFFFF |

Indicates a pin is not to be configured by the SPICC32XXDMA driver.

| typedef struct SPICC32XXDMA_Object * SPICC32XXDMA_Handle |

| const SPI_FxnTable SPICC32XXDMA_fxnTable |