|

|

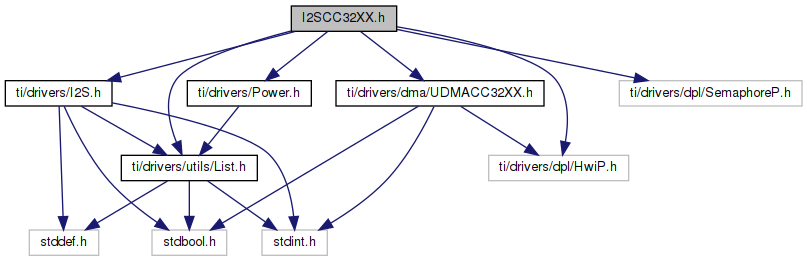

I2S driver implementation for a CC32XX I2S controller.

============================================================================

#include <ti/drivers/I2S.h>#include <ti/drivers/dma/UDMACC32XX.h>#include <ti/drivers/dpl/SemaphoreP.h>#include <ti/drivers/dpl/HwiP.h>#include <ti/drivers/utils/List.h>#include <ti/drivers/Power.h>

Go to the source code of this file.

Data Structures | |

| struct | I2SCC32XX_HWAttrs_ |

| I2S Hardware attributes. More... | |

Typedefs | |

| typedef struct I2SCC32XX_HWAttrs_ | I2SCC32XX_HWAttrs |

| I2S Hardware attributes. More... | |

| typedef void(* | I2SCC32XX_FifoUpdate) (uintptr_t arg) |

| The definition of a function used by the I2S driver to refresh the FIFO. More... | |

| typedef struct I2SCC32XX_HWAttrs_ I2SCC32XX_HWAttrs |

I2S Hardware attributes.

intPriority is the I2S peripheral's interrupt priority, as defined by the TI-RTOS kernel. This value is passed unmodified to Hwi_create().

pinSD1 and pinSD0 define the SD0 and SD1 data pin mapping, respectively. pinSCK, pinMCLK and pinWS define the SCK, MCLK and WS clock pin mapping, respectively. All these pins are typically defined with a macro in a header file, which maps to an IOID.

rxChannelIndex and txChannelIndex are uDMA channels respectively used for the read and the write interface.

A sample structure is shown below:

| typedef void(* I2SCC32XX_FifoUpdate) (uintptr_t arg) |

The definition of a function used by the I2S driver to refresh the FIFO.

| I2S_Handle | I2S_Handle |