Data Structures | |

| struct | SPLL_1PH_SOGI_FLL_OSG_COEFF |

| Defines the SPLL_1PH_SOGI_FLL_OSG_COEFF structure. More... | |

| struct | SPLL_1PH_SOGI_FLL_LPF_COEFF |

| Defines the SPLL_1PH_SOGI_FLL_LPF_COEFF structure. More... | |

| struct | SPLL_1PH_SOGI_FLL |

| Defines the Orthogonal Signal Generator SPLL_1PH_SOGI_FLL structure. More... | |

Functions | |

| static void | SPLL_1PH_SOGI_FLL_reset (SPLL_1PH_SOGI_FLL *spll_obj) |

| Resets internal data to zero,. More... | |

| static void | SPLL_1PH_SOGI_FLL_coeff_calc (SPLL_1PH_SOGI_FLL *spll_obj) |

| Calculates the SPLL_1PH_SOGI_FLL coefficients. More... | |

| static void | SPLL_1PH_SOGI_FLL_config (SPLL_1PH_SOGI_FLL *spll_obj, float32_t acFreq, float32_t isrFrequency, float32_t lpf_b0, float32_t lpf_b1, float32_t k, float32_t gamma) |

| Configures the SPLL_1PH_SOGI_FLL coefficients. More... | |

| static void | SPLL_1PH_SOGI_FLL_run (SPLL_1PH_SOGI_FLL *spll_obj, float32_t acValue) |

| Runs SPLL_1PH_SOGI_FLL module. More... | |

Typedefs | |

| typedef float | float32_t |

| typedef long double | float64_t |

Macros | |

| #define | C2000_IEEE754_TYPES |

The SPLL_1PH_SOGI_FLL API provides a set of functions that implements a software phase lock loop based on orthogonal signal generation using second order generalized integrators and frequency locked loop.

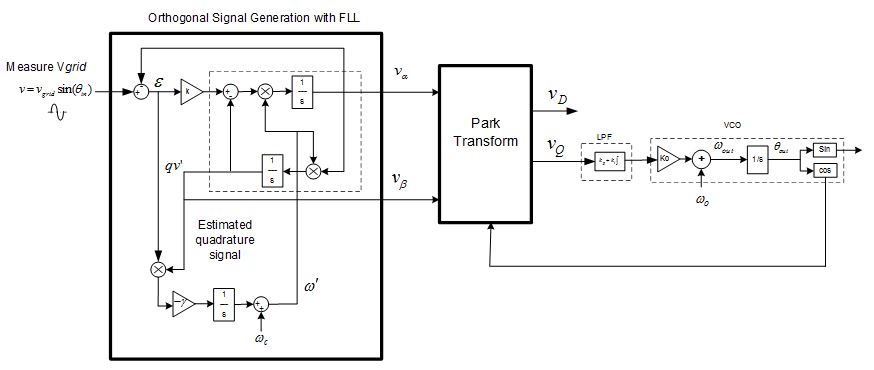

This module follows the same basic structure as the SPLL_1PH_SOGI module and adds to the module a frequency adaptive feature through a frequency locked loop. The module implemented was first proposed by Rodriguez,P. ,Luna,A. , Candela,I. ,Teodorescu, R. , and Blaabjerg, F. in 'Grid Synchronization of Power Converters Using Multiple Second Order Generalized Integrators', In Proceedings of IEEE industrial Electronics Conference (IECON'08), November 2008, pp 755-760. An interesting relation was identified in the paper that the quadrature and the error component are in phase when the center frequency is greater than the actual and out of phase when it is lower than the actual. This feature is used to design a frequency locked loop as shown in figure below.

The value of k and γ are identified through simulation.

The following is a sequence of steps that can be followed to use the SPLL_1PH_SOGI_FLL API library functions in an existing C program. For a set of code examples that illustrates the use of this library, see the examples in the Digial Power SDK.

Before you can using the library you must add the libraries directory path as a searchable directory in the project include options. This can be done by right-clicking on the project in the Project Explorer window, selecting "Properties". In the window that opens, navigate to "Build, C2000 Compiler, Include Options". In the include path

window, click on the green add directory path button on the right and enter the path to the Digital Power SDK libraries directory.

This allows CCS to search the entire directory for library files.

Once that is done you should follow these steps incorporate this library into your project:

There is only one module in this package, the APIs can be referenced at SPLL_1PH_SOGI_FLL. The module headers are located at spll_1ph_sogi_fll.h.

| #define C2000_IEEE754_TYPES |

Definition at line 48 of file spll_1ph_sogi_fll.h.

| typedef float float32_t |

Definition at line 53 of file spll_1ph_sogi_fll.h.

| typedef long double float64_t |

Definition at line 54 of file spll_1ph_sogi_fll.h.

|

inlinestatic |

Resets internal data to zero,.

| *spll_obj | The SPLL_1PH_SOGI_FLL structure pointer |

Definition at line 117 of file spll_1ph_sogi_fll.h.

|

inlinestatic |

Calculates the SPLL_1PH_SOGI_FLL coefficients.

| *spll_obj | The SPLL_1PH_SOGI_FLL structure pointer |

Definition at line 157 of file spll_1ph_sogi_fll.h.

|

inlinestatic |

Configures the SPLL_1PH_SOGI_FLL coefficients.

| *spll_obj | The SPLL_1PH_SOGI_FLL structure pointer |

| acFreq | Nominal AC frequency for the SPLL Module |

| isrFrequency | Nominal AC frequency for the SPLL Module |

| lpf_b0 | B0 coefficient of LPF of SPLL |

| lpf_b1 | B1 coefficient of LPF of SPLL |

| k | k parameter for FLL |

| gamma | gamma parameter for FLL |

Definition at line 188 of file spll_1ph_sogi_fll.h.

|

inlinestatic |

Runs SPLL_1PH_SOGI_FLL module.

| *spll_obj | The SPLL_1PH_SOGI_FLL structure pointer |

| acValue | AC grid voltage in per unit (pu) |

Definition at line 214 of file spll_1ph_sogi_fll.h.