Data Structures | |

| struct | SPLL_1PH_SOGI_OSG_COEFF |

| Defines the SPLL_1PH_SOGI_OSG_COEFF structure. More... | |

| struct | SPLL_1PH_SOGI_LPF_COEFF |

| Defines the SPLL_1PH_SOGI_LPF_COEFF structure. More... | |

| struct | SPLL_1PH_SOGI |

| Defines the Orthogonal Signal Generator SPLL_1PH_SOGI structure. More... | |

Functions | |

| static void | SPLL_1PH_SOGI_reset (SPLL_1PH_SOGI *spll_obj) |

| Resets internal storage data of the module. More... | |

| static void | SPLL_1PH_SOGI_coeff_calc (SPLL_1PH_SOGI *spll_obj) |

| Calculates the SPLL_1PH_SOGI coefficient. More... | |

| static void | SPLL_1PH_SOGI_config (SPLL_1PH_SOGI *spll_obj, float32_t acFreq, float32_t isrFrequency, float32_t lpf_b0, float32_t lpf_b1) |

| Configures the SPLL_1PH_SOGI module. More... | |

| static void | SPLL_1PH_SOGI_run (SPLL_1PH_SOGI *spll_obj, float32_t acValue) |

| Run the SPLL_1PH_SOGI module. More... | |

Typedefs | |

| typedef float | float32_t |

| typedef long double | float64_t |

Macros | |

| #define | C2000_IEEE754_TYPES |

The Orthogonal Signal Generator SPLL for Software Phase Grid (SPLL_1PH_SOGI) API provides a set of functions that implements a software phase lock loop based on orthogonal signal generation using second order generalized integrators. This block can be further used in P and Q style control for single phase grid connected equipment.

The single phase grid software PLL design is tricky because of twice the grid frequency component present in the phase detect output. Notch filter is used in the SPLL_1PH_NOTCH module implementation for this and achieves satisfactory results. Another alternative is to use an orthogonal signal generator scheme and then use park transformation. This software block uses a second order integrator to generate the orthogonal signal from the sensed single phase grid voltage (As proposed in 'A New Software Phase PLL Structure Based on Second Order Generalized Integrator', Mihai Ciobotaru, PESC'06).

A functional diagram of a PLL is shown in the figure below, which consists of a phase detect (PD) consisting of park transform, a loop filter(LPF) and a voltage controlled oscillator(VCO).

The second order generalized integrator closed loop transfer function can be written as:

![\[ H_{d}(s) = \frac{v'}v (s) = \frac{k{\omega_{n}}s} {{s}^{2} + k{\omega_{n}}s + {\omega_{n}}^2} \]](form_42.png)

and

![\[ H_{q}(s) = \frac{qv'}v (s) = \frac{k{{\omega_{n}}}^2} {{s}^{2} + k{\omega_{n}}s + {\omega_{n}}^2} \]](form_43.png)

For discrete implementation using trapezoidal approximation:

![\[ H_{d}(z) = \frac{k{\omega_{n}}\frac{2}{T_{s}}\frac{z-1}{z+1}} {(\frac{2}{T_{s}}\frac{z-1}{z+1})^2 + k{\omega_{n}}\frac{2}{T_{s}}\frac{z-1}{z+1} + {\omega_{n}}^2} = \frac{(2k{\omega_{n}}T_{s})({z}^2 -1)} {4({z-1})^2 + (2k{\omega_{n}}T_{s})({z}^2 -1) + ({\omega_{n}}{T_{s}})^2(z+1)^2} \]](form_44.png)

Now using

![\[ x = 2k{\omega_{n}}T_{s}\]](form_45.png)

and

![\[ y=({\omega_{n}}T_{s})^2 \]](form_46.png)

![\[ H_{d}(z) = \frac{(\frac{x}{x+y+4}) + (\frac{-x}{x+y+4}){z}^{-2}} {1 - (\frac{2(4-y)}{x+y+4}){z}^{-1} - (\frac{x-y-4}{x+y+4}){z}^{-2}} = \frac{b_{0} + {b_{2}{z}^{-2}}} {1 - {a_{1}{z}^{-1}} - {a_{2}{z}^{-2}}} \]](form_47.png)

Similarly

![\[ H_{q}(z) = \frac{(\frac{k*y}{x+y+4}) + 2(\frac{k*y}{x+y+4}){z}^{-1} + (\frac{k*y}{x+y+4}){z}^{-2}} {1 - (\frac{2(4-y)}{x+y+4}){z}^{-1} - (\frac{x-y-4}{x+y+4}){z}^{-2}} = \frac{q{b_{0}} + q{b_{1}{z}^{-1}} + q{b_{2}{z}^{-3}}} {1 - {a_{1}{z}^{-1}} - {a_{2}{z}^{-2}}} \]](form_48.png)

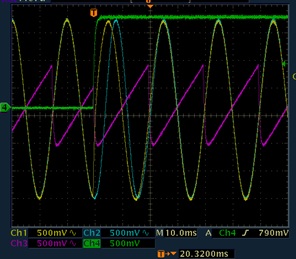

Once the orthogonal signal is generated park transform is used to detect the Q and D components on the rotating reference frame. This is then fed to the loop filter which controls the VCO of the PLL. The tuning of the loop filter is similar to what is described in the SPLL_1PH_NOTCH description. Very fast transient response is possible as shown in the figure below where CH1: is the grid sine value CH2: is the PLL lock CH3: is the grid theta and CH4: is the phase jump.

The coefficients of the orthogonal signal generator can be tuned for varying grid frequency and sampling time (ISR frequency). The only variable is k, which determines the selectiveness of the frequency for the second order integrator. The second order generalized integrator presented can be also modified to extract the harmonic frequency component if needed in a grid monitoring application. A lower k value must be selected for this purpose, however lower k has an effect slowing the response. The figure below shows the extraction of the 5th harmonic using the SOGI. The implementation of this is left for the user as it directly follows from the SOGI implementation shown in SPLL_1ph_SOGI.

Additionally the RMS voltage of the grid can also be estimated using the below equation:

![\[ V_{RMS} = \frac{1}{\sqrt{2}} {\sqrt{{v}^{'2}+q{v}^{'2}}} \]](form_49.png)

The following is a sequence of steps that can be followed to use the SPLL_1PH_SOGI API library functions in an existing C program. For a set of code examples that illustrates the use of this library, see the examples in the Digial Power SDK.

Before you can using the library you must add the libraries directory path as a searchable directory in the project include options. This can be done by right-clicking on the project in the Project Explorer window, selecting "Properties". In the window that opens, navigate to "Build, C2000 Compiler, Include Options". In the include path

window, click on the green add directory path button on the right and enter the path to the Digital Power SDK libraries directory.

This allows CCS to search the entire directory for library files.

Once that is done you should follow these steps incorporate this library into your project:

There is only one module in this package, the APIs can be referenced at SPLL_1PH_SOGI. The module headers are located at spll_1ph_sogi.h.

| #define C2000_IEEE754_TYPES |

Definition at line 48 of file spll_1ph_sogi.h.

| typedef float float32_t |

Definition at line 53 of file spll_1ph_sogi.h.

| typedef long double float64_t |

Definition at line 54 of file spll_1ph_sogi.h.

|

inlinestatic |

Resets internal storage data of the module.

| *spll_obj | The SPLL_1PH_SOGI structure pointer |

Definition at line 112 of file spll_1ph_sogi.h.

|

inlinestatic |

Calculates the SPLL_1PH_SOGI coefficient.

| *spll_obj | The SPLL_1PH_SOGI structure |

Definition at line 147 of file spll_1ph_sogi.h.

|

inlinestatic |

Configures the SPLL_1PH_SOGI module.

| *spll_obj | The SPLL_1PH_SOGI structure |

| acFreq | Nominal AC frequency for the SPLL Module |

| isrFrequency | Frequency at which SPLL module is run |

| lpf_b0 | B0 coefficient of LPF of SPLL |

| lpf_b1 | B1 coefficient of LPF of SPLL |

Definition at line 174 of file spll_1ph_sogi.h.

|

inlinestatic |

Run the SPLL_1PH_SOGI module.

| *spll_obj | The SPLL_1PH_SOGI structure pointer |

| acValue | AC grid voltage in per unit (pu) |

Definition at line 194 of file spll_1ph_sogi.h.