Functions | |

| static void | UARTParityModeSet (uint32_t ui32Base, uint32_t ui32Parity) |

| Sets the type of parity. More... | |

| static uint32_t | UARTParityModeGet (uint32_t ui32Base) |

| Gets the type of parity currently being used. More... | |

| static void | UARTFIFOLevelSet (uint32_t ui32Base, uint32_t ui32TxLevel, uint32_t ui32RxLevel) |

| Sets the FIFO level at which interrupts are generated. More... | |

| void | UARTFIFOLevelGet (uint32_t ui32Base, uint32_t *pui32TxLevel, uint32_t *pui32RxLevel) |

| Gets the FIFO level at which interrupts are generated. More... | |

| void | UARTConfigSetExpClk (uint32_t ui32Base, uint32_t ui32UARTClk, uint32_t ui32Baud, uint32_t ui32Config) |

| Sets the configuration of a UART. More... | |

| void | UARTConfigGetExpClk (uint32_t ui32Base, uint32_t ui32UARTClk, uint32_t *pui32Baud, uint32_t *pui32Config) |

| Gets the current configuration of a UART. More... | |

| static void | UARTEnable (uint32_t ui32Base) |

| Enables transmitting and receiving. More... | |

| void | UARTDisable (uint32_t ui32Base) |

| Disables transmitting and receiving. More... | |

| static void | UARTFIFOEnable (uint32_t ui32Base) |

| Enables the transmit and receive FIFOs. More... | |

| static void | UARTFIFODisable (uint32_t ui32Base) |

| Disables the transmit and receive FIFOs. More... | |

| static bool | UARTCharsAvail (uint32_t ui32Base) |

| Determines if there are any characters in the receive FIFO. More... | |

| static bool | UARTSpaceAvail (uint32_t ui32Base) |

| Determines if there is any space in the transmit FIFO. More... | |

| int32_t | UARTCharGetNonBlocking (uint32_t ui32Base) |

| Receives a character from the specified port. More... | |

| int32_t | UARTCharGet (uint32_t ui32Base) |

| Waits for a character from the specified port. More... | |

| bool | UARTCharPutNonBlocking (uint32_t ui32Base, uint8_t ui8Data) |

| Sends a character to the specified port. More... | |

| void | UARTCharPut (uint32_t ui32Base, uint8_t ui8Data) |

| Waits to send a character from the specified port. More... | |

| static bool | UARTBusy (uint32_t ui32Base) |

| Determines whether the UART transmitter is busy or not. More... | |

| static void | UARTBreakCtl (uint32_t ui32Base, bool bBreakState) |

| Causes a BREAK to be sent. More... | |

| void | UARTIntRegister (uint32_t ui32Base, void(*pfnHandler)(void)) |

| Registers an interrupt handler for a UART interrupt in the dynamic interrupt table. More... | |

| void | UARTIntUnregister (uint32_t ui32Base) |

| Unregisters an interrupt handler for a UART interrupt in the dynamic interrupt table. More... | |

| static void | UARTIntEnable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| Enables individual UART interrupt sources. More... | |

| static void | UARTIntDisable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| Disables individual UART interrupt sources. More... | |

| static uint32_t | UARTIntStatus (uint32_t ui32Base, bool bMasked) |

| Gets the current interrupt status. More... | |

| static void | UARTIntClear (uint32_t ui32Base, uint32_t ui32IntFlags) |

| Clears UART interrupt sources. More... | |

| static void | UARTDMAEnable (uint32_t ui32Base, uint32_t ui32DMAFlags) |

| Enable UART DMA operation. More... | |

| static void | UARTDMADisable (uint32_t ui32Base, uint32_t ui32DMAFlags) |

| Disable UART DMA operation. More... | |

| static uint32_t | UARTRxErrorGet (uint32_t ui32Base) |

| Gets current receiver errors. More... | |

| static void | UARTRxErrorClear (uint32_t ui32Base) |

| Clears all reported receiver errors. More... | |

| static void | UARTHwFlowControlEnable (uint32_t ui32Base) |

| Enables hardware flow control for both CTS and RTS. More... | |

| static void | UARTHwFlowControlDisable (uint32_t ui32Base) |

| Disables hardware flow control for both CTS and RTS. More... | |

DriverLib only supports writing a single character at a time to the UART buffer but it is possible to utilize the library function printf by overriding a few of the functions used by printf with a device specific definition. However, the implementation of printf is compiler specific and requires different functions to be overridden depending on the compiler.

Using printf can increase code size significantly but some compilers provide a highly optimized and configurable implementation suitable for embedded systems which makes the code size increase acceptable for most applications. See the compiler's documentation for details about how to configure the printf library function.

It is required that the application configures and enables the UART module before using printf function.

In Code Composer Studio the functions fputc and fputs must be overridden.

In IAR the function putchar must be overridden.

|

inlinestatic |

Causes a BREAK to be sent.

| ui32Base | is the base address of the UART port. |

| bBreakState | controls the output level.

|

|

inlinestatic |

Determines whether the UART transmitter is busy or not.

Allows the caller to determine whether all transmitted bytes have cleared the transmitter hardware. If false is returned, the transmit FIFO is empty and all bits of the last transmitted character, including all stop bits, have left the hardware shift register.

| ui32Base | is the base address of the UART port. |

true : UART is transmitting.false : All transmissions are complete. | int32_t UARTCharGet | ( | uint32_t | ui32Base | ) |

Waits for a character from the specified port.

This function gets a character from the receive FIFO for the specified port. If there are no characters available, this function waits until a character is received before returning.

| ui32Base | is the base address of the UART port. |

int32_t. | int32_t UARTCharGetNonBlocking | ( | uint32_t | ui32Base | ) |

Receives a character from the specified port.

This function gets a character from the receive FIFO for the specified port.

| ui32Base | is the base address of the UART port. |

int32_t. A -1 is returned if there are no characters present in the receive FIFO.| void UARTCharPut | ( | uint32_t | ui32Base, |

| uint8_t | ui8Data | ||

| ) |

Waits to send a character from the specified port.

This function sends the character ui8Data to the transmit FIFO for the specified port. If there is no space available in the transmit FIFO, this function waits until there is space available before returning.

| ui32Base | is the base address of the UART port. |

| ui8Data | is the character to be transmitted. |

| bool UARTCharPutNonBlocking | ( | uint32_t | ui32Base, |

| uint8_t | ui8Data | ||

| ) |

Sends a character to the specified port.

This function writes the character ui8Data to the transmit FIFO for the specified port. This function does not block, so if there is no space available, then a false is returned, and the application must retry the function later.

| ui32Base | is the base address of the UART port. |

| ui8Data | is the character to be transmitted. |

true : The character was successfully placed in the transmit FIFO.false : There was no space available in the transmit FIFO. Try again later.

|

inlinestatic |

Determines if there are any characters in the receive FIFO.

This function returns a flag indicating whether or not there is data available in the receive FIFO.

| ui32Base | is the base address of the UART port. |

true : There is data in the receive FIFO.false : There is no data in the receive FIFO. | void UARTConfigGetExpClk | ( | uint32_t | ui32Base, |

| uint32_t | ui32UARTClk, | ||

| uint32_t * | pui32Baud, | ||

| uint32_t * | pui32Config | ||

| ) |

Gets the current configuration of a UART.

The baud rate and data format for the UART is determined, given an explicitly provided peripheral clock (hence the ExpClk suffix). The returned baud rate is the actual baud rate; it may not be the exact baud rate requested or an "official" baud rate. The data format returned in pui32Config is enumerated the same as the ui32Config parameter of UARTConfigSetExpClk().

| ui32Base | is the base address of the UART port. |

| ui32UARTClk | is the rate of the clock supplied to the UART module. |

| pui32Baud | is a pointer to storage for the baud rate. |

| pui32Config | is a pointer to storage for the data format. |

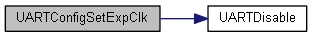

| void UARTConfigSetExpClk | ( | uint32_t | ui32Base, |

| uint32_t | ui32UARTClk, | ||

| uint32_t | ui32Baud, | ||

| uint32_t | ui32Config | ||

| ) |

Sets the configuration of a UART.

This function configures the UART for operation in the specified data format.

| ui32Base | is the base address of the UART port. |

| ui32UARTClk | is the rate of the clock supplied to the UART module. |

| ui32Baud | is the desired baud rate.

|

| ui32Config | is the data format for the port. The parameter is the bitwise OR of three values:

|

| void UARTDisable | ( | uint32_t | ui32Base | ) |

Disables transmitting and receiving.

This function clears the UARTEN, TXE, and RXE bits, waits for the end of transmission of the current character, and flushes the transmit FIFO.

| ui32Base | is the base address of the UART port. |

Referenced by UARTConfigSetExpClk().

|

inlinestatic |

Disable UART DMA operation.

This function is used to disable UART DMA features that were enabled by UARTDMAEnable(). The specified UART DMA features are disabled.

| ui32Base | is the base address of the UART port. |

| ui32DMAFlags | is a bit mask of the DMA features to disable. The parameter is the bitwise OR of any of the following values:

|

|

inlinestatic |

Enable UART DMA operation.

The specified UART DMA features are enabled. The UART can be configured to use DMA for transmit or receive, and to disable receive if an error occurs.

| ui32Base | is the base address of the UART port. |

| ui32DMAFlags | is a bit mask of the DMA features to enable. The parameter is the bitwise OR of any of the following values:

|

|

inlinestatic |

Enables transmitting and receiving.

This function sets the UARTEN, TXE, and RXE bits, and enables the transmit and receive FIFOs.

| ui32Base | is the base address of the UART port. |

|

inlinestatic |

Disables the transmit and receive FIFOs.

This functions disables the transmit and receive FIFOs in the UART.

| ui32Base | is the base address of the UART port. |

|

inlinestatic |

Enables the transmit and receive FIFOs.

This functions enables the transmit and receive FIFOs in the UART.

| ui32Base | is the base address of the UART port. |

| void UARTFIFOLevelGet | ( | uint32_t | ui32Base, |

| uint32_t * | pui32TxLevel, | ||

| uint32_t * | pui32RxLevel | ||

| ) |

Gets the FIFO level at which interrupts are generated.

This function gets the FIFO level at which transmit and receive interrupts are generated.

| ui32Base | is the base address of the UART port. |

| pui32TxLevel | is a pointer to storage for the transmit FIFO level, returned as one of: |

| pui32RxLevel | is a pointer to storage for the receive FIFO level, returned as one of: |

|

inlinestatic |

Sets the FIFO level at which interrupts are generated.

This function sets the FIFO level at which transmit and receive interrupts are generated.

| ui32Base | is the base address of the UART port. |

| ui32TxLevel | is the transmit FIFO interrupt level, specified as one of: |

| ui32RxLevel | is the receive FIFO interrupt level, specified as one of: |

|

inlinestatic |

Disables hardware flow control for both CTS and RTS.

Hardware flow control is disabled by default.

| ui32Base | is the base address of the UART port. |

|

inlinestatic |

Enables hardware flow control for both CTS and RTS.

Hardware flow control is disabled by default.

| ui32Base | is the base address of the UART port. |

|

inlinestatic |

Clears UART interrupt sources.

The specified UART interrupt sources are cleared, so that they no longer assert. This function must be called in the interrupt handler to keep the interrupt from being recognized again immediately upon exit.

| ui32Base | is the base address of the UART port. |

| ui32IntFlags | is a bit mask of the interrupt sources to be cleared.

|

|

inlinestatic |

Disables individual UART interrupt sources.

This function disables the indicated UART interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

| ui32Base | is the base address of the UART port. |

| ui32IntFlags | is the bit mask of the interrupt sources to be disabled.

|

|

inlinestatic |

Enables individual UART interrupt sources.

This function enables the indicated UART interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

| ui32Base | is the base address of the UART port. |

| ui32IntFlags | is the bit mask of the interrupt sources to be enabled. The parameter is the bitwise OR of any of the following:

|

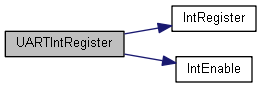

| void UARTIntRegister | ( | uint32_t | ui32Base, |

| void(*)(void) | pfnHandler | ||

| ) |

Registers an interrupt handler for a UART interrupt in the dynamic interrupt table.

This function registers a function as the interrupt handler for a specific interrupt and enables the corresponding interrupt in the interrupt controller.

Specific UART interrupts must be enabled via UARTIntEnable(). It is the interrupt handler's responsibility to clear the interrupt source.

| ui32Base | is the base address of the UART module. |

| pfnHandler | is a pointer to the function to be called when the UART interrupt occurs. |

|

inlinestatic |

Gets the current interrupt status.

This function returns the interrupt status for the specified UART. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

| ui32Base | is the base address of the UART port. |

| bMasked | selects either raw or masked interrupt.

|

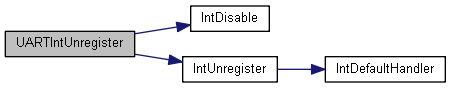

| void UARTIntUnregister | ( | uint32_t | ui32Base | ) |

Unregisters an interrupt handler for a UART interrupt in the dynamic interrupt table.

This function does the actual unregistering of the interrupt handler. It clears the handler to be called when a UART interrupt occurs. This function also masks off the interrupt in the interrupt controller so that the interrupt handler no longer is called.

| ui32Base | is the base address of the UART module. |

|

inlinestatic |

Gets the type of parity currently being used.

This function gets the type of parity used for transmitting data and expected when receiving data.

| ui32Base | is the base address of the UART port. |

|

inlinestatic |

Sets the type of parity.

This function sets the type of parity to use for transmitting and expect when receiving.

| ui32Base | is the base address of the UART port. |

| ui32Parity | specifies the type of parity to use. The last two allow direct control of the parity bit; it is always either one or zero based on the mode. |

|

inlinestatic |

Clears all reported receiver errors.

This function is used to clear all receiver error conditions reported via UARTRxErrorGet(). If using the overrun, framing error, parity error or break interrupts, this function must be called after clearing the interrupt to ensure that later errors of the same type trigger another interrupt.

| ui32Base | is the base address of the UART port. |

|

inlinestatic |

Gets current receiver errors.

This function returns the current state of each of the 4 receiver error sources. The returned errors are equivalent to the four error bits returned via the previous call to UARTCharGet() or UARTCharGetNonBlocking() with the exception that the overrun error is set immediately the overrun occurs rather than when a character is next read.

| ui32Base | is the base address of the UART port. |

|

inlinestatic |

Determines if there is any space in the transmit FIFO.

This function returns a flag indicating whether or not there is space available in the transmit FIFO.

| ui32Base | is the base address of the UART port. |

true : There is space available in the transmit FIFO.false : There is no space available in the transmit FIFO. | #define UART_BUSY 0x00000001 |

Referenced by UARTBusy().

| #define UART_CONFIG_PAR_EVEN 0x00000006 |

Referenced by UARTParityModeSet().

| #define UART_CONFIG_PAR_MASK 0x00000086 |

| #define UART_CONFIG_PAR_NONE 0x00000000 |

Referenced by UARTParityModeSet().

| #define UART_CONFIG_PAR_ODD 0x00000002 |

Referenced by UARTParityModeSet().

| #define UART_CONFIG_PAR_ONE 0x00000082 |

Referenced by UARTParityModeSet().

| #define UART_CONFIG_PAR_ZERO 0x00000086 |

Referenced by UARTParityModeSet().

| #define UART_CONFIG_STOP_MASK 0x00000008 |

| #define UART_CONFIG_STOP_ONE 0x00000000 |

| #define UART_CONFIG_STOP_TWO 0x00000008 |

| #define UART_CONFIG_WLEN_5 0x00000000 |

| #define UART_CONFIG_WLEN_6 0x00000020 |

| #define UART_CONFIG_WLEN_7 0x00000040 |

| #define UART_CONFIG_WLEN_8 0x00000060 |

| #define UART_CONFIG_WLEN_MASK 0x00000060 |

| #define UART_DMA_ERR_RXSTOP 0x00000004 |

| #define UART_DMA_RX 0x00000001 |

| #define UART_DMA_TX 0x00000002 |

| #define UART_FIFO_RX1_8 0x00000000 |

Referenced by UARTFIFOLevelSet().

| #define UART_FIFO_RX2_8 0x00000008 |

Referenced by UARTFIFOLevelSet().

| #define UART_FIFO_RX4_8 0x00000010 |

Referenced by UARTFIFOLevelSet().

| #define UART_FIFO_RX6_8 0x00000018 |

Referenced by UARTFIFOLevelSet().

| #define UART_FIFO_RX7_8 0x00000020 |

Referenced by UARTFIFOLevelSet().

| #define UART_FIFO_TX1_8 0x00000000 |

Referenced by UARTFIFOLevelSet().

| #define UART_FIFO_TX2_8 0x00000001 |

Referenced by UARTFIFOLevelSet().

| #define UART_FIFO_TX4_8 0x00000002 |

Referenced by UARTFIFOLevelSet().

| #define UART_FIFO_TX6_8 0x00000003 |

Referenced by UARTFIFOLevelSet().

| #define UART_FIFO_TX7_8 0x00000004 |

Referenced by UARTFIFOLevelSet().

| #define UART_IDLE 0x00000000 |

Referenced by UARTBusy().

| #define UART_INT_BE ( UART_IMSC_BEIM ) |

| #define UART_INT_CTS ( UART_IMSC_CTSMIM ) |

| #define UART_INT_FE ( UART_IMSC_FEIM ) |

| #define UART_INT_OE ( UART_IMSC_OEIM ) |

| #define UART_INT_PE ( UART_IMSC_PEIM ) |

| #define UART_INT_RT ( UART_IMSC_RTIM ) |

| #define UART_INT_RX ( UART_IMSC_RXIM ) |

| #define UART_INT_TX ( UART_IMSC_TXIM ) |

| #define UART_RXERROR_BREAK 0x00000004 |

| #define UART_RXERROR_FRAMING 0x00000001 |

| #define UART_RXERROR_OVERRUN 0x00000008 |

| #define UART_RXERROR_PARITY 0x00000002 |