Data Structures | |

| struct | rfTrim_t |

Functions | |

| static void | RFCClockEnable (void) |

| Enable the RF core clocks. More... | |

| static void | RFCClockDisable (void) |

| Disable the RF core clocks. More... | |

| static void | RFCCpeIntClear (uint32_t ui32Mask) |

| Clear HW interrupt flags. More... | |

| static void | RFCHwIntClear (uint32_t ui32Mask) |

| Clear CPE interrupt flags. More... | |

| static void | RFCCpe0IntSelect (uint32_t ui32Mask) |

| Select interrupt sources to CPE0 (assign to INT_RFC_CPE_0 interrupt vector). More... | |

| static void | RFCCpe1IntSelect (uint32_t ui32Mask) |

| Select interrupt sources to CPE1 (assign to INT_RFC_CPE_1 interrupt vector). More... | |

| static void | RFCCpeIntEnable (uint32_t ui32Mask) |

| Enable CPEx interrupt sources. More... | |

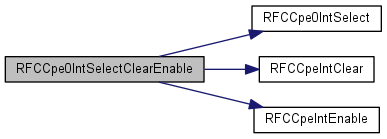

| static void | RFCCpe0IntSelectClearEnable (uint32_t ui32Mask) |

| Select, clear, and enable interrupt sources to CPE0. More... | |

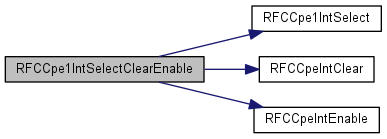

| static void | RFCCpe1IntSelectClearEnable (uint32_t ui32Mask) |

| Select, clear, and enable interrupt sources to CPE1. More... | |

| static void | RFCHwIntEnable (uint32_t ui32Mask) |

| Enable HW interrupt sources. More... | |

| static void | RFCCpeIntDisable (uint32_t ui32Mask) |

| Disable CPE interrupt sources. More... | |

| static void | RFCHwIntDisable (uint32_t ui32Mask) |

| Disable HW interrupt sources. More... | |

| uint32_t | RFCCpeIntGetAndClear (uint32_t ui32Mask) |

| Get and clear CPE interrupt flags. More... | |

| static void | RFCAckIntClear (void) |

| Clear ACK interrupt flag. More... | |

| uint32_t | RFCDoorbellSendTo (uint32_t pOp) |

| Send a radio operation to the doorbell and wait for an acknowledgment. More... | |

| void | RFCSynthPowerDown (void) |

| This function implements a fast way to turn off the synthesizer. More... | |

| void | RFCCpePatchReset (void) |

| Reset previously patched CPE RAM to a state where it can be patched again. More... | |

| uint8_t | RFCOverrideSearch (const uint32_t *pOverride, const uint32_t pattern, const uint32_t mask, const uint8_t searchDepth) |

| uint8_t | RFCOverrideUpdate (rfc_radioOp_t *pOpSetup, uint32_t *pParams) |

| Function to update override list. More... | |

| uint32_t | RFCHwIntGetAndClear (uint32_t ui32Mask) |

| Get and clear HW interrupt flags. More... | |

| void | RFCRfTrimRead (rfc_radioOp_t *pOpSetup, rfTrim_t *rfTrim) |

| Get the type of currently selected PA. More... | |

| void | RFCRfTrimSet (rfTrim_t *rfTrim) |

| Write preloaded RF trim values directly into CPE. More... | |

| uint8_t | RFCRTrim (rfc_radioOp_t *pOpSetup) |

| Check Override RTrim vs FCFG RTrim. More... | |

| void | RFCAdi3VcoLdoVoltageMode (bool bEnable) |

| Function to set VCOLDO reference to voltage mode. More... | |

|

inlinestatic |

| void RFCAdi3VcoLdoVoltageMode | ( | bool | bEnable | ) |

|

inlinestatic |

Disable the RF core clocks.

As soon as the RF core is started it will handle clock control autonomously. No check should be performed to check the clocks. Instead the radio can be ping'ed through the command interface.

When disabling clocks it is the programmers responsibility that the RF core clocks are safely gated. I.e. the RF core should be safely 'parked'.

|

inlinestatic |

Enable the RF core clocks.

As soon as the RF core is started it will handle clock control autonomously. No check should be performed to check the clocks. Instead the radio can be ping'ed through the command interface.

|

inlinestatic |

Select interrupt sources to CPE0 (assign to INT_RFC_CPE_0 interrupt vector).

Referenced by RFCCpe0IntSelectClearEnable().

|

inlinestatic |

Select, clear, and enable interrupt sources to CPE0.

|

inlinestatic |

Select interrupt sources to CPE1 (assign to INT_RFC_CPE_1 interrupt vector).

Referenced by RFCCpe1IntSelectClearEnable().

|

inlinestatic |

Select, clear, and enable interrupt sources to CPE1.

|

inlinestatic |

Clear HW interrupt flags.

Referenced by RFCCpe0IntSelectClearEnable(), RFCCpe1IntSelectClearEnable(), and RFCCpeIntGetAndClear().

|

inlinestatic |

Disable CPE interrupt sources.

|

inlinestatic |

Enable CPEx interrupt sources.

Referenced by RFCCpe0IntSelectClearEnable(), and RFCCpe1IntSelectClearEnable().

| uint32_t RFCCpeIntGetAndClear | ( | uint32_t | ui32Mask | ) |

Get and clear CPE interrupt flags.

| void RFCCpePatchReset | ( | void | ) |

Reset previously patched CPE RAM to a state where it can be patched again.

| uint32_t RFCDoorbellSendTo | ( | uint32_t | pOp | ) |

Send a radio operation to the doorbell and wait for an acknowledgment.

|

inlinestatic |

|

inlinestatic |

Disable HW interrupt sources.

|

inlinestatic |

Enable HW interrupt sources.

| uint32_t RFCHwIntGetAndClear | ( | uint32_t | ui32Mask | ) |

Get and clear HW interrupt flags.

| uint8_t RFCOverrideSearch | ( | const uint32_t * | pOverride, |

| const uint32_t | pattern, | ||

| const uint32_t | mask, | ||

| const uint8_t | searchDepth | ||

| ) |

Referenced by RFCOverrideUpdate().

| uint8_t RFCOverrideUpdate | ( | rfc_radioOp_t * | pOpSetup, |

| uint32_t * | pParams | ||

| ) |

Function to update override list.

| void RFCRfTrimRead | ( | rfc_radioOp_t * | pOpSetup, |

| rfTrim_t * | rfTrim | ||

| ) |

Get the type of currently selected PA.

Read RF trim from flash using CM3.

| void RFCRfTrimSet | ( | rfTrim_t * | rfTrim | ) |

| uint8_t RFCRTrim | ( | rfc_radioOp_t * | pOpSetup | ) |

| void RFCSynthPowerDown | ( | void | ) |

This function implements a fast way to turn off the synthesizer.

| #define RFC_MAX_SEARCH_DEPTH 5 |

Referenced by RFCOverrideUpdate().