3.1. Board Support¶

3.1.1. Introduction¶

Board library contains a set of general initialization and setup functions that are board-specific. This component includes libraries for boards supported in the Processor SDK release. Refer to the package content for the list of supported boards.Board component also includes diagnostic software. Refer to Processor SDK RTOS DIAG for additional details on available diagnostic examples.

3.1.1.1. Board APIs¶

The Board_init() API supports initialization of PLL, peripheral clocks, external DDR memory, pinmux and IO Delay configurations. API Reference for application:

#. include <ti/board/board.h>

Example API pseudo code for Board_init() is as follows:

/* Setting up for pinmux and uart */

Board_STATUS ret;

Board_initCfg boardCfg;

boardCfg = BOARD_INIT_MODULE_CLOCK \| BOARD_INIT_PINMUX_CONFIG \|

BOARD_INIT_UART_STDIO;

ret = Board_init(boardCfg);

3.1.1.2. LLD Dependencies¶

3.1.1.2.1. I2C¶

Application need to configure BOARD_INIT_MODULE_CLOCK option to have I2C operational. I2C is used to read EEPROM data. An I2C handle will be opened in polling mode, and closed after the board ID data is retrieved from EEPROM using Board_getIDInfo() API.

For DRA7xx EVMs, I2C is also used to configure various I/O expanders and board muxes to enable PDK examples to function properly on the EVM. The I2C handles are opened in polling mode and closed after the board mux initialization has completed.

3.1.1.2.2. UART¶

Application need to configure Board_init() with the BOARD_INIT_UART_STDIO option to use the UART stdio API.

After Board_init() completes, application can invoke UART stdio functions such as UART_printf, UART_scanFmt, and etc.

3.1.1.2.3. SCICLIENT¶

AM65xx Board library uses sciclient APIs for configuring the PLL clocks.

3.1.2. Application Integration for AM5x/DRA7xx¶

When configuring pinmux with IO Delay settings for AM5x and DRA7xx boards, there is a hard restriction: the code/data/stack during the IO Delay setup must be within local internal memory. Refer to SOC TRM for additional information.

The board library specifies two sections for users to define for the sole purpose of meeting this requirement. They are: BOARD_IO_DELAY_CODE and BOARD_IO_DELAY_DATA. Below are examples of how to specify these section into the local memory, OCMC_RAM1:

In baremetal case with a linker cmd file:

BOARD_IO_DELAY_CODE : {

. = ALIGN(4);

*(BOARD_IO_DELAY_CODE*)

} > OCMC_RAM1

BOARD_IO_DELAY_DATA : {

. = ALIGN(4);

*(BOARD_IO_DELAY_DATA*)

} > OCMC_RAM1

In a CCS RTSC project with .cfg file:

Program.sectMap["BOARD_IO_DELAY_DATA"] = "OCMC_RAM1";

Program.sectMap["BOARD_IO_DELAY_CODE"] = "OCMC_RAM1";

3.1.2.1. Considerations for DRA7xx devices¶

When integrating the board library in applications on DRA7xx, these code/data sections will likely overlap and conflict with the code/data sections used by the Secondary Boot Loader (SBL) as both modules will assume full access to OCMC_RAM1. Also, as the SBL performs identical configuration using the common pad config data structures, the pinmux request made by an application will be redundant. Therefore, it is advised that the pinmux API be used only when loading the application via CCS. When loading via SBL, there are three options available for handling this conflict:

- Place the BOARD_IO_DELAY_DATA/BOARD_IO_DELAY_CODE sections to another internal memory location. The Board library will check to see if the board code/data/stack are located in internal memory before executing the sequence. If another internal memory section is available for placement (e.g. L2SRAM, OCMC_RAM2), then it is acceptable to place the sections in these locations. The Board init sequence will proceed as expected.

- Place the BOARD_IO_DELAY_DATA/BOARD_IO_DELAY_CODE sections into external memory. The pinmux subroutine in the Board library checks for code/data/stack placement and will fail if it detects that they reside in DDR and return before performing the configuration. The failure will not affect any other Board init requests as other flags are treated orthogonally.

- Remove the BOARD_IO_DELAY_DATA/BOARD_IO_DELAY_CODE sections. This is

the preferred solution as it removes redundant code from executing

and will optimize code/data size and load speed. In order to remove

these sections, two modifications are required:

- Place BOARD_IO_DELAY_DATA/BOARD_IO_DELAY_CODE input sections into an output Dummy Section (DSECT). DSECTs are a Special Linker Section Type which are relocated for linker resolution but otherwise do not allocate space to a memory map, place sections in the output file, or ever get loaded to the target. In order to place these sections into DSECTS, modify the placement as follows:

Replace:

Program.sectMap["BOARD_IO_DELAY_DATA"] =

"OCMC_RAM1"; Program.sectMap["BOARD_IO_DELAY_CODE"] = "OCMC_RAM1";

With:

Program.sectMap["BOARD_IO_DELAY_DATA"] = new

Program.SectionSpec(); Program.sectMap["BOARD_IO_DELAY_CODE"] = new

Program.SectionSpec(); Program.sectMap["BOARD_IO_DELAY_DATA"].type =

"DSECT"; Program.sectMap["BOARD_IO_DELAY_CODE"].type = "DSECT";

- Remove the BOARD_INIT_PINMUX_CONFIG flag from the call to Board_init. Since the BOARD_IO_DELAY_DATA/BOARD_IO_DELAY_CODE sections no longer actually exist, we must instruct the application that it is no longer safe to call the routines and access the data. Otherwise, the CPU will branch to and access undefined memory and cause various exceptions

3.1.3. Custom Board Addition¶

This section provides the guidelines for creating a custom board library.

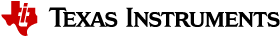

Below image shows the recommended sequence to be followed while porting processor SDK to custom board.

3.1.3.1. Board Configurations¶

Board library supports different SoC and HW board specific configuration functions. Below table shows configurations supported by board library across different platforms.

| Board Configuration | Description | References | AM65xx | AM57xx | AM437x | AM335x | K2G | K2-E/H/K/L |

|---|---|---|---|---|---|---|---|---|

| Pinmux | Configures pinmux for interfaces on the HW board. | Pinmux Tool | x | x | x | x | x | |

| SoC Clock Settings | Enables power domains and clocks for SoC peripherals | Clock Tree Tool | x | x | x | x | x | x |

| DDR Configuration | Configures DDR/EMIF controller and DDR timing parameters. | EMIF Tools Appnote | x | x | x | x | ||

| PLL Configuration | Configures PLL modules to generate various clocks used by the SoC. | NA | x | x | x | x | ||

| Ethernet Configuration | Configures Ethernet PHYs on the board. | NA | x | x | x | x | x | |

| IO Instances | Defines IO instances for HW interfaces. | NA | x | x | x | x | x | x |

| Board Detection | EEPROM board ID for board detection. | NA | x | x | x | x | x | |

| Board Flash APIs | Provides Common APIs for accessing flash devices. | NA | x | x | x | x | x | |

| SerDes Configuration | Configures SerDes interface internal muxing and basic setup. | NA | x |

Adding custom board library can follow two approaches as mentioned below

3.1.3.2. Creating Board Configurations¶

Before updating the board library with configurations for custom board, it is recommended to use GEL file and CCS for validating the configurations. Follow the steps mentioned below

- Update the SoC clock configurations in the GEL file. TI provides Clock Tree Tool to simulate the device clocks.

- Update the PLL clock configurations in GEL file if custom board uses a different input clock than the eval platform and/or needs different clock outputs.

- Update DDR PHY and timing configurations for custom board. Refer the guidelines described in Application Report on EMIF Tools

- After GEL file update is complete, connect to custom board using JTAG, run the GEL script to apply the modified configurations and verify the configured values. Load and run simple hello world example out of SoC internal memory and DDR memory.

3.1.3.3. Updating Board Configurations¶

Steps for updating the board library configurations for a custom board is described in this section. Updating some of the configurations may need additional steps based on the platform. Refer Platform Specific Configuration section for more details.

3.1.3.3.1. Pinmux¶

When the BOARD_INIT_PINMUX_CONFIG option is specified, the Board_init() API configures the pinmux for the board. If applicable, it will also configure IO delay values for those device pads, which ensures correct IO timings are met along with the pinmux settings. Refer SOC TRM for additional details.

The pinmux data to be configured is generated by the TI pinmux tool. Refer to TI PinMux Tool for more information.

Once the pinmux selection is done, Copy the pinmux tool generated files to your custom board library implementation folder.

Refer Platform Specific Configuration section for more details on the files generated by pinmux tool for different platforms.

3.1.3.3.2. SoC Clock Settings¶

The core clocks and module clocks used on the custom board library may vary based on the power requirements and external components used on the boards.

<Board>_clock.c: Defines functions and structures for configuring the clock and power modules. Update this file based on the data from clock tree tool and GEL file validation.

3.1.3.3.3. DDR Configuration¶

The board library has the correct DDR initialization sequence to initialize the DDR memory on your board. You may need to make changes to the AC timings, hardware leveling, and DDR PHY configuration, some or all of which may be different than the TI supported platforms. GEL file can be used to verify the settings in CCS before modifying the source in the board library.

<Board>_ddr.c: Defines functions and structures for configuring the DDR module. Update this file based on the DDR timing parameters specific to custom board.

3.1.3.3.4. PLL Configuration¶

The SOC board library in the PDK configures the SOC PLL and module clock settings to the nominal settings required to be used with the TI evaluation platform. If you want to use different clock settings due to power consideration, or if you are using a variant of the device that needs to be clocked differently, you can enter the PLL and clock settings in the board library. All of the PLL and module clock settings are consolidated in the following files:

- <Board>.c: Contains calls related to all board-level initialization. <Board> refers to the evaluation platform (For example, evmam335x)

- <Board>_pll.c: Defines the Board_PLLInit() function that configures the dividers and multipliers for the clock tree.

3.1.3.3.5. Ethernet Configuration¶

The custom board may have external components (flash devices, Ethernet PHY, etc.) that are different from the components populated on the TI-supported EVM. These components and their support files need to be added to the pdk_xx_xx_xx_xx/packages/ti/board/src/<customBoardName>/device path and linked as part of the board library build.

3.1.3.3.6. IO Instances¶

If your custom board uses an IO instance different from the TI-supported board, the instance needs to be modified in the Pin Mux setup as well as in the board_cfg.h file in pdk_xx_xx_xx_xx/packages/ti/board/src/<customBoardName>/include

3.1.3.3.6.1. Board Detection¶

- TI defined board detect mechanism using structure stored in I2C EEPROM

- Board Lib APIs read and write Board ID to EEPROM on I2C address 0x50

- Application boards, if available, will have their own EEPROM with board information

- Structure typically defines:

Board ID (IDK vs GP EVM vs custom)

Revision number (board revision to address board level issues)

Serial Number (internal tracking)

MAC ID (Custom MAC ID use)

Note

Board detection is TI defined mechanism to detect evaluation platform details. This needs to be removed/replicated from board based on customer board implementation. In case board detect mechanism is not used in custom board, check for the Board_getIDInfo() API calls and make necessary changes in the code to avoid dependencies on board detect mechanism.

3.1.3.3.6.2. Board Flash APIs¶

Board library includes a dedicated flash library to abstract the HW flash interface access using a standard set of APIs. In case custom board uses flash devices that are different from eval platform, update to board flash APIs is required. Check the board flash library available at <PDK_INSTALL_PATH>/packages/ti/board/src/flash and make changes required for custom board as needed.

3.1.3.4. Platform Specific Configurations¶

3.1.3.4.1. AM65xx¶

3.1.3.4.1.1. Pinmux¶

- Follow below steps to update pinmux configuration for custom board on AM65xx platforms.

- Download the pinmux files <Platform Name>pinmux.h and <Platform Name>_pinmux_data.c generated by pinmux tool

- Copy the files to custom board folder and rename them to match with board name if needed.

- Rebuild the board library with new pinmux configurations

3.1.3.4.1.2. SerDes Configuration¶

AM65xx board library includes SerDes module which configures the SerDes interface internal pinmux to route PCIe, USB and SGMII interfaces to different personality cards. If custom board uses similar design, SerDes configurations can be reused. Otherwise this configuration can be ignored.

3.1.3.4.2. AM57xx¶

3.1.3.4.2.1. Pinmux¶

Pinmux tool output for AM57xx platform includes IO delay information. Below are the files generated by pinmux tool:

- boardPadDelay.h: Includes the prototypes of all structures and functions used by pinmux functions

- boardPadDelayInit.c: Includes the pinmux pad config data for all device pads along with values used to compute Manual/Virtual mode values.This data is used to configure pinmux during board initialization.

- boardPadDelayTune.h: This file includes the compile time macros used to select the Timing modes to be configured for modules during board Initialization.

- boardPadDelayDevice.c: This file includes the pinmuxdata for runtime pinmux configuration of the MMC module.

Copy the above listed files generated by pinmux tool to custom board folder and rebuild the board library with updated pinmux configurations.

3.1.3.4.3. AM335x/AM437x¶

3.1.3.4.3.1. Pinmux¶

Follow below steps to update pinmux configuration for custom board on AM335x/AM437x platforms.

- Download the pinmux files <Platform Name>pinmux.h and <Platform Name>_pinmux_data.c generated by pinmux tool

- At the bottom of <Platform Name>pinmux.h change extern pinmuxBoardCfg_t g<Platform Name>PinmuxData[]; to extern pinmuxBoardCfg_t g<Custom Board Name>PinmuxData[];

- Change <Platform Name>_pinmux_data.c to <Platform Name>_<Custom Board Name>pinmux_data.c

- Change g<Platform Name>PinmuxData to g<Custom Board Name>PinmuxData at the end of the file in <Platform Name>_<Custom Board Name>pinmux_data.c

- The last step is to invoke the PinMuxModuleConfig in the file <BoardName>_pinmux.c that is found at <PDK_INSTALL_PATH>packagestiboardsrc<BoardName>. For Example to add three instances of UART in the pinmux setup, users can add :

/* UART */

status = PINMUXModuleConfig(CHIPDB_MOD_ID_UART, 0U, NULL);

status = PINMUXModuleConfig(CHIPDB_MOD_ID_UART, 1U, NULL);

status = PINMUXModuleConfig(CHIPDB_MOD_ID_UART, 4U, NULL);

3.1.3.4.4. K2G¶

3.1.3.4.4.1. Pinmux¶

- Follow below steps to update pinmux configuration for custom board on K2G platforms.

- Download the pinmux files <Platform Name>pinmux.h and <Platform Name>_pinmux_data.c generated by pinmux tool

- Copy the files to custom board folder and rename them to match with board name if needed.

- Rebuild the board library with new pinmux configurations

3.1.3.5. Custom Board Validation¶

Validate the basic functionality of custom board using hardware diagnostics before bringing-up RTOS applications or Linux. Hardware diagnostics help verify the functionality of on-board peripherals and external interfaces of each board.

Refer Board Diagnostics section for more details on the diagnostic tests supported as part of processor SDK.

Below are the recommended diagnostic tests which can be validated on custom board

- External memory (DDR): DDR timing and leveling setting can be checked out using mem_test

- Debug UART: Debug UART pin functionality

- Boot Media: Validate functionality of SD/MMC, OSPIor any other boot interfaces

- Board ID/EEPROM test: Recommend checking out/writing ID on personality EEPROM. This also checkout I2C pin functionality

- Ethernet PHY: Ethernet diagnostics tests read PHY configuration over MDIO and check for Link up status. Good first step before bringing up any network stack

3.1.3.6. Creating Board Library with Custom Name¶

3.1.3.6.1. Instructions to add custom Board to the PDK build¶

Follow below steps for creating board library with custom name. AM572x platform is used as reference in the examples wherever needed.

Step 1: Creating new directory for custom board library

In <PDK_INSTALL_PATH>/packages/ti/board/src, Create new directory myCustomBoard and copy files from existing board library package which closely matches your custom board design.

Step 2: Updating names and makefile inside the customBoard package

In <PDK_INSTALL_PATH>/packages/ti/board/src/myCustomBoard, Rename file src_files_<Board>.mk to src_files_myCustomBoard.mk. This file will need a bit of work depending on what elements of board you need for your platform.

Step 3: Adding MACRO based inclusion of updated board_cfg.h corresponding to custom Board

In packages/ti/board/board_cfg.h, add the lines pointing to board_cfg.h file in your customBoard package so that updated peripheral instances and board specific defines can be picked up

#if defined (myCustomBoard)

#include <ti/board/src/myCustomBoard/include/board_cfg.h>

#endif

Step 4: Update top level board package makefile to include build for customBoard Library The makefile is used to include all relevant make files for including Low level driver(LLD), source files relevant to board and the common board.c file

- In packages/ti/board/build/makefile.mk, add board.c to the customBoard build:

ifeq ($(BOARD),$(filter $(BOARD),evmAM335x icev2AM335x skAM335x bbbAM335x evmAM437x idkAM437x skAM437x myCustomBoard evmAM572x idkAM571x idkAM572x evmK2H evmK2K evmK2E evmK2L evmK2G iceK2G evmC6678 evmC6657))

# Common source files across all platforms and cores

SRCS_COMMON += board.c

endif

- Add board library source files and LLD files to the customBoard build

In packages/ti/board/build/makefile.mk, change

ifeq ($(BOARD),$(filter $(BOARD), evmAM572x idkAM571x idkAM572x))

include $(PDK_BOARD_COMP_PATH)/src/$(BOARD)/src_files_$(BOARD).mk

include $(PDK_BOARD_COMP_PATH)/src/src_files_lld.mk

endif

to

ifeq ($(BOARD),$(filter $(BOARD), myCustomBoard evmAM572x idkAM571x idkAM572x))

include $(PDK_BOARD_COMP_PATH)/src/$(BOARD)/src_files_$(BOARD).mk

include $(PDK_BOARD_COMP_PATH)/src/src_files_lld.mk

endif

Step 5: Update Global makerules

build_config.mk defines the global CFLAGS used to compile different PDK components. Add the following line in the BOARD Specific configurations.

CFLAGS_GLOBAL_myCustomBoard = -DSOC_AM572x -DmyCustomBoard=myCustomBoard

The SOC_AM572x macro ensures that the CSL applicable to this SOC will be included in the build. Use the SoC name that corresponds to the platform of your custom board.

Optional step to update RTSC platform definition If you have a custom RTSC platform definition for your custom board that updates the memory and platform configuration using RTSC Tool then you need to update the platform.mk file that associates the RTSC platform with the corresponding board library

In packages/ti/build/makerules/platform.mk, add the following lines:

ifeq ($(BOARD),$(filter $(BOARD), evmAM572x))

PLATFORM_XDC = "ti.platforms.evmAM572X"

endif

ifeq ($(BOARD),$(filter $(BOARD), myCustomBoard))

PLATFORM_XDC = "evmAM572XCustom"

endif

Note

The SYSBIOS platforms follow the convention to consolidate all platform definitions under SYSBIOS_INSTALL_PATH/packages/ti/platforms/* hence the convention ti.platorms.<platformName> but for custom platform, users are not required to follow this convention.

Step 6: Update source files corresponding to drivers used in board library. src_files_lld.mk file adds source files corresponding to LLD drivers used in the board library. Usually most boards utilitize control driver like I2C (for programming the PMIC or reading EEPROM), UART drivers (for IO) and boot media drivers like (SPI/QSPI, MMC or NAND). In the example below, we assume that the custom Board library has dependency on I2C, SPI and UART LLD drivers. Since the LLD drivers will be linked to the application along with board library, board library only needs <driver>_soc.c corresponding to SOC used on the custom Board.

In packages/ti/board/src/src_files_lld.mk, add the following lines:

ifeq ($(BOARD),$(filter $(BOARD), myCustomBoard))

SRCDIR += $(PDK_INSTALL_PATH)/ti/drv/i2c/soc/am572x \

$(PDK_INSTALL_PATH)/ti/drv/uart/soc/am572x \

$(PDK_INSTALL_PATH)/ti/drv/spi/soc/am572x

INCDIR += $(PDK_INSTALL_PATH)/ti/drv/i2c/soc/am572x \

$(PDK_INSTALL_PATH)/ti/drv/uart/soc/am572x \

$(PDK_INSTALL_PATH)/ti/drv/spi/soc/am572x

# Common source files across all platforms and cores

SRCS_COMMON += I2C_soc.c UART_soc.c SPI_soc.c

endif

Note

For all LLD drivers linked to the board library you need to include corresponding <drv>_soc.c file. For example if you include GPIO driver for setting board mux then GPIO_soc.c needs to be added to LLD source files.

Step 7: Add custom Board to BOARDLIST and update CORELIST

In packages/ti/board/board_component.mk, modify the build to add your custom board and specify the cores for which you want to build the board library. Example to build board library for only A15 and C66x cores, limit the build by specify only a15_0 and C66x in the CORELIST

board_lib_BOARDLIST = myCustomBoard evmAM335x icev2AM335x skAM335x bbbAM335x evmAM437x idkAM437x skAM437x evmAM572x idkAM571x idkAM572x evmK2H evmK2K evmK2E evmK2L evmK2G iceK2G \

#board_lib_am572x_CORELIST = c66x a15_0 ipu1_0

board_lib_am572x_CORELIST = a15_0 c66x

Step 8: Update .bld files for XDCTOOL based build steps.

Make corresponding changes in packages/ti/board/config.bld, by adding the following lines:

var myCustomBoard = {

name: "myCustomBoard",

ccOpts: "-DmyCustomBoard -DSOC_AM572x",

targets: [C66LE,A15LE ]

}

var boards = [ evmAM335x, icev2AM335x, skAM335x, bbbAM335x, evmAM437x, idkAM437x, skAM437x, myCustomBoard, evmAM572x, idkAM571x, idkAM572x, evmK2H, evmK2K, evmK2E, evmK2L, evmK2G, evmC6678, evmC6657 ];

Also, in packages/ti/board/package.bld, add the following line:

Pkg.otherFiles[Pkg.otherFiles.length++] = "src/myCustomBoard/src_files_myCustomBoard.mk";

Step 9: Setup Top level PDK build files to add the Custom board to setup environment.

Final setup involves updating the top level setup file for PDK package to update to setup the build environment to include the custom Board in setup. This can be done by commenting out the top line and adding in the bottom line in <PDK_INSTALL_PATH>/packages/Rules.make:

#export LIMIT_BOARDS ?= evmAM572x idkAM571x idkAM572x

export LIMIT_BOARDS ?= myCustomBoard

Alternative: Invoke the build using command line options to limit the build to specific board, specific SOC and specific CORE. For example, if you want to build the A15 version of board library for AM572x EVM, you can invoke the build using:

gmake board_lib LIMIT_SOCS=am572x LIMIT_BOARDS=myCustomBoard LIMIT_CORES=a15_0

Step 10: Building the custom board with the updated settings

To build package change directory to <SDK_INSTALL_PATH>/<PDK_INSTALL_PATH>/packages, first run pdksetupenv.bat

To make just the board library: gmake board_lib

3.1.3.6.2. Additional steps for AM335x/AM437x users¶

Note

Currently the AM335x and AM437x board libraries re-use the board support that was used in legacy starterware software. AM335x and AM437x users will need to additionally modify build files in starterware to build their custom board library.

3.2. Diagnostics¶

3.2.1. Overview¶

The Processor SDK RTOS Diagnostic package is designed to be a set of baremetal tests to run on a given board to provide data path continuity testing on peripherals. For K2H/K2E/K2L/C66x devices, this functionality is provided by POST.

3.2.2. Building the Examples¶

3.2.2.1. Pre-requisites to Building¶

- Set your environment using pdksetupenv.bat or pdksetupenv.sh. The diagnostic application uses the same environment variables as the board library build. Refer to the Processor SDK RTOS Building page for information on setting up your build environment.

- You will need the following libraries built:

- Board

- UART

- GPIO

- I2C

- SPI

- CSL

- ICSS

- PRUSS

- MMCSD

- EMAC

- USB

- UDMA

- SCICLIENT

(Note: not every library is used for every application, and these libraries should come pre-built with any fresh installation of the Processor SDK)

3.2.2.2. Compiling the Diagnostic Applications¶

To build the diagnostic examples:

- cd <PDK>/packages/ti/board/diag

- make <BOARD>

This will make the diagnostic applications for a specific $BOARD. Output files will be located in: <PDK>/packages/ti/board/bin/<BOARD>

3.2.2.3. Creating the SD Card Loadable Files¶

For converting the compiled .out files to a format loadable by TI’s Secondary Boot Loader (SBL), you must follow these two steps:

- out2rprc.exe [.out file] [rprc output]

- MulticoreImageGen.exe LE 55 [output name] 0 [rprc output]

Out2rprc.exe and MulticoreImageGen.exe are tools supplied by TI and can be located in the <PDK>/packages/ti/boot/sbl/tools folder. “rprc output” can be any spare name of your choosing. “output name” can also be any name of your choosing. For diagnostic applications, your final output name must have the keyword “TEST” in it. You will have to do this process for every .out application you wish to be loadable on the SD card.

Alternatively, there is also a make target to automate this process:

- cd <PDK>/packages/ti/board/diag

- make <BOARD>_sd

This will compile all the applications for a specific $BOARD, and also create the SD card loadable files. The output files will be located in: <PDK>/packages/ti/board/bin/<BOARD>/sd. Note that the framework application is named “app” to allow it to be the default application to be loaded by the SBL.

Note

Diagnostic tests on AM65xx platform supports A53 and R5 cores. A53 binary path: <PDK>/packages/ti/board/bin/<BOARD>/sd/armv8. R5 binary path: <PDK>/packages/ti/board/bin/<BOARD>/sd/armv7.

3.2.2.4. Creating the SPI Flash Loadable Files¶

SPI boot shall be the primary boot option for the platforms (Ex: AMIC110 ICE) which does not support SD card interface. All the diagnostic tests are integrated into framework binary for the ease of use in the case of SPI boot. Integrated diagnostic framework test binary can be loaded and executed through UART port.

Use below command to build the diagnostic tests and create SPI flash loadable files.

- make <BOARD>_spi

3.2.2.5. Make targets¶

The simplest invocation is to use “make <BOARD>” to compile all the applications. Here is a list of make targets implemented for the diagnostic makefile:

- make <BOARD> - compile all diagnostic applications for one specific BOARD

- make clean - clean and remove all applications for all supported BOARDs

- make <BOARD>_clean - clean and remove all application for one specific BOARD

- make <BOARD>_sd - compile all diagnostic applications for one specific BOARD and create the SD card loadable files with those compiled applications

- make <BOARD>_spi - compile all diagnostic applications for one specific BOARD and create the SPI flash loadable files with those compiled applications

The <BOARD> supported depends on your Processor SDK RTOS variant. Refer to following table for available <BOARD> for each Processor SDK RTOS variant:

| make target / Variant | am335x | am437x | am57xx | k2g | omapl13x | AM65xx |

|---|---|---|---|---|---|---|

| <Board> | evmAM335x skAM335x bbbAM335x icev2AM33 5x iceAMIC11 0 | evmAM437x skAM437x idkAM437x | idkAM572x idkAM571x evmAM572x idkAM574x | evmK2G iceK2G | evmOMAPL1 37 (No Boot support. Diagnosti cs need to run from CCS) |

am65xx_evm am65xx_idk (Supports A53 & R5 cores) |

Note

OMAPL137 EVM diagnostic tests does not support executing from a boot device. Use the command make evmOMAPL137 to build the diagnostics. Diagnostics test binaries need to be executed from CCS.

3.2.3. Running the Diagnostic Examples¶

3.2.3.1. Loading through SD Card (Default Method)¶

Your SD card must be set up to a bootable format. Refer to the Processor SDK RTOS Boot page for information on how the SD card is handled.

You will need to compile the diagnostic applications for your BOARD, created their respective SD card loadable files, and copied them onto an SD card. You will also need the SBL (renamed to “MLO”) on the SD card. To do so:

- cd <PDK>/packages/ti/board/diag

- make <BOARD>_sd

- copy all the content under <PDK>/packages/ti/board/bin/<BOARD>/sd to your SD card

- copy the MLO to your SD card (default location at <PDK>/packages/ti/boot/sbl/binary/<BOARD>/mmcsd

- insert your SD card into your board and power on your board

- open Terminal emulator program eg: Teraterm to connect to the board’s UART console

Note

Use MAIN UART0 console for running the tests on A53 core and MCU UART console for running the tests on R5 core for AM65xx platform.

- press the “Hard Reset” button on your board. (This is to force re-booting, and not absolutely necessary. Because Terminal emulator program is opened after boot is powered on, you would’ve missed the initial printout messages. This step is for demonstration and confidence checking that the board has booted correctly)

Note

Diagnostic tests on AM65xx platform supports A53 and R5 cores. A53 binary path: <PDK>/packages/ti/board/bin/<BOARD>/sd/armv8. R5 binary path: <PDK>/packages/ti/board/bin/<BOARD>/sd/armv7.

Note

SBL binary name is different on AM65xx platform and requires system firmware binary also to be copied to SD card. Copy the sbl_mmcsd_img_mcu1_0_release.tiimage file from <PDK>/packages/ti/boot/sbl/binary/mmcsd/<BOARD> to SD card and rename it to tiboot3.bin. Copy the system firmware image <PDK>/packages/ti/drv/sciclient/soc/V0/sysfw.bin to SD card

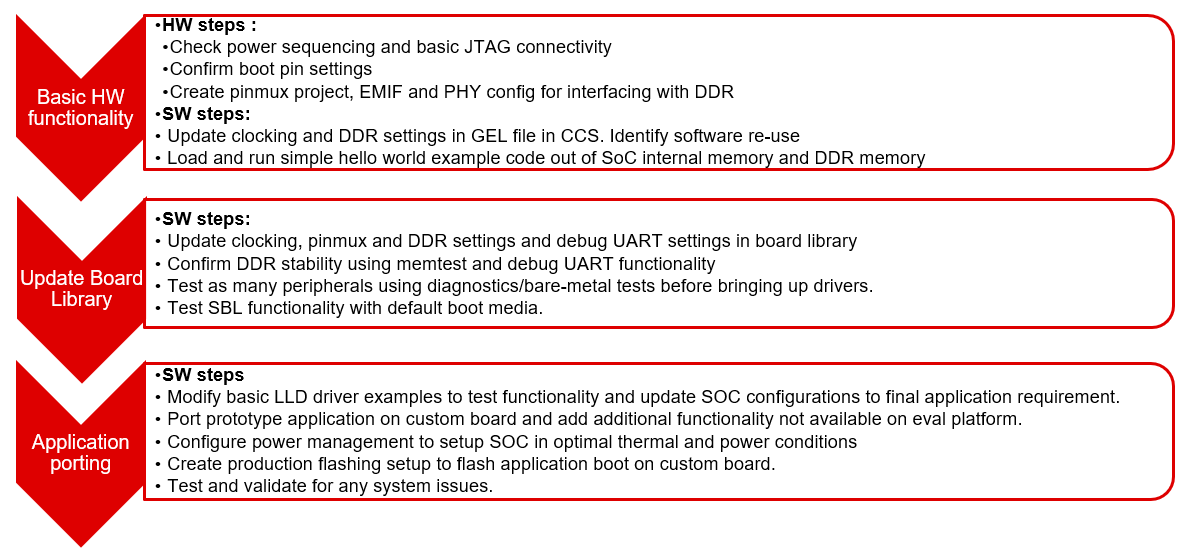

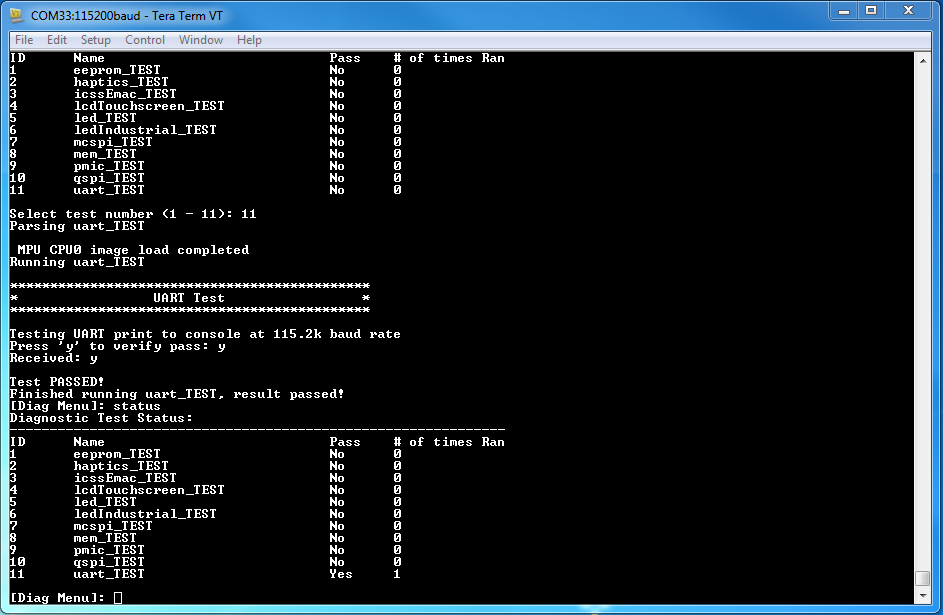

You should see the following screen when board is bootted with diagnostic binaries in SD card:

The framework diagnostic application should be loaded through SBL, and gives you the options:

- help - prints the command menu and descriptions of the commands

- run - run a diagnostic application found on the SD card

- status - current status of the framework run

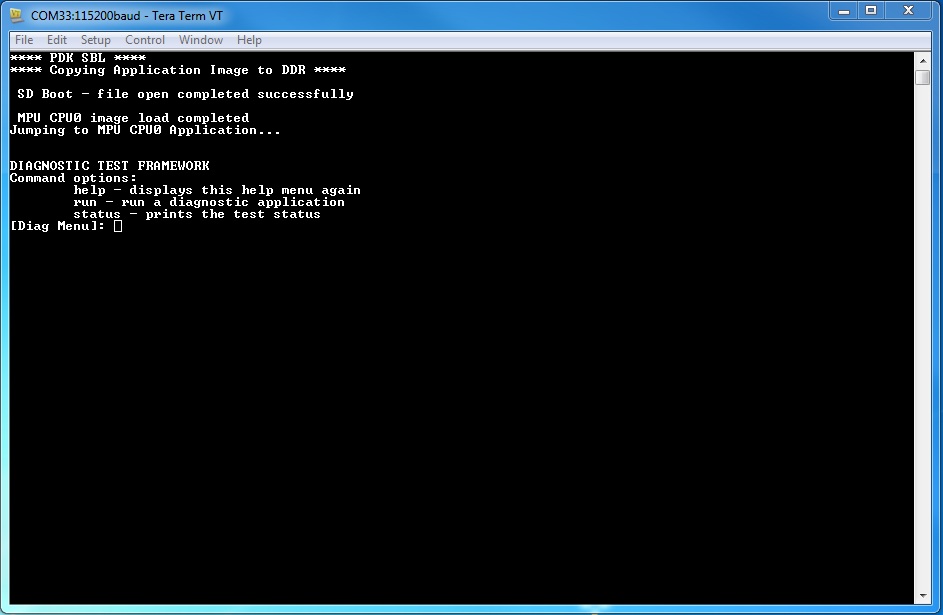

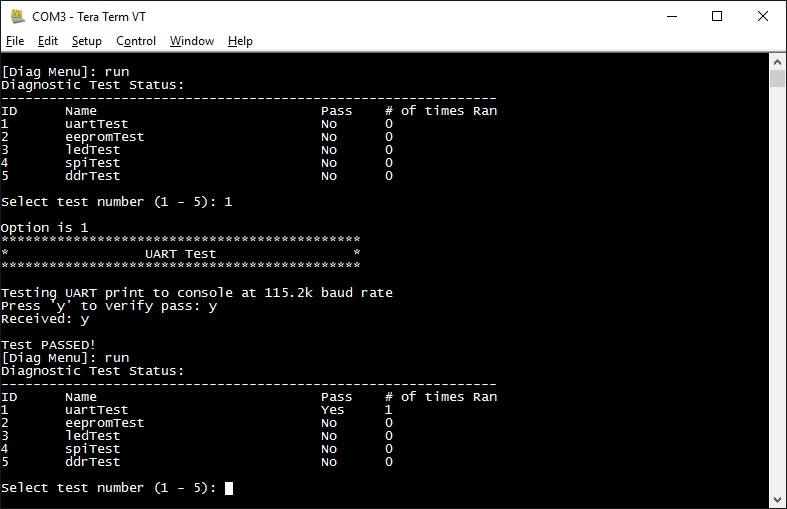

Below is an example of running a diagnostic application:

Result of return from above run:

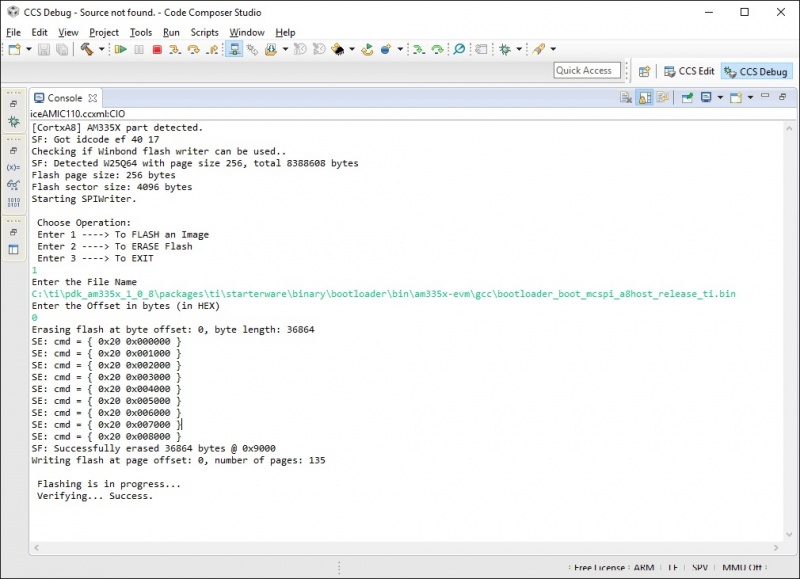

3.2.3.2. Loading through SPI Flash¶

This section describes creating the diagnostic test images for SPI flash booting, programming and running them from SPI flash. Currently SPI boot is supported only by iceAMIC110 platform.

You will need to compile the diagnostic applications for your BOARD, create their respective SPI flash loadable files, and program them onto SPI flash. To do so:

- cd <PDK>/packages/ti/board/diag

- make <BOARD>_spi

- Start CCS and launch target configuration file for AMIC110 ICE board

- Connect the target, load and run the SPI flash writer binary. Prebuilt SPI flash writer is available at <AM335x PDK>packagestistarterwaretoolsflash_writerspi_flash_writer_AM335X.out

- Choose option 1 to initiate image flashing

- Enter the file name as SPI bootloader along with full path (Ex: <AM335x PDK>packagestistarterwarebinarybootloaderbinam335x-evmgccbootloader_boot_mcspi_a8host_release_ti.bin)

- Enter offset as 0

- Wait until flashing completes successfully

- Rerun the SPI flash writer binary and program diagnostic framework loader at offset 20000. Diagnostic framework loader binary will be available at <AM335x PDK>packagestiboardbiniceAMIC110spiapp

- Rerun the SPI flash writer binary and program diagnostic framework at offset 40000. Diagnostic framework binary will be available at <AM335x PDK>packagestiboardbiniceAMIC110spiframework

Sample CCS output of SPI flash writer is shown below:

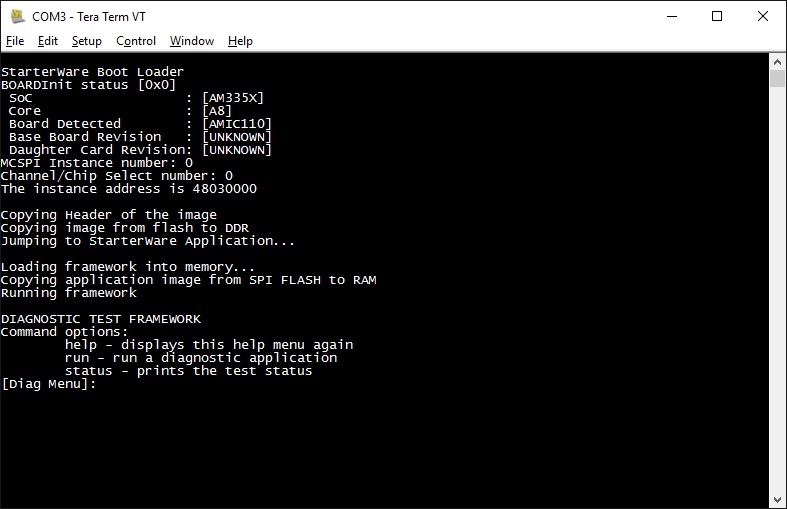

- open Terminal emulator program eg: Teraterm to connect to the board’s UART console

- press the “Hard Reset” button on your board. (This is to force re-booting, and not absolutely necessary. Because Terminal emulator program is opened after boot is powered on, you would’ve missed the initial printout messages. This step is for demonstration and confidence checking that the board has booted correctly)

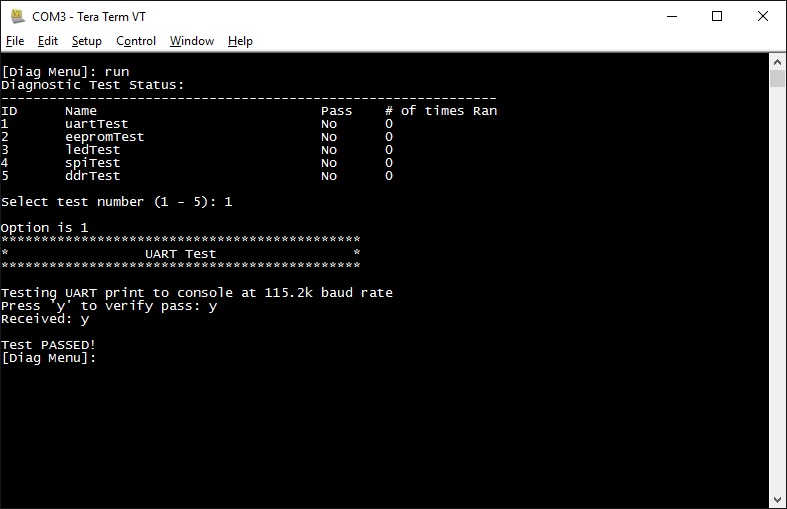

You should see the following screen:

- help - prints the command menu and descriptions of the commands

- run - run a diagnostic application found on the SD card

- status - current status of the framework run

Below is an example of running a diagnostic application:

3.2.3.3. Running or debugging on CCS¶

To debug your application, CCS can give you access to the chip’s memory and register values. You can follow the below steps to load and run an application in CCS. If you have a SD card loadable image, and is able to load your application, you can connect to the A15 core in CCS and load symbols without having to load and run the entire application. After running “make all” or “make $BOARD”, the output files should be generated under <PDK>/packages/ti/board/bin/ directory. You will have to navigate down to the $BOARD you’re building (eg. idkAM572x, evmAM572x, etc.) and the $TARGET core you’re building for (eg. armv7).

For the existing diagnostic applications, you may need to define PDK_RAW_BOOT before compiling. This is done by adding the line “#define PDK_RAW_BOOT” to an individual application source file or to <PDK>/packages/ti/board/src/<BOARD>/include/board_cfg.h to apply for all applications. This is used because the default diagnostic loading method is through SD card, and the pinmux is done already. Adding this option only forces the diagnostic applications to do pinmuxing within the application itself (and not depend it being done).

To run on CCS:

- Connect USB cable to the board’s JTAG

- Connect the UART serial cable. For the IDK boards, the UART console is the same as the usb JTAG connector, so no additional cable is necessary.

- Plug in power cord to your board

- Press the power button on the board to turn the board on

- Setup and run CCSv6.1 (or higher). Follow the Processor SDK RTOS Getting Started Guide on how to setup your CCS to connect to the board

- Launch target configuration for the board

- Connect to the core that you built your application for. For example: for idkAM572x armv7 projects, click on the Cortex A-15 MPU0 core and press the connect button

- Load the program by pressing the load button and navigate the explorer to the .out file that you want to load

- Press the Run button to run the program

- Check UART console to see if anything is printed out. **If nothing is printed out, pause the core and see where the program counter is at. If it is at 0x3808c (or near it), try reloading the program and running again.

Note

Diagnostics are built for both DSP (C674x) and ARM (arm9) cores on omapl13x platform.

3.2.3.4. Running on a different ARM core¶

The diagnostic baremetal applications are typically targeted for Core 0 of an ARM corepac. It is possible to load and run it on one of the subcores in CCS. To do so, please consider the following:

- Enable Cache - setup typically only enables cache for the main ARM core. You may have to explicitly enable the data and instruction cache. See relevant cache functions under pdk/packages/ti/csl/arch.

- [For AM57x boards] Set OPP to high - SBL would set OPP to high for Core 0, but may not do it for the subcores. You can do so by using the GEL file. After connecting to the core, run the function under Scripts -> AM572x PRCM CLOCK configuration -> AM572x_PRCM_Clock_Config_OPPHIGH (similarly named for AM571x).

3.2.4. Diagnostic Applications¶

| Name | Description | AM65xx EVM | AM65xx IDK | GP AM572x | IDK AM572x/AM574x | IDK AM571x | EVM K2G | ICE K2G | EVM AM335x | SK AM335x | BBB AM335x | ICEv2 AM335x | EVM AM437x | SK AM437x | IDK AM437x | EVM OMAPL137 | ICE AMIC110 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| lcdTouchscreen_TEST | Test for device detection and read the X, Y and Z axis values to confirm values within range. | x | x | x | x | ||||||||||||

| adc_TEST | Test for ADC configuration for Channel sequencing and One shot mode operation. | x | x | x | x | ||||||||||||

| ambient_TEST | Test for device detection on board and working of the light sensor. | x | x | ||||||||||||||

| buzzer_TEST | Writes to GPIO in connected to a buzzer. Requires user to verify sound | x | x | ||||||||||||||

| clock_TEST | Probes the clock generator on I2C bus | x | |||||||||||||||

| currentMonitor_TEST | Read voltage, current on I2C devices | x | x | x | |||||||||||||

| currentMonitorStress_TEST | Read voltage, current on I2C devices. Test is repeated for 100 cycles. Press ‘b’ to stop the test before completing test cycles. | x | x | ||||||||||||||

| dcan_TEST | Does DCAN loopback writes and reads. Passes on successful return. | x | x | x | |||||||||||||

| eeprom_TEST | Reads the EEPROM and prints out the board’s ID information. Passes on successful I2C reads. EEPROM will need to be programmed prior in order for a correct read. | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

| emac_TEST | Sends packet o PHY loopback t verify MAC operations | x | x | x | |||||||||||||

| emacStress_TEST | Verifies EMAC Ethernet ports by sending and receiving 10240 packets. | x | x | ||||||||||||||

| emmc_TEST | Writes to and read from eMMC memory. Passes on reading back the correct value as the one written | x | x | x | x | x | x | ||||||||||

| emmcStress_TEST | Writes to and read from eMMC memory. Test covers the entire eMMC memory | x | x | ||||||||||||||

| app | The main diagnostic application. This is loaded by SBL and can load other diagnostic applications on the SD card. | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

| gmac_TEST | Sends and receive packets over ethernet, both internally and externally. Passes on receiving all packets. | x | x | ||||||||||||||

| haptics_TEST | Writes to the GPIO pin connected to a motor (haptics). Requires user to verify that the motor is active. | x | x | x | |||||||||||||

| hdmi_TEST | Tests HDMI display output | x | |||||||||||||||

| icssEmac_TEST | Configures one ICSS EMAC port and tests functionality via packet loopback. | x | x | ||||||||||||||

| lcd_TEST | Tests LCD display output and touch input | x | x | ||||||||||||||

| lcdTouchscreen_TEST | Prompts the user for touches on the LCD touchscreen and report back its location. Requires user to input 9 simultaneous touches to verify pass. | x | x | ||||||||||||||

| led_TEST | Cycles through GPIO LEDs on the board. Requires user to verify the LEDs blink. | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

| ledStress_TEST | Cycles through GPIO LEDs on the board. Requires user to verify the LEDs blink. Test is repeated for 100 cycles. Press ‘b’ to stop the test before completing test cycles. | x | x | ||||||||||||||

| ledIndustrial_TEST | Cycles through the I2C LEDs on the board. Requires user to verify LEDs blink. | x | x | x | x | x | |||||||||||

| ledIndustrialStress_TEST | Cycles through the I2C LEDs on the board. Requires user to verify LEDs blink. Test is repeated for 100 cycles. Press ‘b’ to stop the test before completing test cycles. | x | x | ||||||||||||||

| mcspi_TEST | Attempts one write and read on the MCSPI header. Requires user to verify the value being read back is as expected. | x | x | x | x | ||||||||||||

| mem_TEST | Writes and reads to external (DDR) memory of the board. Value written/read is the address of the word. This is done two times, for value and ~value (complement), to test for all bits. | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

| memStress_TEST | Writes and reads to external (DDR) memory of the board. Walking 1’s and walking 0’s tests are executed on the whole DDR memory | x | x | ||||||||||||||

| mmcsd_TEST | Writes to and read from MMCSD memory. Passes on reading back the correct value as the one written | x | x | x | x | x | x | x | x | x | x | x | x | ||||

| mmcsdStress_TEST | Writes to and read from MMCSD memory. Passes on reading back the correct value as the one written. Entire SD card memory starting from 1.5GB offset is written/read during the test. | x | x | ||||||||||||||

| nand_TEST | Tests reading and writing to NAND flash memory | x | |||||||||||||||

| norflash_TEST | Tests reading and writing to NOR flash memory | x | x | x | |||||||||||||

| norflashStress_TEST | Tests reading and writing to NOR flash memory. Entire NOR flash memory is accessed during the test. | x | x | ||||||||||||||

| oled_TEST | Light up the OLED display to verify functionality | x | |||||||||||||||

| pmic_TEST | Writes and reads to the PMIC controller. This is to verify ability to use I2C to control PMIC. Test passes on successful read and write. | x | x | x | x | x | x | x | x | x | |||||||

| qspi_TEST | Tests the Quad SPI by writing and reading back the value written to memory. Test passes on correct data read back. | x | x | x | x | x | |||||||||||

| rotarySwitch_TEST | Tests the rotary switch at the 10 possible positions | x | x | ||||||||||||||

| rtc_TEST | Test for setting date and time to RTC registers and running the clock | x | x | x | x | x | x | x | |||||||||

| temperature_TEST | Tests reading back from temperature sensor via I2C. Test passes on successful I2C reads. | x | x | x | x | x | x | ||||||||||

| temperatureStress_TEST | Tests reading back from temperature sensor via I2C. Test passes on successful I2C reads. Test is repeated for 100 cycles. Press ‘b’ to stop the test before completing test cycles. | x | x | ||||||||||||||

| uart2usb_TEST | Tests uart messages over usb port. | x | |||||||||||||||

| uart_TEST | Data Path continuity test for UART output. Requires user to verify that outputs do appear on console. | x | x | x | x | x | x | x | x | x | x | x | x | x | x | ||

| uartStress_TEST | Verifies UART port with large block of data transfer. Sends 10MB of data from the board to serial console. Teraterm script loops the data back to the board. Data recieved on the board and verified. RS485 to RS232 coverter is needed to run the test on AM65xx platform. Need to run this test from CCS. SD boot support is not available. |

x | x | ||||||||||||||

| mcasp_TEST | On-board audio codec functionality is exercised by this test. Audio supplied at EVM audio input port will loopback to audio output port. This test is intended to demonstrate baremetal functionality of mcasp, edma3 and i2c CSL modules without depending on the LLD libraries. No console output is supported by this test. | x | x | ||||||||||||||

| mcaspAudioDC_TEST | Multi-channel audio daughter card functionality is exercised by this test. Audio supplied at audio DC input ports will loopback to audio DC output ports. This test is intended to demonstrate bare metal functionality of mcasp, edma3 and spi CSL modules without depending on the LLD libraries. No console output is supported by this test. | x | |||||||||||||||

| pwm_TEST | Demonstrates the usage of PWM CSL FL APIs by configuring the PWM module to generate a pulse of 1KHz with different duty cycle - 25, 50 and 75%. | x | x | x | x | ||||||||||||

| usbDevice_TEST | Verifies the USB device mode operation of board under test. USB modules operates at high speed (2.0) Board is exposed as USB MSC device to host PC during the test. | x | x | ||||||||||||||

| usbHost_TEST | Verifies the USB host mode operation of boardf under test. USB modules operates at high speed (2.0) during the test. File write/read and data verification on the connected USB device is done during the test | x | x | ||||||||||||||

| usbHostStress_TEST | Verifies the USB host mode operation of boardf under test. USB modules operates at high speed (2.0) during the test. File write/read and data verification on the connected USB device is done during the test Test is repeated for 100 cycles. Press ‘b’ to stop the test before completing test cycles. | x | x | ||||||||||||||

| ospi_TEST | Tests the Octal SPI by writing and reading back the value written to memory. Test passes on correct data read back. | x | x | ||||||||||||||

| ospiStress_TEST | Tests the Octal SPI by writing and reading back the value written to memory. Test passes on correct data read back. Entire OSPI flash memory is accessed during the test. | x | x | ||||||||||||||

| pcie_TEST | Tests the PCIe interface in end point and rootcomplex mode using two boards. Data is sent from one board to other and sent it back to the first board for verification. | x | x | ||||||||||||||

| bootEeprom_TEST | Verifies boot EEPROM by writing a block of data, reading back written data for correctness. | x | x | ||||||||||||||

| bootEepromStress_TEST | Verifies boot EEPROM read/write covering entire memory. | x | x | ||||||||||||||

| extRtc_TEST | Test for setting date and time to external RTC and running the clock | x | x | ||||||||||||||

| extRtcStress_TEST | Test for setting date and time to external RTC and running the clock. Test is repeated for 100 cycles. Press ‘b’ to stop the test before completing test cycles. | x | x | ||||||||||||||

| icssgEmac_TEST | Verifies ICSSG EMAC ports in loopback with one port connected to another port. 10 packets are sent and received during the test. | x | x | ||||||||||||||

| icssgEmacStress_TEST | Verifies ICSSG EMAC ports in loopback with one port connected to another port. 10240 packets are sent and received during the test. | x | x | ||||||||||||||

| icssgLed_TEST | Cycles through LEDs on the IDK application board. | x | |||||||||||||||

| icssgLedStress_TEST | Cycles through LEDs on the IDK application board. Test is repeated for 100 cycles. Press ‘b’ to stop the test before completing test cycles. | x | |||||||||||||||

| bootSwitch_TEST | Verifies boot mode switch by configuring boot strap pins as GPIOs and reading the pin state with boot switch set in different patterns | x | x | ||||||||||||||

| button_TEST | Verifies push buttons on the board. Test prompts for pressing a specific button which will be detected by the test. | x | x | ||||||||||||||

| mcan_TEST | Verifies MCAN ports on the board with two ports connected with each other. Data is sent from one port and received on another port. Both ports are veirified for Tx and Rx | x | |||||||||||||||

| mcanStress_TEST | Verifies MCAN ports on the board with two ports connected with each other. 10240 packets are sent from one port and received on another port. Both ports are veirified for Tx and Rx | x | |||||||||||||||

| rs485_TEST | Verifies PRU UART port on the board. Supports board to board test and single board test. RS485 to RS232 coverter is needed to run the test on AM65xx platform | x | x | x | |||||||||||||

| rs485Stress_TEST | Verifies PRU UART port on the board. Sends 10MB of data from the board to serial console. Teraterm script loops the data back to the board. Data recieved on the board and verified. RS485 to RS232 coverter is needed to run the test on AM65xx platform. Need to run this test from CCS. SD boot support is not available. |

x |

3.2.5. Additional Jumper or Hardware Settings¶

3.2.5.1. Current Monitor¶

For iceK2G, this test expects J16 and J17 to be connected with jumper shunts. This enables the current monitors to be used.

3.2.5.2. GMAC¶

For idkAM572x, idkAM571x, idkAM574x and evmAM572x, this test expects loopback plugs to be used on both Ethernet ports. These loopback plugs will loopback the TX lines back to the RX lines. The Ethernet ports are the RJ-45 connectors labeled “Ethernet” on the board.

3.2.5.3. ICSS EMAC¶

For idkAM572x, idkAM574x and idkAM571x, this test expects loopback plug to be used on J6. These loopback plugs will loopback the TX lines back to the RX lines. For iceK2G, this test expects loopback plugs to be used on all four ICSS EMAC ports.

3.2.5.4. LCD Touchscreen¶

For idkAM572x, idkAM574x and idkAM571x, this test expects the LCD module to be connected. This requires the two ribbon cables (one for display, one for the capacitive-touch IC) to be connected.

3.2.5.5. McSPI¶

For idkAM572x, idkAM574x and idkAM571x, this test expects pins to be connected to the Industrial I/O header. The Industrial I/O header, J37, has two columns in parallel, one of which is the McSPI input and the other being VDD. Thus, connecting any row with a jumper will yield a ‘1’ read on that McSPI input. By connecting the first, second, third, and forth row with jumpers would yield 0x1, 0x2, 0x4, and 0x8 being read respectively.

3.2.5.6. PWM¶

PWM output generated while running the diagnostic test can be verified at below pins.

evmK2G - J12 pin 33

evmAM572x - P17 pin 5

idkAM437x - J16 pin 14

evmAM335x - J5 pin 13

3.3. Diagnostics Execution¶

3.3.1. Overview¶

Detailed test procedure and additional HW setup needed for running the processor SDK board diagnostic tests are explained in the following sections. Logs shown for each test are for sample reference, actual logs may slightly vary from platform to platform.

Two different modes of diagnostic tests are supported - Functional and Stress. Functional tests verify basic functionality of an interface to confirm the interface HW connectivity. Stress tests verify the functionality of an interface under stress conditions which will confirm the stability of the HW interface.

Refer to Diagnostic Applications section for details of the platforms supported by each of the diagnostic tests described below.

Application/Daughter cards required for running the test are not mentioned in the test setup assuming the tests are run with full HW kit.

3.3.2. Functional Tests¶

This section describes the test procedure and setup for diagnostic functional tests.

3.3.2.1. Accelerometer Test¶

This test verifies the Accelerometer sensor on the HW platform under test.

3.3.2.1.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.1.2. Test Setup¶

No specific test setup is needed. Use the default HW setup recommended in HW user manual.

3.3.2.1.3. Test Execution¶

- Select the menu option to run ‘accelerometer_TEST’

- Verify the test log on serial console

3.3.2.1.4. Test Log¶

Sample log for Accelerometer test is shown below

*********************************************

* Accelerometer Test *

*********************************************

Test: Expected Result: Actual Result: Result:

---------------- ---------------- -------------- -------

0x32 PASS

Self-Test(X Axis) 120-550 247 PASS

Self-Test(Y axis) 120-550 192 PASS

Self-Test(Z Axis) 140-750 349 PASS

Exiting

3.3.2.2. ADC Test¶

This test verifies ADC interface on the HW platform under test.

3.3.2.2.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.2.2. Test Setup¶

No specific test setup is needed. Use the default HW setup recommended in HW user manual.

3.3.2.2.3. Test Execution¶

- Select the menu option to run ‘adc_TEST’

- Verify the test log on serial console

3.3.2.2.4. Test Log¶

Sample log for ADC test is shown below

*********************************************

* ADC Test *

*********************************************

Voltage sensed on the AN0 line : 846mV

Voltage sensed on the AN1 line : 1156mv

Test PASSED!

3.3.2.3. Boot EEPROM Test¶

This test verifies Boot EEPROM memory. First and last page of the EEPROM are written with a test pattern and read back for data verification.

3.3.2.3.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.3.2. Test Setup¶

Make sure pins 2-3 of J44 and J45 headers on AM65x CP board are shorted

3.3.2.3.3. Test Execution¶

- Select the menu option to run ‘bootEeprom_TEST’

- Verify the test log on serial console

3.3.2.3.4. Test Log¶

Sample log for boot EEPROM test is shown below

*********************************************

* Boot EEPROM Test *

*********************************************

Running Boot EEPROM test

Detecting the Boot EEPROM device...

Boot EEPROM device detection successful

Boot EEPROM boundary verification test...

Verifying the Boot EEPROM first page...

Verifying the Boot EEPROM last page...

Boot EEPROM boundary verification test successful

Boot EEPROM test Passed

3.3.2.4. Boot Switch Test¶

Test verifies boot mode switch by configuring boot strap pins as GPIOs and reading the pin state with boot switch set in different patterns. Test prompts to set the boot switch with a specific pattern and waits for user confirmation of the setting. ON-OFF-ON... sequence indicated by the test starts from switch position 1.

3.3.2.4.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.4.2. Test Setup¶

No specific test setup is needed. Use the default HW setup recommended in HW user manual.

3.3.2.4.3. Test Execution¶

- Select the menu option to run ‘bootSwitch_TEST’

- Setup the boot switch as instructed by the serial console log

- Verify the test log on serial console

3.3.2.4.4. Test Log¶

Sample log for boot switch test is shown below

*********************************************

* Boot Switch Test *

*********************************************

Set All switches to OFF

Press Enter after setting the switches

Set the Switches to ON-OFF-ON-OFF...

Press Enter after setting the switches

Set the Switches to OFF-ON-OFF-ON...

Press Enter after setting the switches

Set All switches to ON

Press Enter after setting the switches

Test Passed

3.3.2.5. Button Test¶

Verifies push buttons on the board. Test prompts for pressing a specific button which should be detected by the test and displayed on the console.

3.3.2.5.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.5.2. Test Setup¶

No specific test setup is needed. Use the default HW setup recommended in HW user manual.

3.3.2.5.3. Test Execution¶

- Select the menu option to run ‘button_TEST’

- Press the button as instructed by the test messages on the serial console.

- Verify the test log on serial console. Make sure the button press is detected properly.

Note

Button release detection is supported only on AM65xx platform.

3.3.2.5.4. Test Log¶

Sample log for push button test is shown below

*********************************************

* Button Test *

*********************************************

Running button test...

Button SW 5 WAIT Waiting for button press Button Pressed

Button SW 5 WAIT Waiting for button release Button released

Button SW 5 PASS

Button SW 6 WAIT Waiting for button press Button Pressed

Button SW 6 WAIT Waiting for button release Button released

Button SW 6 PASS

Test PASSED!

3.3.2.6. Buzzer Test¶

This test verifies the Buzzer interface on the HW platform under test.

3.3.2.6.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.6.2. Test Setup¶

No specific test setup is needed. Use the default HW setup recommended in HW user manual.

3.3.2.6.3. Test Execution¶

- Select the menu option to run ‘buzzer_TEST’

- Verify the Buzzer sound on the HW platform

- Verify the test log on serial console

- Press ‘y’ to confirm proper buzzer output or any other key to indicate failure

3.3.2.6.4. Test Log¶

Sample log for buzzer test is shown below

*********************************************

* Buzzer Test *

*********************************************

Testing Buzzer sound

Press 'y' to verify pass: y

Received: y

Test PASSED!

3.3.2.7. Clock Generator Test¶

This test verifies clock generator interface on the HW platform under test. Need to probe and confirm the clocks during the test.

3.3.2.7.1. Test Accessories¶

Oscilloscope to verify the clock outputs

3.3.2.7.2. Test Setup¶

No specific test setup is needed. Use the default HW setup recommended in HW user manual.

3.3.2.7.3. Test Execution¶

- Select the menu option to run ‘clock_TEST’

- Verify the test log on serial console

- Verify the clock generator output clocks and confirm the result on the serial console

3.3.2.7.4. Test Log¶

Sample log for clock generator test is shown below

**********************************

CLOCK GENERATOR Test

**********************************

Running Clock generator Detect Test

Clock generator Detection Successful!

Clock generator Detect Test Passed!

Running Clock generator probe Test

Probe the clock generator clock outputs

Are the signals generated properly ?

Press 'Y' to confirm, any other key to deny

y

Clock generator probe Test Passed!

Clock generator Test Passed!

Clock generator Tests Completed!!

-----------------X-----------------

3.3.2.8. Current Monitor Test¶

Test reads the voltage and current values from different current monitor devices available on the board. All the current monitor devices available on the board are verified during the test.

3.3.2.8.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.8.2. Test Setup¶

For iceK2G, this test expects J16 and J17 to be connected with jumper shunts. This enables the current monitors to be used.

3.3.2.8.3. Test Execution¶

- Select the menu option to run ‘currentMonitor_TEST’

- Verify the test log on serial console

3.3.2.8.4. Test Log¶

Sample log for current monitor test is shown below

**********************************************

* Current Monitor Test *

**********************************************

Running Current Monitor Test...

Verifying Device VDD_CORE at Address - 0x40

Setting the configuration register...

Setting the calibration register...

Calibration Value = 16777

Reading the Shunt Voltage register...

Shunt Voltage Register Value = 9

Shunt Voltage = 0mV

Reading the Bus Voltage register...

Bus Voltage Register Value = 800

Bus Voltage = 1000mV

Reading the Power register...

Power Register Value = 3

Power = 915mW

Reading the Current register...

Current Register Value = 74

Current = 11mA

Verifying Device VDD_MCU at Address - 0x41

Setting the configuration register...

Setting the calibration register...

Calibration Value = 16777

Reading the Shunt Voltage register...

Shunt Voltage Register Value = 1534

Shunt Voltage = 3mV

Reading the Bus Voltage register...

Bus Voltage Register Value = 797

Bus Voltage = 996mV

Reading the Power register...

Power Register Value = 501

Power = 19108mW

Reading the Current register...

Current Register Value = 12566

Current = 383mA

Verifying Device VDD_MPU at Address - 0x42

Setting the configuration register...

Setting the calibration register...

Calibration Value = 27962

Reading the Shunt Voltage register...

Shunt Voltage Register Value = 6

Shunt Voltage = 0mV

Reading the Bus Voltage register...

Bus Voltage Register Value = 802

Bus Voltage = 1002mV

Reading the Power register...

Power Register Value = 3

Power = 503mW

Reading the Current register...

Current Register Value = 82

Current = 7mA

Verifying Device SoC_DVDD3V3 at Address - 0x43

Setting the configuration register...

Setting the calibration register...

Calibration Value = 27962

Reading the Shunt Voltage register...

Shunt Voltage Register Value = 15

Shunt Voltage = 0mV

Reading the Bus Voltage register...

Bus Voltage Register Value = 2665

Bus Voltage = 3331mV

Reading the Power register...

Power Register Value = 28

Power = 2670mW

Reading the Current register...

Current Register Value = 205

Current = 18mA

Verifying Device SoC_DVDD1V8 at Address - 0x44

Setting the configuration register...

Setting the calibration register...

Calibration Value = 5592

Reading the Shunt Voltage register...

Shunt Voltage Register Value = 108

Shunt Voltage = 0mV

Reading the Bus Voltage register...

Bus Voltage Register Value = 1442

Bus Voltage = 1802mV

Reading the Power register...

Power Register Value = 21

Power = 3204mW

Reading the Current register...

Current Register Value = 295

Current = 26mA

Verifying Device SoC_AVDD1V8 at Address - 0x45

Setting the configuration register...

Setting the calibration register...

Calibration Value = 41943

Reading the Shunt Voltage register...

Shunt Voltage Register Value = 1196

Shunt Voltage = 2mV

Reading the Bus Voltage register...

Bus Voltage Register Value = 1442

Bus Voltage = 1802mV

Reading the Power register...

Power Register Value = 387

Power = 14760mW

Reading the Current register...

Current Register Value = 5358

Current = 65mA

Verifying Device SoC_VDDS_DDR at Address - 0x46

Setting the configuration register...

Setting the calibration register...

Calibration Value = 8388

Reading the Shunt Voltage register...

Shunt Voltage Register Value = 256

Shunt Voltage = 0mV

Reading the Bus Voltage register...

Bus Voltage Register Value = 956

Bus Voltage = 1195mV

Reading the Power register...

Power Register Value = 50

Power = 1335mW

Reading the Current register...

Current Register Value = 1049

Current = 63mA

Verifying Device VDD_DDR at Address - 0x47

Setting the configuration register...

Setting the calibration register...

Calibration Value = 8388

Reading the Shunt Voltage register...

Shunt Voltage Register Value = 38

Shunt Voltage = 0mV

Reading the Bus Voltage register...

Bus Voltage Register Value = 957

Bus Voltage = 1196mV

Reading the Power register...

Power Register Value = 8

Power = 689mW

Reading the Current register...

Current Register Value = 156

Current = 9mA

3.3.2.9. DCAN Test¶

This test verifies the DCAN ports on the HW platform under test. Test supports verifying the DCAN interface in internal and external loopback modes.

3.3.2.9.1. Test Accessories¶

DCAN loopback cable (for evmK2G)

3.3.2.9.2. Test Setup¶

Connect two DCAN ports (P2 and P3) with DCAN loopback cable - only on evmK2G

3.3.2.9.3. Test Execution¶

- Select the menu option to run ‘dcan_TEST’

- Follow the instructions on serial console to select the DCAN instance

- Verify the test log on serial console

3.3.2.9.4. Test Log¶

Sample log for DCAN test is shown below

*********************************************

* DCAN Test *

*********************************************

**** DCAN APPLICATION TEST ****

Menu:

1. DCAN External Loopback test - DCAN1 Instance

2. DCAN Internal Loopback test - DCAN2 Instance

x. Exit

Select DCAN APPLICATION TEST : 1

DCAN External Loopback Test App: DCAN1 MSG OBJ 1 (TX) to DCAN1 MSG OBJ 2 (RX)

DCAN -- External Loopback Testmode test Passed!!

**** DCAN APPLICATION TEST ****

Menu:

1. DCAN External Loopback test - DCAN1 Instance

2. DCAN Internal Loopback test - DCAN2 Instance

x. Exit

Select DCAN APPLICATION TEST : 2

DCAN Internal Loopback Test App: DCAN2 MSG OBJ 1 (TX) to DCAN2 MSG OBJ 2 (RX)

DCAN -- Internal Loopback Testmode test Passed!!

**** DCAN APPLICATION TEST ****

Menu:

1. DCAN External Loopback test - DCAN1 Instance

2. DCAN Internal Loopback test - DCAN2 Instance

x. Exit

Select DCAN APPLICATION TEST : x

DCAN Application Test exiting...

3.3.2.10. EEPROM Test¶

This test reads and displays the board ID details from the EEPROM memory.

3.3.2.10.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.10.2. Test Setup¶

No specific test setup is needed. Use the default HW setup recommended in HW user manual.

3.3.2.10.3. Test Execution¶

- Select the menu option to run ‘eeprom_TEST’

- Verify the board ID details displayed on the serial console

3.3.2.10.4. Test Log¶

Sample log for Board ID EEPROM test is shown below

*********************************************

* EEPROM Test *

*********************************************

header: aa5533ee

boardName: 66AK2GICE

version: 1.0A

serialNum: 09164P540001

Test PASSED!

Note

Board ID content shown in the above log changes from platform to platform.

3.3.2.11. EMAC Test¶

This test verifies the EMAC Ethernet port on HW platform under test. Ethernet link and data transmit/receive are verified during this test. Ethernet interface is configured for 100mbps speed and 10 packets are sent/received during the test. Ethernet cable disconnect/reconnect and data transfer after cable connection is also verified during the test.

3.3.2.11.1. Test Accessories¶

Ethernet loopback cables/plugs

3.3.2.11.2. Test Setup¶

Connect the Ethernet loopback cables to the EMAC Ethernet port (RJ-45) on the board. Check below table for the details of EMAC Ethernet ports used by the test on different platforms.

| HW Platform | Ethernet Port |

|---|---|

| iceK2G | J10 |

| am65xx_evm | J12 on CP board |

| am65xx_idk | J12 on CP board |

3.3.2.11.3. Test Execution¶

- Select the menu option to run ‘emac_TEST’

- Follow the instructions on serial console for disconnecting and connecting the cable during the test.

- Verify the test log on serial console

3.3.2.11.4. Test Log¶

Sample log for Ethernet loopback test is shown below

************************************************

* ETHERNET LOOPBACK Test *

************************************************

Reading Ethernet PHY Register Dump...

Register Dump for PHY Addr - 0x0000

PHY Register 0x0000 - 0x1140

PHY Register 0x0001 - 0x7949

PHY Register 0x0002 - 0x2000

PHY Register 0x0003 - 0xa231

PHY Register 0x0004 - 0x01e1

PHY Register 0x0005 - 0xc1e1

PHY Register 0x0006 - 0x006f

PHY Register 0x0007 - 0x2001

PHY Register 0x0008 - 0x4806

PHY Register 0x0009 - 0x0300

PHY Register 0x000a - 0x8c00

PHY Register 0x000b - 0x0000

PHY Register 0x000c - 0x0000

PHY Register 0x000d - 0x401f

PHY Register 0x000e - 0x0006

PHY Register 0x000f - 0x3000

PHY Register(STRAP1) 0x006e - 0x0000

PHY Register(STRAP2) 0x006f - 0x0000

RGMII Control Register (RGMIICTL) Value - 0x00d3

--- RGMII_RX_CLK_DELAY - 0x0001

--- RGMII_TX_CLK_DELAY - 0x0001

RGMII Delay Control Register (RGMIIDCTL) Value - 0x0077

EMAC loopback test application initialization

main: emac_open success

Configuring Phy

Waiting for Link Status

Link is UP!!

Sending Packet: 1

Sending Packet: 2

Sending Packet: 3

Sending Packet: 4

Sending Packet: 5

Sending Packet: 6

Sending Packet: 7

Sending Packet: 8

Sending Packet: 9

Sending Packet: 10

Received Packet: 1

Received Packet: 2

Received Packet: 3

Received Packet: 4

Received Packet: 5

Received Packet: 6

Received Packet: 7

Received Packet: 8

Received Packet: 9

Received Packet: 10

Packets sent: 10, Packets received: 10

Ethernet Loopback test passed

All tests completed

Please disconnect the loopback cable

Link is Down

Please reconnect the loopback cable

Link is UP

Reading Ethernet PHY Register Dump...

Register Dump for PHY Addr - 0x0000

PHY Register 0x0000 - 0x1000

PHY Register 0x0001 - 0x796d

PHY Register 0x0002 - 0x2000

PHY Register 0x0003 - 0xa231

PHY Register 0x0004 - 0x01e1

PHY Register 0x0005 - 0xc1e1

PHY Register 0x0006 - 0x006f

PHY Register 0x0007 - 0x2001

PHY Register 0x0008 - 0x4006

PHY Register 0x0009 - 0x1000

PHY Register 0x000a - 0x0000

PHY Register 0x000b - 0x0000

PHY Register 0x000c - 0x0000

PHY Register 0x000d - 0x401f

PHY Register 0x000e - 0x0006

PHY Register 0x000f - 0x3000

PHY Register(STRAP1) 0x006e - 0x0000

PHY Register(STRAP2) 0x006f - 0x0000

RGMII Control Register (RGMIICTL) Value - 0x00d3

--- RGMII_RX_CLK_DELAY - 0x0001

--- RGMII_TX_CLK_DELAY - 0x0001

RGMII Delay Control Register (RGMIIDCTL) Value - 0x0077

EMAC loopback test application initialization

main: emac_open success

Configuring Phy

Waiting for Link Status

Link is UP!!

Sending Packet: 1

Sending Packet: 2

Sending Packet: 3

Sending Packet: 4

Sending Packet: 5

Sending Packet: 6

Sending Packet: 7

Sending Packet: 8

Sending Packet: 9

Sending Packet: 10

Received Packet: 1

Received Packet: 2

Received Packet: 3

Received Packet: 4

Received Packet: 5

Received Packet: 6

Received Packet: 7

Received Packet: 8

Received Packet: 9

Received Packet: 10

Packets sent: 10, Packets received: 10

Ethernet Loopback test passed

All tests completed

3.3.2.12. eMMC Test¶

This test verifies eMMC memory interface on the HW platform under test. 16KB of data is written and read during the test.

3.3.2.12.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.12.2. Test Setup¶

No specific test setup is needed. Use the default HW setup recommended in HW user manual.

3.3.2.12.3. Test Execution¶

- Select the menu option to run ‘emmc_TEST’

- Verify the test log on serial console

3.3.2.12.4. Test Log¶

Sample log for eMMC test is shown below

*********************************************

* eMMC Test *

*********************************************

PASS: Read/Write Success for this pattern

3.3.2.13. External RTC Test¶

This test verifies setting the time, date and running the clock for on-board RTC interface. RTC configuration is done through I2C interface. Time and date are read for 5 times for every 5secs during the test to demonstrate operation of the RTC clock.

3.3.2.13.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.13.2. Test Setup¶

No specific test setup is needed. Use the default HW setup recommended in HW user manual.

3.3.2.13.3. Test Execution¶

- Select the menu option to run ‘extRtc_TEST’

- Verify the test log on serial console

- Confirm the test result by pressing ‘y’ if RTC time/date changes properly or press any key for failure

3.3.2.13.4. Test Log¶

Sample log for external RTC test is shown below

*********************************************

* RTC Test *

*********************************************

Setting Time...

Setting Date...

Reading Time...

Reading Date...

Displaying time: 11:59:53 PM

Displaying Day: Sunday

Displaying Date: 31/12/18

Displaying time: 11:59:57 PM

Displaying Day: Sunday

Displaying Date: 31/12/18

Displaying time: 12:0:2 AM

Displaying Day: Monday

Displaying Date: 1/1/19

Displaying time: 12:0:7 AM

Displaying Day: Monday

Displaying Date: 1/1/19

Displaying time: 12:0:12 AM

Displaying Day: Monday

Displaying Date: 1/1/19

Displaying time: 12:0:17 AM

Displaying Day: Monday

Displaying Date: 1/1/19

If the time and date increment, press 'y' to indicate pass or any other character to indicate failure

y

RTC test passed...

3.3.2.14. GMAC Test¶

This test verifies the GMAC Ethernet ports of the HW platform under test.

3.3.2.14.1. Test Accessories¶

Ethernet loopback cables/plugs

3.3.2.14.2. Test Setup¶

Connect the Ethernet loopback cables to the GMAC Ethernet port (RJ-45) on the board. Check below table for the details of GMAC Ethernet ports used by the test on different platforms.

| HW Platform | Ethernet Port |

|---|---|

| idkAM571x | J10 & J12 |

| idkAM572x | J10 & J12 |

| idkAM574x | J10 & J12 |

| evmAM572x | Both ports of P5 |

3.3.2.14.3. Test Execution¶

- Select the menu option to run ‘gmac_TEST’

- Verify the test log on serial console

3.3.2.14.4. Test Log¶

Sample log for GMAC test is shown below

*********************************************

* GMAC Test *

*********************************************

Test Port Link Link-Speed Status Error

-------------------- ---- ---- -------------------- ------ ---------------------------

Phy Loopback 1 Up Phy Loopback PASS

10Mbps Full-Duplex 1 Up 10Mbps Full duplex PASS

100Mbps Half-Duplex 1 Up 100Mbps Half duplex PASS

100Mbps Full-Duplex 1 Up 100Mbps Full duplex PASS

Phy Loopback 2 Up Phy Loopback PASS

10Mbps Full-Duplex 2 Up 10Mbps Full duplex PASS

100Mbps Half-Duplex 2 Up 100Mbps Half duplex PASS

100Mbps Full-Duplex 2 Up 100Mbps Full duplex PASS

Exiting

3.3.2.15. Haptics Test¶

This verifies haptics motor using vibrations on the HW platform under test.

3.3.2.15.1. Test Accessories¶

No additional accessories are required for running this test.

3.3.2.15.2. Test Setup¶

No specific test setup is needed. Use the default HW setup recommended in HW user manual.

3.3.2.15.3. Test Execution¶

- Select the menu option to run ‘haptics_TEST’

- Verify the test log on serial console

- Check for the vibrations on the HW platform

3.3.2.15.4. Test Log¶

Sample log for Haptics test is shown below

*********************************************

* Haptics Test *

*********************************************

Testing Haptics (vibration)

Press 'y' to verify pass: y

Received: y

Test PASSED!

3.3.2.16. HDMI Test¶

This test verifies HDMI display port on the HW platform under test. Color bar and different colors are displayed on HDMI monitor during the test.

3.3.2.16.1. Test Accessories¶

- HDMI Display

- HDMI cable

3.3.2.16.2. Test Setup¶

Connect the HDMI Display to the HDMI port on the board. Check below table for the details of HDMI ports used by the test on different platforms.

| HW Platform | HDMI Port |

|---|---|

| evmK2G | J36 |

3.3.2.16.3. Test Execution¶

- Select the menu option to run ‘hdmi_TEST’

- Verify the color bar and different colors displayed on the HDMI Monitor.

- Verify the test log on serial console and confirm test result.

3.3.2.16.4. Test Log¶

Sample log for HDMI test is shown below

***********************

HDMI Test

***********************

Running HDMI Device Detect Test

sil9022 HDMI Chip version = b0

HDMI Device Detect Test Passed

Displaying Colorbar... WAIT Press 'y' if Colorbar is displayed, any other key for failure: y

Display Colorbar - PASS

Displaying WHITE... WAIT Press 'y' if WHITE is displayed, any other key for failure: y

Display WHITE - PASS

Displaying BLUE... WAIT Press 'y' if BLUE is displayed, any other key for failure: y

Display BLUE - PASS

Displaying GREEN... WAIT Press 'y' if GREEN is displayed, any other key for failure: y

Display GREEN - PASS

Displaying RED... WAIT Press 'y' if RED is displayed, any other key for failure: y

Display RED - PASS

Displaying PURPLE... WAIT Press 'y' if PURPLE is displayed, any other key for failure: y

Display PURPLE - PASS

Displaying PINK... WAIT Press 'y' if PINK is displayed, any other key for failure: y

Display PINK - PASS

Displaying BLACK... WAIT Press 'y' if BLACK is displayed, any other key for failure: y

Display BLACK - PASS

Displaying YELLOW... WAIT Press 'y' if YELLOW is displayed, any other key for failure: y

Display YELLOW - PASS

HDMI Tests Completed!!

-----------------X-----------------

3.3.2.17. ICSS EMAC Test¶