### Introduction

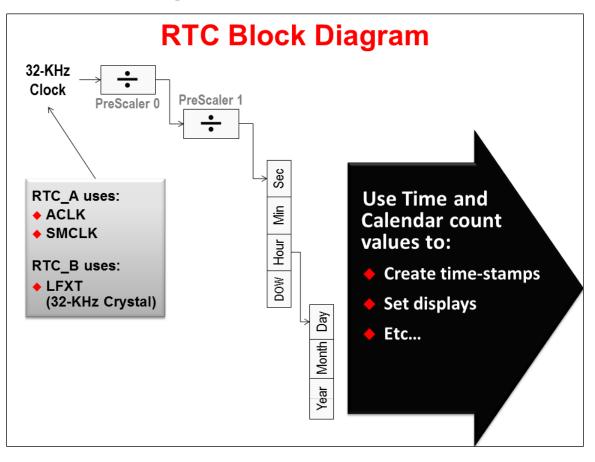

The Real-Time Clock (RTC) peripheral is a sophisticated timer that keeps track of Calendar, Month, and Time information. It operates in Binary or BCD modes; whichever is most useful for your application.

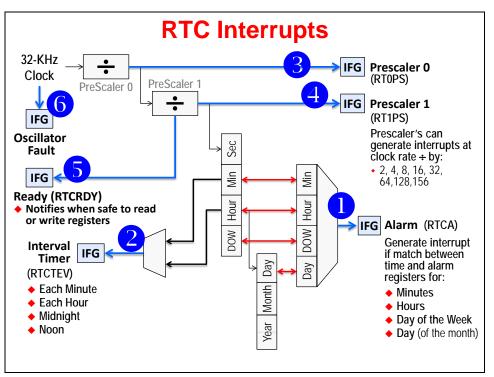

The RTC affords you the ability to set Calendar/Time based Alarms (i.e. Interrupts).

This peripheral is extremely power sensitive and operates in many low-power modes. In fact, on the MSP430FR5969, it even operates in LPM3.5 mode.

# **Learning Objectives**

- Describe the architecture of the Real-Time Clock module.

- Learn to set alarms/interrupts for the RTC.

# **Chapter Topics**

| Real-Time Clock (RTC)8     | 3-1 |

|----------------------------|-----|

| What is a Real-Time Clock? | 3-3 |

| How Does the RTC Work?     |     |

| RTC Interrupts             |     |

| Programming the RTC        | 3-6 |

| Additional Considerations  | 3-7 |

| Summary                    | 3-8 |

# What is a Real-Time Clock?

# How Does the RTC Work?

# **RTC Block Diagram**

### **RTC Interrupts**

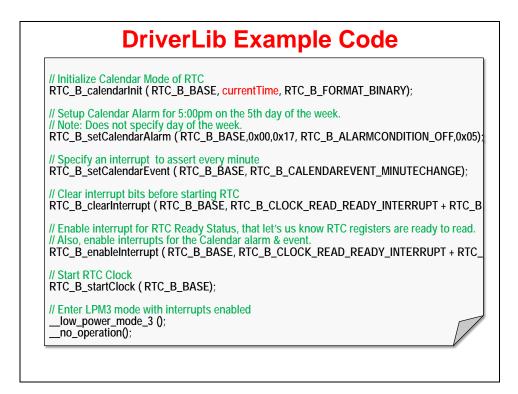

## **Programming the RTC**

| Setting RTC using GRACE         |                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Setting RIC using GRAA          | <ul> <li>Grace supports:</li> <li>Devices <ul> <li>F2xx, G2xx</li> <li>FR5xx</li> </ul> </li> <li>RTC use cases <ul> <li>Calendar mode only</li> </ul> </li> <li>BCD or Hex modes</li> <li>Creates interrupt handler template: <ul> <li>Alarm</li> <li>Events</li> <li>Ready</li> <li>Osc Fault</li> </ul> </li> </ul> |  |  |  |  |

| Grace RTC_B 💥 Clock System (CS) |                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

### **Additional Considerations**

# Additional Features Using RTC in LPM3.5 Mode All RTC's work in LPM3 mode Since <u>RTC B</u> and <u>RTC C</u> can directly access the LF crystal, they can operate in the "3.5" low-power mode LPM3.5 provides the lowest possible power dissipation with RTC wake-up capability Machine Mathematical Structure (as a structure) Priver Library function provides easy access to this hardware feature Mathematical Structure (as a structure) Counter mode generates overflow interrupts at 8-, 16-, 24- and 32-bits

| Exercise Caution                                                                                                                                                                                                                       |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| <ul> <li>Clear bit-fields before setting counters and alarms</li> </ul>                                                                                                                                                                |  |  |  |  |  |

| <ul> <li>Prior to setting an alarms, clear all alarm registers, including the<br/>alarm enable (AE) bits</li> </ul>                                                                                                                    |  |  |  |  |  |

| <ul> <li>To prevent potential erroneous alarms when setting time values,<br/>clear the interrupt enable (IE) bits, as well as the AE bits</li> </ul>                                                                                   |  |  |  |  |  |

| <ul> <li>Writes to count registers takes effect immediately. Note that the RTC<br/>clock is stopped during the write and both pre-scale registers are<br/>reset. This could result in losing up to 1 second during a write.</li> </ul> |  |  |  |  |  |

| <ul> <li>Invalid time and alarm settings are not validated or handled<br/>via hardware (measure twice, program once)</li> </ul>                                                                                                        |  |  |  |  |  |

| <ul> <li>Reading Registers</li> </ul>                                                                                                                                                                                                  |  |  |  |  |  |

| <ul> <li>Care should be taken when reading (or writing) RTC<br/>time/calendar/prescale registers so that your actions do not occur<br/>during counter transitions</li> </ul>                                                           |  |  |  |  |  |

| These options can help to prevent erroneous results:                                                                                                                                                                                   |  |  |  |  |  |

| <ol> <li>Let the RTC Ready (RTCRDY) interrupt you just after an update – you'll<br/>have ~1 sec before the next update</li> </ol>                                                                                                      |  |  |  |  |  |

| 2. Check the RTCRDY bit before reading or writing the registers                                                                                                                                                                        |  |  |  |  |  |

| 3. Read the registers multiple times and take the majority vote                                                                                                                                                                        |  |  |  |  |  |

| 4. Hold the RTC before reading or writing any registers                                                                                                                                                                                |  |  |  |  |  |

# Summary

| RTC Comparison                   |                                           |                                                         |                                  |                                                                      |  |  |

|----------------------------------|-------------------------------------------|---------------------------------------------------------|----------------------------------|----------------------------------------------------------------------|--|--|

|                                  | Feature                                   | RTC_A                                                   | RTC_B                            | RCT_C                                                                |  |  |

|                                  | Highlights                                | 32-bit Counter<br>Mode                                  | LPM3.5,<br>Calendar Mode<br>Only | Protection Plus<br>Improved Calibration<br>& Compensation            |  |  |

| Modes                            | Calendar Mode with<br>Programmable Alarms | Yes                                                     | Yes                              | Yes                                                                  |  |  |

|                                  | Counter Mode                              | Yes                                                     | No                               | Device-dependent                                                     |  |  |

|                                  | Input Clocks                              | ALCK, SMCLK                                             | 32-kHz crystal                   | 32-kHz crystal                                                       |  |  |

|                                  | LPM3.5 Support                            | No                                                      | Yes                              | Yes                                                                  |  |  |

| Compensation<br>&<br>Calibration | Offset Calibration<br>Register            | Yes                                                     | Yes                              | Yes                                                                  |  |  |

|                                  | Temperature<br>Compensation Register      | No                                                      | No                               | Yes                                                                  |  |  |

|                                  | Temperature<br>Compensation               | With software, manipulating<br>offset calibration value |                                  | With software using separate<br>temperature compensation<br>register |  |  |

|                                  | Calibration and<br>Compensation Period    | 64 min                                                  | 60 min                           | 1 min                                                                |  |  |

| Features                         | BCD to Binary<br>Conversion               | Integrated for<br>Calendar Mode                         |                                  |                                                                      |  |  |

|                                  | Event/Tamper Detect<br>With Time Stamp    | No                                                      | No                               | Device-dependent                                                     |  |  |

|                                  | Password Protected<br>Calendar Registers  | No                                                      | No                               | Yes                                                                  |  |  |