|

|

Non-Volatile Storage driver for CC13XX/CC26XX devices.

When writing or erasing flash, interrupts must be disabled to avoid executing code in flash while the flash is being reprogrammed. This constraint is handled by the driver. Application code does not need to safeguard against this.

Additionally, to avoid extremely large interrupt latencies that would be incurred if entire blocks were written with interrupts disabled, block writes to flash are broken into multiple smaller sizes.

Even with this scheme in place, latencies of roughly 64 microseconds will be incurred while flash is being written to.

A similar caveat applies to flash erase operations. Erasing an entire flash sector (the minimal amount that can be erased at a time) can take roughly 8 milliseconds. This entire operation must be performed with interrupts disabled. Here again, this requirement is met internally by the driver and flash region erases are performed one sector at a time to minimize this significant latency impact.

Care must be taken by the user to not perform flash write or erase operations during latency critical phases of an application. See the NVS_lock() and NVS_unlock() API descriptions for more information.

On CC13XX & CC26XX memory rows can be 128 or 256 bytes in length; refer to the device datasheet for the exact size. A maximum of 83 write operations can be performed on a memory row. Once the limit is reached, the row must be erased before it is written to again. It is the developer's responsibility to ensure that this limit is not exceeded in their applications. The developer may also opt to use the third party SPIFFS library implementation supported by TIRTOS which does track writes.

A write "Scoreboard" can be enabled in this driver; the scoreboard keeps track of how many times a page has been written to. It is provided as a debug tool to ensure the 83 write limit is not exceeded. If a page is written to more than 83 times, the NVSCC26XX driver will spin forever. Each byte in the scoreboard corresponds to a memory page in the NVS region. The byte is incremented when the memory is written to & set to 0 when erased.

To enable the "scoreboard" the "NVSCC26XX_INSTRUMENTED" symbol must be defined when the driver is compiled. Three new fields are added to the NVSCC26XX_HWAttrs structure:

When configured correctly, the scoreboard can be viewed in a memory browser.

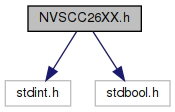

#include <stdint.h>#include <stdbool.h>

Go to the source code of this file.

Data Structures | |

| struct | NVSCC26XX_HWAttrs |

| NVSCC26XX hardware attributes. More... | |

| struct | NVSCC26XX_Object |

Macros | |

| #define | NVSCC26XX_STATUS_LOW_VOLTAGE (NVS_STATUS_RESERVED - 1) |

| Error status code returned by NVS_erase(), NVS_write(). More... | |

Variables | |

| const NVS_FxnTable | NVSCC26XX_fxnTable |

| #define NVSCC26XX_STATUS_LOW_VOLTAGE (NVS_STATUS_RESERVED - 1) |

Error status code returned by NVS_erase(), NVS_write().

This error status is returned if the system voltage is too low to safely perform the flash operation. Voltage must be 1.5V or greater.

| const NVS_FxnTable NVSCC26XX_fxnTable |