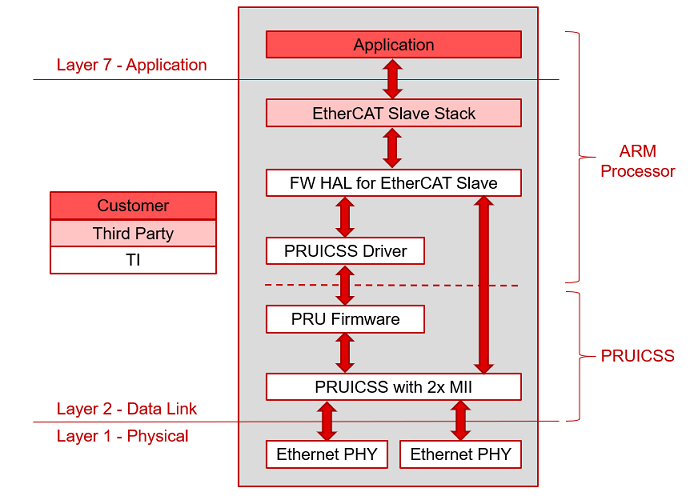

This software is designed for the TI SoCs with PRU-ICSS IP to enable customers add EtherCAT Slave protocol support to their system. It implements EtherCAT Slave Controller(ESC) Layer 2 functionality with two MII ports (one IN and one OUT port per PRU-ICSS) in accordance with ETG.1000.4 Data Link Layer protocol specification. This provides EtherCAT ASIC like functionality integrated into TI SoCs.

EtherCAT firmware for PRU-ICSS is a black box product maintained by TI. EtherCAT Slave FWHAL(Firmware and Hardware Abstraction Layer) allows loading and running the EtherCAT firmware and acts as an interface with ESC firmware. FWHAL implements the key interface between EtherCAT Slave Controller Emulation firmware and EtherCAT stack.

SysConfig can be used to configure things mentioned below:

| Record ID | Details | Workaround |

|---|---|---|

| PINDSW-47 | Multiple FMMU access in a single datagram to a slave for process data using LRD/LWR commands | Use LRW instead of LRD/LWR |

| PINDSW-72 | PDI/PD watchdog counter incremented by 1 whenever PDI/PD watchdog is disabled | None |

| PINDSW-74 | LRD access on unused registers increment WKC - no register protection while using LRD | None |

| PINDSW-141 | LRW access to non-interleaved input and output process data of multiple slaves does not work. SOEM accesses slaves in LRW mode this way | Use LRD/LWR for process data access or use more optimal interleaved access for process data access from Master (TwinCAT way) |

| PINDSW-2204 | Frames with no SFD not counted as errors if received on reverse path | None |

| PINDSW-2360 | System time of next Sync0 pulse register (0x990:0x993) is not instantaneous, resulting in read of incorrect value if read immediately after sync pulse | None |

| PINDSW-5135 | Read permissions and byte level write permissions for RW type commands are not checked | None |

For more details, please see the EtherCAT Slave Errata document.

| Folder/Files | Description |

|---|---|

| ${SDK_INSTALL_PATH}/examples/industrial_comms | |

| ethercat_slave_beckhoff_ssc_demo | EtherCAT Slave Example based on Beckhoff SSC |

| ${SDK_INSTALL_PATH}/source/industrial_comms/ethercat_slave | |

| icss_fwhal/firmware/m_v2.3 | Firmware for the PRU cores in PRU-ICSS. Firmware Version : 5.5.1 |

| icss_fwhal/lib/ | FWHAL library for EtherCAT Slave |

| icss_fwhal/tiescbsp.h | FWHAL interface file |

| beckhoff_stack/esi | ESI XML file for Beckhoff Slave Stack Code(SSC) based example |

| beckhoff_stack/patch | Patch file for Beckhoff Slave Stack Code(SSC) sources |

| beckhoff_stack/stack_hal | Stack adaptation APIs for Beckhoff Slave Stack Code(SSC) |

| beckhoff_stack/stack_sources | Folder where Beckhoff Slave Stack Code(SSC) sources should be copied. Stack sources are not packaged in the SDK |

Please see APIs for Ethercat Slave FWHAL for API documentation.

It is recommended to use these FWHAL APIs in the stack adaptation files. For example, see ${SDK_INSTALL_PATH}/source/industrial_comms/ethercat_slave/beckhoff_stack/stack_hal, which contains the stack adaptation APIs for Beckhoff Slave Stack Code(SSC).

EtherCAT Slave Controller firmware generates the following interrupts.

8 Host Interrupts (Host Interrupts 2 through 9) are exported from the PRU_ICSSG internal INTC for signaling the device level interrupt controllers. PRU_EVTOUT0 to PRU_EVTOUT7 correspond to these eight interrupts in the following table. Please check PRUICSS Interrupt Controller section for more details.

| Name | Host Interrupt | Description |

|---|---|---|

| DC SYNC0 OUT | PRU_EVTOUT1 | Used in DC mode for syncing the application |

| DC SYNC1 OUT | PRU_EVTOUT2 | Used in DC mode for syncing the application |

| PDI Interrupt | PRU_EVTOUT3 | AL event/PDI interrupt to host stack |

| ESC Command Acknowledgement | PRU_EVTOUT4 | ESC firmware command completion acknowledgement to Host |

TI EtherCAT Slave Controller Register List contains descriptions of the registers in TI's EtherCAT Slave Controller implementation.

TI EtherCAT Slave Controller Exceptions lists the exceptions TI's EtherCAT Slave Controller implementation when compared with ET1100 ASIC. Please note that TI ESC is a 2 port EtherCAT slave and it does not support E-bus interface and all the corresponding register fields are not implemented.

Please refer to below documents to understand more about EtherCAT slave on TI platforms and EtherCAT slave protocol specifications.

| Document | Description |

|---|---|

| EtherCAT on Sitara Processors | Application note by TI on the EtherCAT slave implementation on TI's Sitara Processors. |

| PRU-ICSS EtherCAT Slave Troubleshooting Guide | This troubleshooting guide is intended to provide guidance on how to set up and debug the EtherCAT slave implemented on TI's Sitara processors. |

| EtherCAT ESC Datasheet Section 1 - Technology | Section 1 of Beckhoff's EtherCAT Slave Controller (ESC) documentation which describes basic EtherCAT technology. |

| EtherCAT ESC Datasheet Section 2 - Register Description | Section 2 of Beckhoff's EtherCAT Slave Controller (ESC) documentation which contains ESC register descriptions. |

| Application Note ET9300 (EtherCAT Slave Stack Code) | This contains details on how to start EtherCAT Slave development with Slave Stack Code. |

| EtherCAT Slave Implementation Guide from EtherCAT Technology Group | This contains information on how to develop an EtherCAT slave implementation. |

| EtherCAT Slave Design Quick Guide from Beckhoff | This contains information on modifying PDO when using Beckhoff SSC Tool for code generation. |