# EDMA3 Driver

# User Guide

July 2009

Anuj Aggarwal

Document Version 01.10.00.XX

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI

#### Mailing Address: Texas Instruments Post Office Box 655303, Dallas, Texas 75265

#### Copyright © 2009, Texas Instruments Incorporated

#### LICENSE

This work is licensed under the Creative Commons Attribution-Share Alike 3.0 United States License. To view a copy of this license, visit <u>http://creativecommons.org/licenses/by-sa/3.0/us/</u> or send a letter to Creative Commons, 171 Second Street, Suite 300, San Francisco, California, 94105, USA.

# **Read This First**

#### About This Manual

This User's Manual serves as a software programmer's handbook for working with the **EDMA3 Driver Version 01.10.00.XX.** This manual provides necessary information regarding how to effectively install, build and use **EDMA3 Driver** in user systems and applications.

This manual provides details regarding how the **EDMA3 Driver** is Architected, its composition, its functionality, the requirements it places on the hardware and software environment where it can be deployed, how to customize/configure it to specific requirements, how to leverage the supported run-time interfaces in user's own application etc.,

This manual also provides supplementary information regarding steps to be followed for proper installation/ un-installation of the EDMA3 Driver. Also included are appendix sections on related Glossary, Web sites and Pointers for gathering further information on the EDMA3 Driver.

### Terms and Abbreviations

Add any longer explanations for terms before the table.

Add any abbreviations and short explanations to the table.

| Term/Abbreviation | Description                                                                                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EDMA              | Enhanced Direct Memory Access                                                                                                                                                         |

| EDMA3 Controller  | Consists of the EDMA3 channel controller (EDMA3CC) and EDMA3 transfer memory access controller(s) (EDMA3TC). Is referred to as EDMA3 in this document.                                |

| DMA               | Direct Memory Access                                                                                                                                                                  |

| QDMA              | Quick DMA                                                                                                                                                                             |

| ТСС               | Transfer Completion Code (basically Interrupt Channel)                                                                                                                                |

| ISR               | Interrupt Service Routine                                                                                                                                                             |

| CC                | Channel Controller                                                                                                                                                                    |

| тс                | Transfer Controller                                                                                                                                                                   |

| RM                | Resource Manager                                                                                                                                                                      |

| TR                | Transfer Request.<br>A command for data movement that is issued from the<br>EDMA3CC to the EDMA3TC. A TR includes source and<br>destination addresses, counts, indexes, options, etc. |

#### Notations

Explain any special notations or typefaces used (such as for API guides, special typefaces for functions, variables, etc.)

#### Information about Cautions and Warnings

This book may contain cautions and warnings.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

#### **Related Documentation**

- □ EDMA3 Channel Controller (TPCC), version 3.0.2

- □ EDMA3 Transfer Controller (TPTC), version 3.0.1

### Trademarks

The TI logo design is a trademark of Texas Instruments Incorporated. All other brand and product names may be trademarks of their respective companies.

# **Revision History**

| Date                  | Author           | <b>Revision History</b>                                                                                                                                                                                                                                                                                                                                                                                                                                  | Version     |

|-----------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| July 9, 2009          | Anuj<br>Aggarwal | <ul> <li>a) ECN# TIDSP00012004 (Migration to new BSD license) and TIDSP00011985 (Addition of new API EDMA3_DRV_disableLogicalChannel API in EDMA3 Driver) implemented.</li> <li>b) IRs# SDOCM00058027, SDOCM00058147 and SDOCM00058401 fixed.</li> <li>See release notes for more information.</li> </ul>                                                                                                                                                | 01.10.00.01 |

| May 11, 2009          | Anuj<br>Aggarwal | a) Add support for new platforms: C6748, OMAPL138, DRA44x and DRX45x.                                                                                                                                                                                                                                                                                                                                                                                    | 01.07.00.01 |

| November 4,<br>2008   | Anuj<br>Aggarwal | <ul><li>a) Added support for new platforms.</li><li>b) IR SDOCM00049778 is fixed.</li><li>See release notes for more information.</li></ul>                                                                                                                                                                                                                                                                                                              | 01.06.00.01 |

| March 20,<br>2008     | Anuj<br>Aggarwal | <ul> <li>a) Added support for new platforms.</li> <li>b) MRs DPSP00010071, DPSP00010187,<br/>DPSP00010479 and DPSP00010480 are<br/>fixed.</li> <li>See release notes for more information.</li> </ul>                                                                                                                                                                                                                                                    | 1.05.00.01  |

| January 28,<br>2008   | Anuj<br>Aggarwal | <ul> <li>a) Header files modified to have extern "C" declarations.</li> <li>b) Implemented ECNs DPSP00009815 &amp; DPSP00010035.</li> </ul>                                                                                                                                                                                                                                                                                                              | 1.04.00.01  |

| January 9,<br>2008    | Anuj<br>Aggarwal | <ul> <li>a) MR# DPSP00009788 has been fixed in<br/>this release. See Release Notes for more<br/>information.</li> </ul>                                                                                                                                                                                                                                                                                                                                  | 1.03.01.01  |

| October 21,<br>2007   | Anuj<br>Aggarwal | <ul> <li>a) C6452 support has been added in this release. Now C6452 applications can also be built in the RTSC environment.</li> <li>b) All the CCS PJT files now come under two flavors: one for the RTSC environment and the other for the non-RTSC environment.</li> <li>c) IOCTL interface has been added in the EDMA3 Driver.</li> <li>d) MRs DPSP00009099, DPSP00009190 and DPSP00009213 Fixed. See Release Notes for more information.</li> </ul> | 1.03.00.01  |

| September 28,<br>2007 | Anuj<br>Aggarwal | <ul> <li>a) Added support for DM6467 platform.</li> <li>b) MRs DPSP00009060, DPSP00009063,<br/>DPSP00009093 and DPSP00009100<br/>Fixed. See Release Notes for more<br/>information.</li> </ul>                                                                                                                                                                                                                                                           | 1.02.00.01  |

| September 14,<br>2007 | Anuj<br>Aggarwal | <ul><li>a) Moved the platform specific configuration<br/>to the Resource Manager.</li><li>b) Modified the chaining API.</li></ul>                                                                                                                                                                                                                                                                                                                        | 1.01.00.01  |

|               |                  | c) Divided the sample app into sample<br>initialization library and the standalone<br>sample application.                                                                                                                                                                        |            |

|---------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| July 11, 2007 | Anuj<br>Aggarwal | a) Modified the DSP/BIOS version number.<br>b) Modified the Driver directory structure as<br>per RTSC standard.                                                                                                                                                                  | 1.00.00.03 |

| June 18, 2007 | Anuj<br>Aggarwal | a) Made the EDMA3 package RTSC compliant.                                                                                                                                                                                                                                        | 1.00.00.02 |

| May 14, 2007  | Anuj<br>Aggarwal | a) MR# DPSP00007858 (Issue in EDMA3<br>DRV causes false missed events) Fixed.                                                                                                                                                                                                    | 1.0.0.1    |

| May 9, 2007   | Anuj<br>Aggarwal | <ul> <li>a) MR# DPSP00007800 (Result of resource 1.0.0 allocation is over-written by the semaphore release result in EDMA3 Resource Manager) Fixed.</li> <li>b) MR# DPSP00007803 (Exit from EDMA3_RM_allocContiguousResource () in case of error is incorrect) Fixed.</li> </ul> |            |

| Apr 23, 2007  | Anuj<br>Aggarwal | <ul> <li>a) New APIs to support POLL mode provided.</li> <li>b) API to set CC Register provided.</li> <li>c) Sample application made generic and more test cases added.</li> </ul>                                                                                               |            |

| Mar 23, 2007  | Anuj<br>Aggarwal | a) DMA/QDMA channel event missed issue fixed.                                                                                                                                                                                                                                    | 0.3.1      |

| Mar 6, 2007   | Anuj<br>Aggarwal | a) Renamed EDMA3_DVR to EDMA3_DRV.<br>b) IPR bit clearing in RM ISR issue fixed.<br>c) Sample application made generic.                                                                                                                                                          | 0.3.0      |

| Jan 16, 2007  | Anuj<br>Aggarwal | Critical section handling code modification.<br>Uses semaphore and interrupts disabling<br>mechanism for resources sharing.                                                                                                                                                      | 0.2.2      |

| Nov 14, 2006  | Anuj<br>Aggarwal | Made EDMA3 Driver OS Independent. Also, more run time configuration is possible now.                                                                                                                                                                                             | 0.2.1      |

# Contents

| About This Manual       iii         This manual also provides supplementary information regarding steps to be followed for proper installation / un-installation of the EDMA3 Driver. Also included are appendix sections on related Glossary, Web sites and Pointers for gathering further information on the EDMA3 Driver. Terms and Abbreviations.         included are appendix sections on related Glossary, Web sites and Pointers for gathering further information on the EDMA3 Driver. Terms and Abbreviations.       iv         Notations       v       v         Refracted Documentation       vi         Trademarks vi       vi         Revision History       vii         Contents.       ix <b>EDMA3 Driver Introduction</b> 0-1-1         1.1       Overview       0-1-2         1.1.1       System Partitioning       0-1-2         1.1.2       Supported Services       0-16         Installation Guide       1-2-4       2.2         2.2       Development Tools Environment(s)       1-2-4         2.3       Installation guide       1-2-5         2.3.1       Installation guide       1-2-5         2.3.2       Un-installation       1-2-6         2.4.4       Build Options       1-2-6         2.4.1       Build Options       1-2-7         3.2.2       EDMA3_DR | Read T  | his Fi | rst                                     | iii |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|-----------------------------------------|-----|

| This manual also provides supplementary information regarding steps to be followed for proper installation/ un-installation of the EDMA3 Driver. Also included are appendix sections on related Glossary, Web sites and Pointers for gathering further information on the EDMA3 Driver. Terms and Abbreviations.         iv       Notations       v         Notations       v       Notations         v       Notations       v         Related Documentation       vi       vi         Trademarks vi       Revision History.       vii         Contents       xi       xi <i>EDMA3 Driver</i> Introduction       0-1-1       1.1         1.1       Overview       0-1-2         1.1.1       System Partitioning       0-1-2         1.1.1       System Partitioning       0-1-2         1.1.1       System Partitioning       1-2-4         2.2       Development Tools       1-2-4         2.3       Installation Guide       1-2-4         2.4       Development Tools       1-2-4         2.3       Installation       1-2-5         2.3.1       Installation guide       1-2-5         2.3.2       Un-installation       1-2-4         2.4       Build       1-2-7         Rebevelopment Tools       1-2-4                                                                            |         |        |                                         |     |

| followed for proper installation/ un-installation of the EDMA3 Driver. Also included are appendix sections on related Glossary, Web sites and Abbreviations.iii         gathering further information on the EDMA3 Driver. Terms and Abbreviations.iii         Terms and Abbreviations         w         Notations         v         Information about Cautions and Warnings         v         Related Documentation         vi         Trademarks vi         Revision History         Revision History         vii         Contents         ix         Tables         xii <i>EDMA3 Driver</i> Introduction         0-1-2         1.1.1         Overview         0-1-2         1.1.2         Supported Services         0-1-2         1.1.2         Supported Services         1.2.1         Development Tools Environment(s)         1-2.2         2.3         Installation guide         1-2.4         2.1         Development Tools         1.2.2         Development Tools         1.2.3         Installation guide                                                                                                                                                                                                                                                                    |         |        |                                         |     |

| included are appendix sections on related Glossary, Web sites and Pointers for<br>gathering further information on the EDMA3 Driver. Terms and Abbreviations<br>iv<br>Notations v<br>Information about Cautions and Warnings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |        |                                         |     |

| gathering further information on the EDMA3 Driver. Terms and Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |        |                                         |     |

| Terms and Abbreviations       iv         Notations       v         Information about Cautions and Warnings       v         Related Documentation       vi         Trademarks vi       vi         Revision History       vii         Contents       ix         Tables       ix         Tables       xi <i>EDMA3 Driver</i> Introduction       0-1-1         1.1       Overview       0-1-2         1.1.1       System Partitioning       0-1-2         1.1.1       System Partitioning       0-1-2         1.1.2       Supported Services       0-1-6         Installation Guide       1-2-4         2.1       Development Tools Environment(s)       1-2-4         2.2       Development Tools       1-2-4         2.3       Installation guide       1-2-5         2.3.1       Installation       1-2-5         2.3.2       Un-installation       1-2-6         2.4.1       Build       1-2-6         2.4.1       Build Options       1-2-7         Run-Time Interfaces/Integration Guide       2-A-1         3.2.2       EDMA3_DRV_GblConfigParams       2-A-13         3.2.1       EDMA3_DRV                                                                                                                                                                                            |         |        |                                         |     |

| Notations       v         Information about Cautions and Warnings.       v         Related Documentation       vi         Trademarks       vi         Revision History       vii         Contents       ix         Tables       xi         EDMA3 Driver Introduction       0-1-1         1.1       Overview       0-1-2         1.1.1       System Partitioning       0-1-2         1.1.2       Supported Services       0-1-6         Installation Guide       1-2-1         2.1       Component Folder       1-2-2         2.2       Development Tools Environment(s)       1-2-4         2.3       Installation guide       1-2-5         2.3.1       Installation and Usage Procedure.       1-2-5         2.3.2       Un-installation       1-2-6         2.4       Build       1-2-6         2.4.1       Build Options       1-2-7         Run-Time Interfaces/Integration Guide       2-A-13         3.2.1       EDMA3_DRV_InstanceInitConfig       2-A-13         3.2.2       EDMA3_DRV_InstanceInitConfig       2-A-13         3.2.3       EDMA3_DRV_ChainOptions       2-A-22         3.2.4       EDMA3_DRV_MiscPa                                                                                                                                                               |         |        |                                         |     |

| Information about Cautions and Warnings       v         Related Documentation       vi         Trademarks vi       vii         Revision History       vii         Contents       ix         Tables       xi <i>EDMA3 Driver</i> Introduction       0-1-1         1.1       Overview       0-1-2         1.1.1       System Partitioning       0-1-2         1.1.2       Supported Services       0-1-6         Installation Guide       1-2-1         2.1       Component Folder       1-2-2         2.2       Development Tools Environment(s)       1-2-4         2.3       Installation guide       1-2-5         2.3.1       Installation and Usage Procedure.       1-2-5         2.3.2       Un-installation       1-2-7         Run-Time Interfaces/Integration Guide       2-A-13         3.2.1       EDMA3_DRV_EdblConfigParams       2-A-13         3.2.1       EDMA3_DRV_InitConfig       2-A-13         3.2.2       EDMA3_DRV_InitConfig       2-A-14         3.2.3       EDMA3_DRV_ChainOptions       2-A-20         3.2.4       EDMA3_DRV_PaRAMRegs       2-A-21         3.2.7       EDMA3_DRV_PaRAMRegs       2-A-24                                                                                                                                                        |         |        |                                         | IV  |

| Related Documentation       vi         Trademarks vi       vii         Revision History       vii         Contents       ix         Tables       xi         EDMA3 Driver Introduction       0-1-1         1.1       Overview       0-1-2         1.1.1       System Partitioning       0-1-2         1.1.1       System Partitioning       0-1-2         1.1.2       Supported Services       0-1-6         Installation Guide       1-2-1         2.1       Component Folder       1-2-2         2.2       Development Tools Environment(s)       1-2-4         2.3       Installation guide       1-2-5         2.3.1       Installation       1-2-5         2.3.2       Un-installation       1-2-5         2.4       Build       1-2-5         2.4       Build Options       1-2-7         Run-Time Interfaces/Integration Guide       2-A-13         3.2.1       EDMA3_DRV_EdblConfigParams       2-A-13         3.2.2       EDMA3_DRV_InstanceInitConfig       2-A-14         3.2.3       EDMA3_DRV_ChainOptions       2-A-20         3.2.4       EDMA3_DRV_PaRAMRegs       2-A-21         3.2.7       <                                                                                                                                                                             |         |        | •                                       |     |

| Trademarks viviiRevision History.viiContents.ixTables.xiEDMA3 Driver Introduction.0-1-11.1Overview0-1-21.1.1System Partitioning.0-1-21.1.2Supported Services0-1-6Installation Guide.1-2-12.1Component Folder2.2Development Tools Environment(s)1-2-42.3Installation guide2.42.2.1Development Tools2.3Installation and Usage Procedure.1-2-52.3.1Installation and Usage Procedure.1-2-52.3.2Un-installation2.4Build2.4Build2.52.3.22.4Build3.2.1EDMA3_DRV_Integration Guide3.2.2EDMA3_DRV_InstanceInitConfig.2.3EDMA3_DRV_InitCorfig3.4EDMA3_DRV_PaRAMRegs3.2.7EDMA3_DRV_InitCorfig3.3API Specification3.4Teration3.3.2Configuration3.4Teration3.5.4EDMA3 DRV_Initialization3.5.1EDMA3 Driver Creation3.5.1EDMA3 Driver Creation2.4.733.5.1EDMA3 Driver Creation2.4.733.5.1EDMA3 Driver Creation2.4.733.5.1EDMA3 Driver Creation2.4.733.5.1EDMA3 Driver Creation2.4.733.5.1                                                                                                                                                                                                                                                                                                                                                                                                                 | Deleted |        | bout Cautions and warnings              | V   |

| Revision HistoryviiContentsixTablesxiEDMA3 Driver Introduction0-1-11.1Overview0.1.21.1.1 System Partitioning1.1.1 System Partitioning0-1-21.1.2 Supported Services0-1-6Installation Guide1-2-12.1Component Folder2.2Development Tools Environment(s)1.2.42.2.1 Development Tools2.3Installation guide2.42.3.1 Installation guide2.52.3.2 Un-installation2.4Build2.4Build Options2.4Build Options2.4Symbolic Constants and Enumerated Data types2.42.4.1 Build Options3.2.1 EDMA3_DRV_GblConfigParams2.42.4.133.2.2 EDMA3_DRV_InstanceInitConfig2.3.3 APIV_Septication3.4 EDMA3_DRV_MiscParam3.2.4 EDMA3_DRV_MiscParam3.2.5 EDMA3_DRV_PaRAMRegs2.4.203.2.6 EDMA3_DRV_PaRAMRegs2.7 EDMA3_DRV_Erduperiority2.4.213.3 Control2.4.253.3 Control3.4 Termination2.4.263.3 Control3.4 Termination2.4.273.3 Control3.4 Termination2.4.273.3.4 Termination2.4.273.5.1 EDMA3 Driver Creation2.4.73                                                                                                                                                                                                                                                                                                                                                                                                    |         |        |                                         | VI  |

| ContentsixTablesxiEDMA3 Driver Introduction0-1-11.1Overview0-1-21.1.1System Partitioning0-1-21.1.2Supported Services0-1-6Installation Guide1-2-12.1Component Folder1-2-22.2Development Tools Environment(s)1-2-42.3Installation guide1-2-52.3.1Installation quide1-2-52.3.2Un-installation1-2-52.4Build1-2-62.4.1Build Options1-2-7Run-Time Interfaces/Integration Guide2-A-13.2.1EDMA3_DRV_GblConfigParams2-A-133.2.2EDMA3_DRV_GblConfigParams2-A-163.2.3EDMA3_DRV_MiscParam2-A-193.2.4EDMA3_DRV_MiscParam2-A-203.2.5EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_ParAMRegs2-A-213.2.7EDMA3_DRV_ParAMRegs2-A-213.2.7EDMA3_DRV_ParAMRegs2-A-213.2.7EDMA3_DRV_ParAMRegs2-A-243.3API Specification2-A-243.3Control2-A-243.3Control2-A-273.3Control2-A-273.3Control2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |        |                                         |     |

| Tables.xi <i>EDMA3 Driver</i> Introduction.0-1-11.1Overview0-1-21.1.1System Partitioning0-1-21.1.2Supported Services0-16Installation Guide.1-2-12.1Component Folder1-2-22.2Development Tools Environment(s)1-2-42.3Installation guide1-2-52.3.1Installation and Usage Procedure1-2-52.3.2Un-installation1-2-62.4.1Build1-2-62.4.1Build Options1-2-7Run-Time Interfaces/Integration Guide2-A-13.2.1EDMA3_DRV_GblConfigParams2-A-133.2.2EDMA3_DRV_InitConfig2-A-133.2.3EDMA3_DRV_ChainOptions2-A-133.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_PaRAMRegs2-A-223.3API Specification2-A-233.4Termination2-A-233.5API Specification2-A-243.3Control2-A-233.4Termination2-A-683.4EDMA3 Driver Initialization2-A-773.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |        | 1                                       |     |

| EDMA3 Driver Introduction0-1-11.1Overview0-1-21.1.1System Partitioning0-1-21.1.2Supported Services0-1-6Installation Guide1-2-12.1Component Folder1-2-22.2Development Tools Environment(s)1-2-42.3Installation guide1-2-52.3.1Installation and Usage Procedure1-2-52.3.2Un-installation1-2-62.4Build1-2-62.4.1Build Options1-2-7Run-Time Interfaces/Integration Guide2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-133.2.2EDMA3_DRV_InitConfig2-A-133.2.3EDMA3_DRV_ChainOptions2-A-193.2.4EDMA3_DRV_ChainOptions2-A-203.2.5EDMA3_DRV_ChainOptions2-A-213.2.7Zortification2-A-233.3API Specification2-A-223.3.4Teretion2-A-233.3.1Creation2-A-233.3.4Termination2-A-233.3.4Termination2-A-243.3.1Creation2-A-273.3.4Termination2-A-283.4EDMA3 Driver Initialization2-A-273.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |        |                                         |     |

| 1.1       Overview       0-1-2         1.1.1       System Partitioning       0-1-2         1.1.2       Supported Services       0-1-16         Installation Guide       1-2-1         2.1       Component Folder       1-2-2         2.2       Development Tools Environment(s)       1-2-4         2.2       Development Tools       1-2-4         2.3       Installation guide       1-2-5         2.3.1       Installation and Usage Procedure       1-2-5         2.3.2       Un-installation       1-2-6         2.4       Build       1-2-7         Run-Time Interfaces/Integration Guide       2-A-1         3.1       Symbolic Constants and Enumerated Data types       2-A-2         3.2       Data Structures       2-A-13         3.2.1       EDMA3_DRV_GblConfigParams       2-A-13         3.2.2       EDMA3_DRV_InstanceInitConfig       2-A-16         3.2.3       EDMA3_DRV_MiscParam       2-A-20         3.2.4       EDMA3_DRV_MiscParam       2-A-21         3.2.7       EDMA3_DRV_MiscParam       2-A-21         3.2.7       EDMA3_DRV_PaRAMRegs       2-A-21         3.2.7       EDMA3_DRV_PaRAMRegs       2-A-24         3.3.1                                                                                                                                      |         |        |                                         |     |

| 1.1.1System Partitioning0-1-21.1.2Supported Services0-1-6Installation Guide1-2-12.1Component Folder1-2-22.2Development Tools Environment(s)1-2-42.3Installation guide1-2-52.3.1Installation and Usage Procedure1-2-52.3.2Un-installation1-2-52.3.4Build1-2-62.4Build1-2-7Run-Time Interfaces/Integration Guide2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_InstanceInitConfig2-A-163.2.3EDMA3_DRV_InstanceInitConfig2-A-183.2.4EDMA3_DRV_ChainOptions2-A-203.2.5EDMA3_DRV_PaRAMRegs2-A-213.3API Specification2-A-243.3.1Creation2-A-243.3.2Configuration2-A-243.3.3API Specification2-A-273.3.4Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -       | -      |                                         | -   |

| 1.1.2Supported Services0-1-6Installation Guide1-2-12.1Component Folder1-2-22.2Development Tools Environment(s)1-2-42.3Installation guide1-2-52.3.1Installation and Usage Procedure1-2-52.3.2Un-installation1-2-52.3.3Un-installation1-2-62.4Build1-2-62.4.1Build Options1-2-7Run-Time Interfaces/Integration Guide2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-163.2.2EDMA3_DRV_InitConfig2-A-163.2.3EDMA3_DRV_MiscParam2-A-193.2.4EDMA3_DRV_MiscParam2-A-203.2.6EDMA3_DRV_PaRAMRegs2-A-213.3API Specification2-A-243.3.1Creation2-A-243.3.2Configuration2-A-243.3.4Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.1     |        |                                         |     |

| Installation Guide1-2-12.1Component Folder1-2-22.2Development Tools Environment(s)1-2-42.2.1Development Tools1-2-42.3Installation guide1-2-52.3.1Installation and Usage Procedure1-2-52.3.2Un-installation1-2-52.4Build1-2-62.4.1Build Options1-2-7Run-Time Interfaces/Integration Guide2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-163.2.3EDMA3_DRV_InitConfig2-A-183.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_ChainOptions2-A-203.4FIP Mas_DRV_EvQuePriority2-A-233.3API Specification2-A-243.3.1Creation2-A-273.3.2Configuration2-A-273.3.4Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |        |                                         |     |

| 2.1Component Folder1-2-22.2Development Tools Environment(s)1-2-42.2.1Development Tools1-2-42.3Installation guide1-2-52.3.1Installation and Usage Procedure1-2-52.3.2Un-installation1-2-52.3.4Build1-2-62.4.1Build Options1-2-7 <b>Run-Time Interfaces/Integration Guide</b> 2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-163.2.3EDMA3_DRV_InstanceInitConfig2-A-163.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_ChainOptions2-A-203.2.6EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-243.3.1Creation2-A-243.3.3Configuration2-A-273.3.4Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5.1EDMA3 Driver Creation2-A-723.5.1EDMA3 Driver Creation2-A-72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |        |                                         |     |

| 2.2Development Tools Environment(s)1-2-42.2.1Development Tools1-2-42.3Installation guide1-2-52.3.1Installation and Usage Procedure1-2-52.3.2Un-installation1-2-52.3.4Build1-2-62.4.1Build Options1-2-7Run-Time Interfaces/Integration Guide2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-133.2.2EDMA3_DRV_InitConfig2-A-163.2.3EDMA3_DRV_MiscParam2-A-193.2.4EDMA3_DRV_ChainOptions2-A-203.2.5EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-243.3.1Creation2-A-243.3.3Configuration2-A-273.3.4Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |        |                                         |     |

| 2.2.1Development Tools1-2-42.3Installation guide1-2-52.3.1Installation and Usage Procedure1-2-52.3.2Un-installation1-2-52.3.2Un-installation1-2-52.3.2Un-installation1-2-52.4Build1-2-62.4.1Build Options1-2-7 <b>Run-Time Interfaces/Integration Guide</b> 2.4.1Symbolic Constants and Enumerated Data types2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-163.2.2EDMA3_DRV_InstanceInitConfig2-A-163.2.3EDMA3_DRV_MiscParam2-A-193.2.4EDMA3_DRV_ChainOptions2-A-203.2.5EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-243.3.1Creation2-A-273.3.3Control2-A-293.3.4Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |        |                                         |     |

| 2.3Installation guide1-2-52.3.1Installation and Usage Procedure.1-2-52.3.2Un-installation1-2-52.3.2Un-installation1-2-52.4Build1-2-62.4.1Build Options1-2-7 <b>Run-Time Interfaces/Integration Guide</b> 3.1Symbolic Constants and Enumerated Data types2-A-13.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-163.2.2EDMA3_DRV_InstanceInitConfig2-A-163.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_ChainOptions2-A-203.2.6EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-243.3.1Creation2-A-273.3.2Configuration2-A-273.3.4Termination2-A-683.4EDMA3 Driver Initialization2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.2     |        |                                         |     |

| 2.3.1Installation and Usage Procedure.1-2-52.3.2Un-installation1-2-52.4Build1-2-62.4.1Build Options1-2-7 <b>Run-Time Interfaces/Integration Guide</b> 2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-163.2.2EDMA3_DRV_InstanceInitConfig2-A-163.2.3EDMA3_DRV_InitConfig2-A-183.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_ChainOptions2-A-203.2.6EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-243.3.1Creation2-A-253.3.2Configuration2-A-293.3API Specification2-A-273.3API Flow Diagram2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |        | •                                       |     |

| 2.3.2Un-installation1-2-52.4Build1-2-62.4.1Build Options1-2-7 <b>Run-Time Interfaces/Integration Guide</b> 2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-163.2.2EDMA3_DRV_InstanceInitConfig2-A-163.2.3EDMA3_DRV_InitConfig2-A-183.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_ChainOptions2-A-203.2.6EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-243.3.1Creation2-A-253.3.2Configuration2-A-293.4Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.3     |        |                                         |     |

| 2.4Build1-2-62.4.1Build Options1-2-7Run-Time Interfaces/Integration Guide2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-133.2.2EDMA3_DRV_InstanceInitConfig2-A-163.2.3EDMA3_DRV_InitConfig2-A-183.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_ChainOptions2-A-203.2.6EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-253.3Configuration2-A-273.3Control2-A-293.4Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |        |                                         |     |

| 2.4.1Build Options1-2-7 <b>Run-Time Interfaces/Integration Guide</b> 2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-133.2.2EDMA3_DRV_InstanceInitConfig2-A-163.2.3EDMA3_DRV_InitConfig2-A-183.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_ChainOptions2-A-203.2.6EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-253.3.1Creation2-A-273.3.3Configuration2-A-293.4Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ~ .     |        |                                         |     |

| Run-Time Interfaces/Integration Guide2-A-13.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-133.2.2EDMA3_DRV_InstanceInitConfig2-A-163.2.3EDMA3_DRV_InstanceInitConfig2-A-183.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_ChainOptions2-A-203.2.6EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-253.3.1Creation2-A-273.3.3Configuration2-A-293.4Termination2-A-683.4EDMA3 Driver Initialization2-A-71API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.4     |        |                                         |     |

| 3.1Symbolic Constants and Enumerated Data types2-A-23.2Data Structures2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-133.2.2EDMA3_DRV_InstanceInitConfig2-A-163.2.3EDMA3_DRV_InitConfig2-A-183.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_ChainOptions2-A-203.2.6EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-243.3.1Creation2-A-253.3.2Configuration2-A-293.4Termination2-A-683.4EDMA3 Driver Initialization2-A-71API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | D. T.   |        |                                         |     |

| 3.2Data Structures.2-A-133.2.1EDMA3_DRV_GblConfigParams2-A-133.2.2EDMA3_DRV_InstanceInitConfig2-A-163.2.3EDMA3_DRV_InitConfig2-A-183.2.4EDMA3_DRV_MiscParam2-A-193.2.5EDMA3_DRV_ChainOptions2-A-203.2.6EDMA3_DRV_PaRAMRegs2-A-213.2.7EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-243.3.1Creation2-A-253.3.2Configuration2-A-293.3.4Termination2-A-68EDMA3 Driver Initialization2-A-71API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |        |                                         |     |

| 3.2.1       EDMA3_DRV_GblConfigParams       2-A-13         3.2.2       EDMA3_DRV_InstanceInitConfig       2-A-16         3.2.3       EDMA3_DRV_InitConfig       2-A-18         3.2.4       EDMA3_DRV_MiscParam       2-A-19         3.2.5       EDMA3_DRV_ChainOptions       2-A-20         3.2.6       EDMA3_DRV_PaRAMRegs       2-A-21         3.2.7       EDMA3_DRV_EvtQuePriority       2-A-23         3.3       API Specification       2-A-25         3.3.1       Creation       2-A-25         3.3.2       Configuration       2-A-29         3.3.4       Termination       2-A-68         EDMA3_Driver Initialization       2-A-71         API Flow Diagram       2-A-72         3.5.1       EDMA3 Driver Creation       2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |        | , , , , , , , , , , , , , , , , , , , , |     |

| 3.2.2       EDMA3_DRV_InstanceInitConfig       2-A-16         3.2.3       EDMA3_DRV_InitConfig       2-A-18         3.2.4       EDMA3_DRV_MiscParam       2-A-19         3.2.5       EDMA3_DRV_ChainOptions       2-A-20         3.2.6       EDMA3_DRV_PaRAMRegs       2-A-21         3.2.7       EDMA3_DRV_EvtQuePriority       2-A-23         3.3       API Specification       2-A-24         3.3.1       Creation       2-A-25         3.3.2       Configuration       2-A-29         3.3.4       Termination       2-A-29         3.4       EDMA3 Driver Initialization       2-A-71         3.5       API Flow Diagram       2-A-72         3.5.1       EDMA3 Driver Creation       2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.2     |        |                                         |     |

| 3.2.3       EDMA3_DRV_InitConfig.       2-A-18         3.2.4       EDMA3_DRV_MiscParam.       2-A-19         3.2.5       EDMA3_DRV_ChainOptions.       2-A-20         3.2.6       EDMA3_DRV_PaRAMRegs.       2-A-21         3.2.7       EDMA3_DRV_EvtQuePriority       2-A-23         3.3       API Specification       2-A-25         3.3.1       Creation       2-A-27         3.3.2       Configuration       2-A-29         3.4       Termination       2-A-68         2.4       EDMA3 Driver Initialization       2-A-71         3.5       API Flow Diagram       2-A-72         3.5.1       EDMA3 Driver Creation       2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |        |                                         |     |

| 3.2.4       EDMA3_DRV_MiscParam.       2-A-19         3.2.5       EDMA3_DRV_ChainOptions.       2-A-20         3.2.6       EDMA3_DRV_PaRAMRegs.       2-A-21         3.2.7       EDMA3_DRV_EvtQuePriority       2-A-23         3.3       API Specification       2-A-25         3.3.1       Creation       2-A-25         3.3.2       Configuration       2-A-27         3.3.3       Control       2-A-29         3.4       Termination       2-A-68         3.4       EDMA3 Driver Initialization       2-A-71         3.5       API Flow Diagram       2-A-72         3.5.1       EDMA3 Driver Creation       2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |        | •                                       |     |

| 3.2.5 EDMA3_DRV_ChainOptions2-A-203.2.6 EDMA3_DRV_PaRAMRegs2-A-213.2.7 EDMA3_DRV_EvtQuePriority2-A-233.3 API Specification2-A-243.3.1 Creation2-A-253.3.2 Configuration2-A-273.3.3 Control2-A-293.4 Termination2-A-682.42.53.5API Flow Diagram3.5API Flow Diagram3.52-A-723.5.1 EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |        |                                         |     |

| 3.2.6EDMA3_DRV_PaRAMRegs.2-A-213.2.7EDMA3_DRV_EvtQuePriority2-A-233.3API Specification2-A-243.1Creation2-A-253.2Configuration2-A-273.3Control2-A-293.4Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |        |                                         |     |

| 3.2.7 EDMA3_DRV_EvtQuePriority       2-A-23         3.3       API Specification       2-A-24         3.3.1 Creation       2-A-25         3.3.2 Configuration       2-A-27         3.3.3 Control       2-A-29         3.3.4 Termination       2-A-68         3.5       EDMA3 Driver Initialization       2-A-71         3.5       API Flow Diagram       2-A-72         3.5.1 EDMA3 Driver Creation       2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |        |                                         |     |

| 3.3       API Specification       2-A-24         3.3.1       Creation       2-A-25         3.3.2       Configuration       2-A-27         3.3.3       Control       2-A-29         3.3.4       Termination       2-A-68         3.4       EDMA3 Driver Initialization       2-A-71         3.5       API Flow Diagram       2-A-72         3.5.1       EDMA3 Driver Creation       2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |        |                                         |     |

| 3.3.1       Creation       2-A-25         3.3.2       Configuration       2-A-27         3.3.3       Control       2-A-29         3.3.4       Termination       2-A-68         3.4       EDMA3 Driver Initialization       2-A-71         3.5       API Flow Diagram       2-A-72         3.5.1       EDMA3 Driver Creation       2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3 3     |        |                                         |     |

| 3.3.2       Configuration       2-A-27         3.3.3       Control       2-A-29         3.3.4       Termination       2-A-68         3.4       EDMA3 Driver Initialization       2-A-71         3.5       API Flow Diagram       2-A-72         3.5.1       EDMA3 Driver Creation       2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.5     |        |                                         |     |

| 3.3.3 Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |        |                                         |     |

| 3.3.4 Termination2-A-683.4EDMA3 Driver Initialization2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |        |                                         |     |

| 3.4EDMA3 Driver Initialization2-A-713.5API Flow Diagram2-A-723.5.1EDMA3 Driver Creation2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |        |                                         |     |

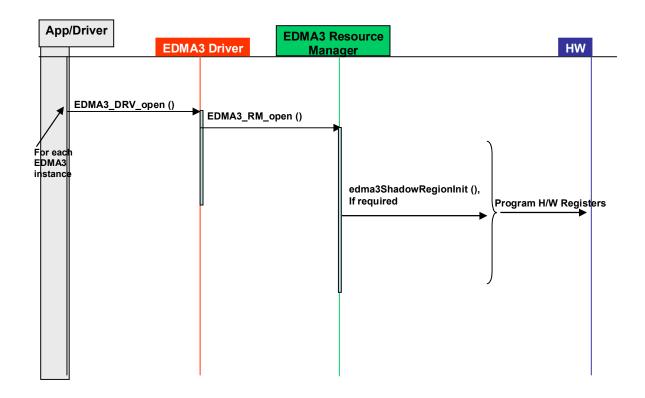

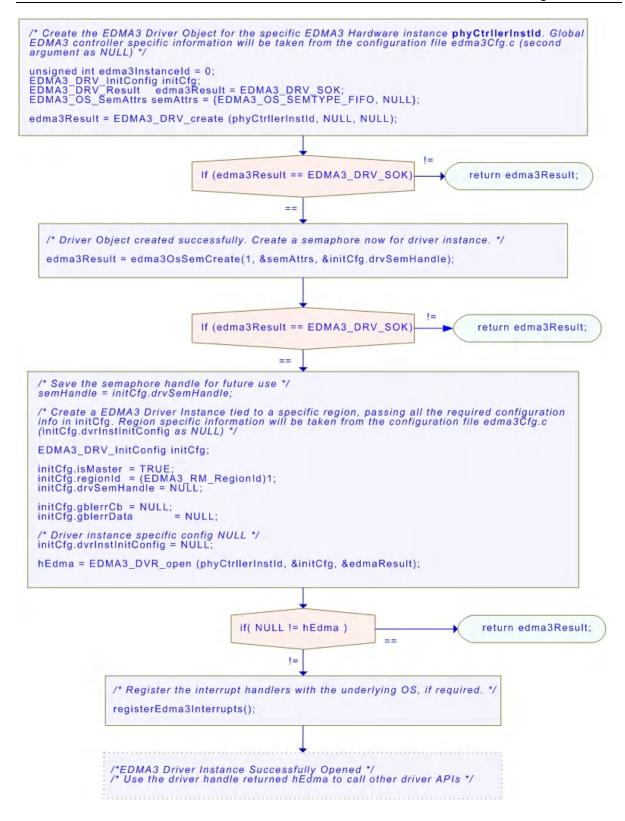

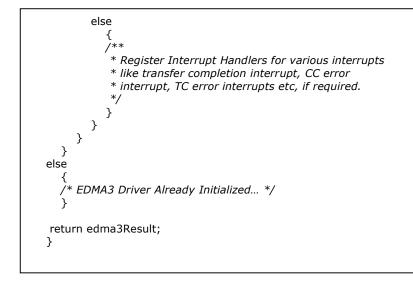

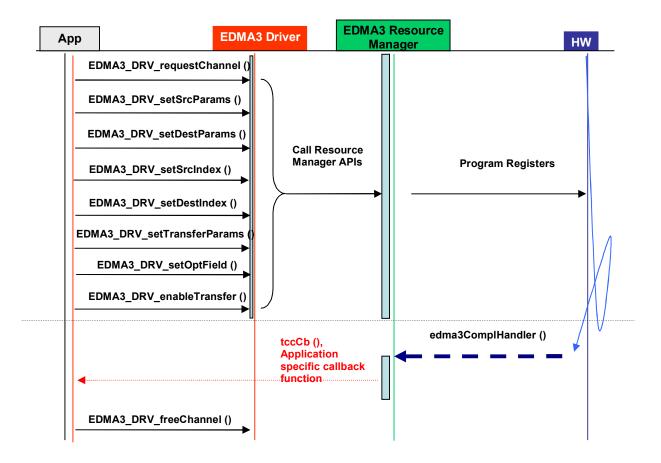

| 3.5         API Flow Diagram         2-A-72           3.5.1         EDMA3 Driver Creation         2-A-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.4     |        |                                         |     |

| 3.5.1 EDMA3 Driver Creation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |        |                                         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |        |                                         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |        |                                         |     |

| 3.5.3 EDI | 1A3 Request Channel (DMA / QDMA Channel)                                                                    | 2-A-74                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 3.5.4 EDN | 1A3 Request Channel (LINK Channel)                                                                          | 2-A-75                                                              |

| 3.5.5 EDN | 1A3 Close                                                                                                   | 2-A-76                                                              |

| 3.5.6 EDN | 1A3 Delete                                                                                                  | 2-A-77                                                              |

| API U     | Jsage Example                                                                                               | 2-A-78                                                              |

| Driver Po | orting                                                                                                      | 3-A-84                                                              |

| Gett      | ing Started                                                                                                 | 3-A-85                                                              |

| Step      | -by-Step procedure for porting                                                                              | 3-A-87                                                              |

| 3.8.1 edn | na3_ <platform_name>_cfg.c:</platform_name>                                                                 | 3-A-87                                                              |

| 3.8.2 edn | na3_rm_bios_ <platform_name>_lib.pjt</platform_name>                                                        | 3-A-88                                                              |

| 3.8.3 OS- | dependent (sample) Implementation                                                                           | 3-A-89                                                              |