# C2000<sup>™</sup> Multicore Development User Guide v1.0

Copyright © 2020, Texas Instruments Incorporated

Online HTML version available here

# CONTENTS

| 1 | Introduction                                                                                                                                                                                                                                                                                                                | 2                                          |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 2 | Memory blocks available                                                                                                                                                                                                                                                                                                     | 3                                          |

| 3 | Ownership assignment of shared resources3.1LSxRAM3.2GSx RAM3.3Peripherals3.4GPIOs                                                                                                                                                                                                                                           | <b>5</b><br>5<br>6<br>7                    |

| 4 | Communication between CPU1, CPU2 and CM cores4.1Message RAMs4.2IPC Flags and Command registers4.3Trigger an interrupt (with no data) from one core to another4.4Send a command from one core to another with interrupt4.5Sending a large amount of data from one core to another4.6Synchronize 2 cores4.7IPC Message queues | 8<br>8<br>10<br>11<br>12<br>12<br>13<br>13 |

| 5 | Communication between C28x and CLA                                                                                                                                                                                                                                                                                          | 14                                         |

| 6 | Debugging multiple cores6.1Loading program in multiple cores6.2Loading program in CLA6.3Exercise 1 - Multi-core Debug Example6.4Viewing Memories/Registers/Expressions6.5Exercise 1 - Multi-core Debug Example (continued)                                                                                                  | <b>15</b><br>15<br>16<br>17<br>19<br>19    |

| 7 | Examples from C2000ware7.1Exercise 2 - IPC example7.2Exercise 3 - IPC example with message queues7.3Exercise 4 - CLA example7.4Exercise 5 - Dual core GPIO example7.5Exercise 6 - CM example with shared peripheral                                                                                                         | <b>21</b><br>23<br>24<br>26<br>26          |

| 8 | Frequently Asked Questions                                                                                                                                                                                                                                                                                                  | 28                                         |

| 9 | IMPORTANT NOTICE AND DISCLAIMER                                                                                                                                                                                                                                                                                             | 30                                         |

This guide describes various cores available in C2000<sup>TM</sup> devices and how other resources such as peripherals, memories, GPIOs are shared among these. It also talks about how to communicate and share data among different cores. This guide is written for F2838x family of devices, but this can also apply for other devices with some exceptions.

# INTRODUCTION

Note: The online HTML version of this guide is available at

https://software-dl.ti.com/C2000/docs/C2000\_Multicore\_Development\_User\_Guide/index.html.

The F2838x family of devices contain 2 C28x CPU subsystems and one CM (Connectivity Manager) subsystem. The C28x CPU subsystem includes a C28x core, a CLA, and a DMA. The CM subsystem has an ARM Cortex M4 core and a uDMA.

Cores available in F2838x device:

- C28x1

- CPU1.CLA

- C28x2

- CPU2.CLA

- CM

Note that C28x1 and C28x2 cores are also referred as CPU1 and CPU2 respectively.

An important aspect in a multi-core application development is to split the resources across different cores. The F2838x device includes multiple memory blocks, peripherals and GPIOs, some of which are dedicated to certain cores, and some are shared across multiple cores. All the shared resources has to be assigned to an owner core before accessing the same. The ownership needs to be assigned by CPU1, which is the master core. Chapter *Ownership assignment of shared resources* provides details about the how to configure and assign ownership of various resources in the device.

Another important aspect is to enable effective communication and data sharing among various cores. The device has dedicated message RAMs which can be used for sharing data. It also includes an InterProcessor Communication (IPC) module which is used to communicate between C28x1, C28x2 and CM cores. This is further explained in chapters *Communication between CPU1, CPU2 and CM cores* and *Communication between C28x and CLA*.

The chapter *Debugging multiple cores* describes in detail how to load binaries in various cores and debug them. The chapter *Examples from C2000ware* demonstrates various examples available in C2000ware.

In the F2838x device, C28x1 core acts as the master core. The basic initialization of the device including the clocking and GPIO settings should be done by the CPU1 application. CPU1 can be booted in different modes based on the boot pin configuration. The CPU2 and the CM cores must be booted by the CPU1 application using the IPC module. Refer to the TRM chapter *ROM Code and Peripheral Booting* for more details on boot modes and boot pins. Some of these aspects are covered as part of example available in chapter *Examples from C2000ware*

For more details on CLA software development, please refer to to the C2000<sup>TM</sup> CLA Software Development Guide and the appnote Software Examples to Showcase Unique Capabilities of TI's C2000<sup>TM</sup> CLA

### TWO

# MEMORY BLOCKS AVAILABLE

The following table lists the memories available in the device and their accessibility across cores. Please check the device datasheet for the actual size of the memories.

| Memory            | C28x | CLA | СМ | Notes                                                                                                               |

|-------------------|------|-----|----|---------------------------------------------------------------------------------------------------------------------|

| Mx/Dx RAM         | Y    | N   | N  | Each CPU subsystem has dedicated RAM blocks.                                                                        |

| LSx RAM           | Y    | Y   | N  | Each CPU subsystem has dedicated RAM blocks.<br>Can be used as CLA data/program memory.                             |

| GSx RAM           | Y    | N   | N  | Shared between C28x1 and C28x2.<br>Shared with DMA on each of the CPU subsystem.                                    |

| Cx RAM            | N    | N   | Y  |                                                                                                                     |

| Sx/Ex RAM         | N    | N   | Y  | Shared with UDMA on CM subsystem.                                                                                   |

| CPUx-CPUx MSG RAM | Y    | N   | N  | Separate RAM blocks for CPU1 to CPU2 and CPU2 to CPU1 communication.                                                |

| CPUx-CM MSG RAM   | Y    | N   | Y  | Separate RAM blocks for CPUx to CM and CM to CPUx communication.                                                    |

| CLA Message RAM   | Y    | Y   | N  | Each CPU subsystem has dedicated RAM blocks.<br>Separate RAM blocks for CPU to CLA and CLA to<br>CPU communication. |

Table 2.1: Memory blocks available on F2838x

continues on next page

| Memory                 | C28x | CLA | СМ | Notes                                                                                                               |

|------------------------|------|-----|----|---------------------------------------------------------------------------------------------------------------------|

| CLA-DMA Message<br>RAM | Ν    | Y   | Ν  | Each CPU subsystem has dedicated RAM blocks.<br>Separate RAM blocks for CLA to DMA and DMA to<br>CLA communication. |

| Flash                  | Y    | N   | Y  | CPU1, CPU2 and CM has dedicated flash memory blocks.                                                                |

Table 2.1 – continued from previous page

THREE

# **OWNERSHIP ASSIGNMENT OF SHARED RESOURCES**

### 3.1 LSxRAM

The dual-core C2000 device includes dedicated LS RAMs for CPU1 and CPU2 subsystems. LSxRAM can be owned by the C28x core or by the CLA core. The ownership of LS RAM should be assigned by the C28x core in the respective subsystem.

By default, all the LS RAMs are configured as C28x only memory.

| Configuration                                 | Register to be set                               | Driverlib function                                                                                                                                    |

|-----------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| C28x only<br>memory                           | LSxMSEL.MSEL_LSx = 0                             | MemCfg_setLSRAMMasterSel<br>(MEMCFG_SECT_LSx,<br>MEMCFG_LSRAMMASTER_CPU_ONLY)                                                                         |

| CLA program<br>memory                         | LSxMSEL.MSEL_LSx = 1<br>LSxCLAPGM.CLAPGM_LSx = 1 | MemCfg_setLSRAMMasterSel<br>(MEMCFG_SECT_LSx,<br>MEMCFG_LSRAMMASTER_CPU_CLA1)<br>MemCfg_setCLAMemType<br>(MEMCFG_SECT_LSx,<br>MEMCFG_CLA_MEM_PROGRAM) |

| Data memory<br>shared between<br>C28x and CLA | LSxMSEL.MSEL_LSx = 1<br>LSxCLAPGM.CLAPGM_LSx = 0 | MemCfg_setLSRAMMasterSel<br>(MEMCFG_SECT_LSx,<br>MEMCFG_LSRAMMASTER_CPU_CLA1)<br>MemCfg_setCLAMemType<br>(MEMCFG_SECT_LSx,<br>MEMCFG_CLA_MEM_DATA)    |

Table 3.1: LSxRAM ownership assignment

# 3.2 GSx RAM

GS RAMs are shared between CPU1 and CPU2 subsystems. The ownership of GS RAM should be assigned by CPU1. By default, all the GS RAMs are owned by CPU1 subsystem.

| Configuration              | Register to be set   | Driverlib function                                                        |

|----------------------------|----------------------|---------------------------------------------------------------------------|

| Owned by CPU1<br>subsystem | GSxMSEL.MSEL_GSx = 0 | MemCfg_setGSRAMMasterSel<br>(MEMCFG_SECT_GSx,<br>MEMCFG_GSRAMMASTER_CPU1) |

| Owned by CPU2<br>subsystem | GSxMSEL.MSEL_GSx = 1 | MemCfg_setGSRAMMasterSel<br>(MEMCFG_SECT_GSx,<br>MEMCFG_GSRAMMASTER_CPU2) |

| Table 3.2: | GSxRAM | ownership | assignment |

|------------|--------|-----------|------------|

|            |        |           |            |

# 3.3 Peripherals

Most of the C28x peripherals are shared between CPU1 and CPU2. Please refer to the device datasheet for available peripherals. The ownership of the peripherals should be assigned by CPU1.

By default, all the peripherals are owned by CPU1.

| Configuration                        | Register to be set | Driverlib function                                                       |

|--------------------------------------|--------------------|--------------------------------------------------------------------------|

| Owned by CPU1 CPUSELx.module = 0     |                    | SysCtl_selectCPUForPeripheral (peripheral, instance, SYSCTL_CPUSEL_CPU1) |

| Owned by CPU2     CPUSELx.module = 1 |                    | SysCtl_selectCPUForPeripheral (peripheral, instance, SYSCTL_CPUSEL_CPU2) |

Table 3.3: C28x Peripheral ownership assignment

There are few peripherals such as CAN, MCAN, Ethernet and USB which are shared across CPU1, CPU2 and CM cores. The ownership of shared peripheral should be assigned by CPU1.

| Configuration | Register to be set                                  | Driverlib function                                                                                                             |

|---------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Owned by CPU1 | CPUSELx.bit.module = 0<br>PALLOCATE0.bit.module = 0 | SysCtl_selectCPUForPeripheral (peripheral, instance,<br>SYSCTL_CPUSEL_CPU1)<br>SysCtl_allocateSharedPeripheral (peripheral, 0) |

Table 3.4: Shared Peripheral ownership assignment

continues on next page

| Configuration | Register to be set                                  | Driverlib function                                                                                                             |

|---------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Owned by CPU2 | CPUSELx.bit.module = 1<br>PALLOCATE0.bit.module = 0 | SysCtl_selectCPUForPeripheral (peripheral, instance,<br>SYSCTL_CPUSEL_CPU2)<br>SysCtl_allocateSharedPeripheral (peripheral, 0) |

| Owned by CM   | PALLOCATE0.bit.module = 1                           | SysCtl_allocateSharedPeripheral (peripheral, 1)                                                                                |

Table 3.4 – continued from previous page

Note: The peripheral clock must be enabled by the owner core.

# 3.4 GPIOs

The GPIOs on the devices are shared across all the cores and the ownership should be assigned by the CPU1 core before using them.

By default, all the GPIOs are owned by CPU1.

| Configuration                            | Register to be set     | Driverlib function                            |

|------------------------------------------|------------------------|-----------------------------------------------|

| Owned by CPU1 GPxCSELy.bit.GPIOz =       |                        | GPIO_setMasterCore (pin, GPIO_CORE_CPU1)      |

| Owned by CPU1.CLA                        | GPxCSELy.bit.GPIOz = 1 | GPIO_setMasterCore (pin, GPIO_CORE_CPU1_CLA1) |

| Owned by CPU2GPxCSELy.bit.GPIOz = 2      |                        | GPIO_setMasterCore (pin, GPIO_CORE_CPU2)      |

| Owned by CPU2.CLA GPxCSELy.bit.GPIOz = 3 |                        | GPIO_setMasterCore (pin, GPIO_CORE_CPU2_CLA1) |

| Owned by CMGPxCSELy.bit.GPIOz = 4        |                        | GPIO_setMasterCore (pin, GPIO_CORE_CM)        |

Table 3.5: GPIO ownership assignment

FOUR

# COMMUNICATION BETWEEN CPU1, CPU2 AND CM CORES

### 4.1 Message RAMs

The device includes dedicated MSG RAMs for each combination of cores. For example, for sharing data from CPU1 to CPU2, CPU1 needs to write data to CPU1 TO CPU2 MSGRAM and CPU2 can read from this location. All the MSG RAMs are accessible to DMA (on C28x side) and to uDMA (on the CM side).

The following table lists out various Message RAMs available in the device and its accessibility across different cores. This also includes the name of the driverlib macro which holds the base address of the Message RAM.

- RW : Read and Write access

- R : Read access

- X : No access

| Memory              | CPU1 | CPU2 | СМ | Driverlib macro                                                        |

|---------------------|------|------|----|------------------------------------------------------------------------|

| CPU1_TO_CPU2 MSGRAM | RW   | R    | X  | C28x:<br>CPU1TOCPU2MSGRAM0_BASE<br>CPU1TOCPU2MSGRAM1_BASE<br>CM:<br>NA |

| CPU2_TO_CPU1 MSGRAM | R    | RW   | X  | C28x:<br>CPU2TOCPU1MSGRAM0_BASE<br>CPU2TOCPU1MSGRAM1_BASE<br>CM:<br>NA |

#### Table 4.1: IPC Message RAMs

continues on next page

| Memory            | CPU1 | CPU2 | CM | Page Driverlib macro                                                                                         |

|-------------------|------|------|----|--------------------------------------------------------------------------------------------------------------|

| CPU1_TO_CM MSGRAM | RW   | x    | R  | C28x:<br>CPUXTOCMMSGRAM0_BASE<br>CPUXTOCMMSGRAM1_BASE<br>CM:<br>CPU1TOCMMSGRAM0_BASE<br>CPU1TOCMMSGRAM1_BASE |

| CM_TO_CPU1 MSGRAM | R    | X    | RW | C28x:<br>CMTOCPUXMSGRAM0_BASE<br>CMTOCPUXMSGRAM1_BASE<br>CM:<br>CMTOCPU1MSGRAM0_BASE<br>CMTOCPU1MSGRAM1_BASE |

| CPU2_TO_CM MSGRAM | X    | RW   | R  | C28x:<br>CPUXTOCMMSGRAM0_BASE<br>CPUXTOCMMSGRAM1_BASE<br>CM:<br>CPU2TOCMMSGRAM0_BASE<br>CPU2TOCMMSGRAM1_BASE |

| CM_TO_CPU2 MSGRAM | X    | R    | RW | C28x:<br>CMTOCPUXMSGRAM0_BASE<br>CMTOCPUXMSGRAM1_BASE<br>CM:<br>CMTOCPU2MSGRAM0_BASE<br>CMTOCPU2MSGRAM1_BASE |

Table 4.1 – continued from previous page

Not that the addresses of the CPUx-CM MSG RAM on the C28x side and CM side are different. Also, on the C28x side, the addresses of CPU1\_TO\_CM and CPU2\_O\_CM MSG RAMs are the same. Depending on the core which is doing the write access (CPU1 or CPU2), the corresponding RAM block is updated. Similarly, same addresses are used for CM\_TO\_CPU1 and CM\_TO\_CPU2 MSG RAMs, depending on the core which is doing the read access (CPU1 or CPU2), the corresponding RAM block is updated. Similarly, same addresses are used for CM\_TO\_CPU1 and CM\_TO\_CPU2 MSG RAMs, depending on the core which is doing the read access (CPU1 or CPU2), the corresponding RAM block is read.

# 4.2 IPC Flags and Command registers

The device also includes Inter processor Communication (IPC) module for communication between cores. The F2838x device has 3 instances of IPC for the following communications:

- CPU1-CPU2

- CPU1-CM

- CPU2-CM

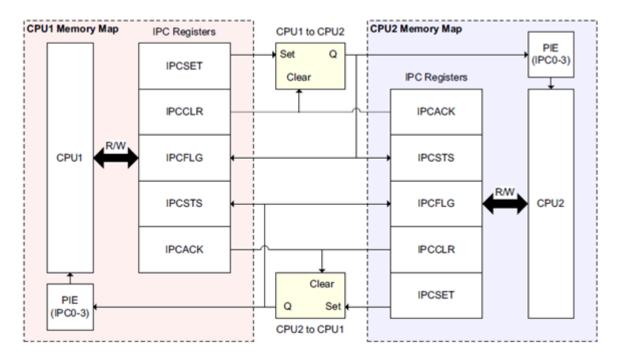

IPC includes registers for sending up to 32 flags from one core to another. For CPU1-CPU2 IPC instance, 4 of these flags have interrupt capability; which means, both C28x1 and C28x2 has 4 dedicated interrupt channels which can be triggered by the other C28x core. For CPUx-CM IPC instances, 8 out of the 32 flags have interrupt capability; which means, C28x1, C28x2 and CM has 8 dedicated interrupt channels which can be triggered by the other core.

Fig. 4.1: IPC flags

Apart from the flags registers, the IPC module includes dedicated command registers. This include 4 registers for sending and 4 registers for receiving commands.

| Local Register Name | Local CPU | Remote CPU | Remote Register Name |

|---------------------|-----------|------------|----------------------|

| IPCSENDCOM          | R/W       | R          | IPCRECVCOM           |

| IPCSENDADDR         | R/W       | R          | IPCRECVADDR          |

| IPCSENDDATA         | R/W       | R          | IPCRECVDATA          |

| IPCREMOTEREPLY      | R         | R/W        | IPCLOCALREPLY        |

Fig. 4.2: IPC command registers

For more details on the IPC flags and command registers, please refer to the TRM chapter *Interprocessor Communication (IPC)*.

Since the address spaces of CM and C28x are different, the driverlib functions used for sending and receiving messages includes a parameter *addrCorrEnable* which will correct the address while sending a command from CPUx to CM or vice versa. For more details, please refer to the driverlib API guide.

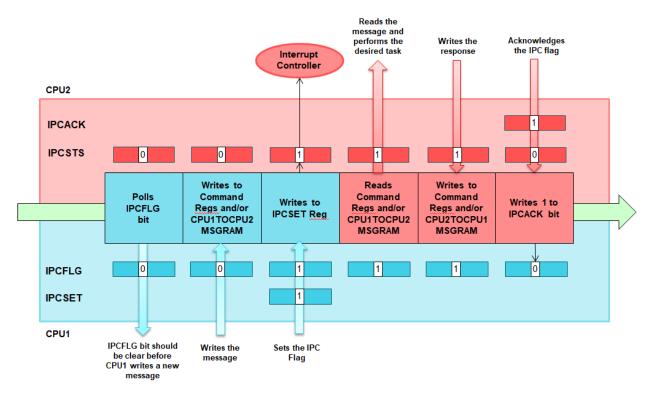

For sending data or commands from one core to the another, application can use the IPC flags, command registers and the message RAM as per the need. The image below shows a basic flow of how these can be used. The upcoming sections provide more details on how these are used for different usecases.

Fig. 4.3: IPC flow diagram

**Note:** The letters *L* and *R* used in IPC driverlib APIs denotes *Local* and *Remote* cores. For CPU1 to CPU2 communication, the enum *CPU1\_L\_CPU2\_R* shall be used as the parameter *ipcType* in the driverlib functions.

### 4.3 Trigger an interrupt (with no data) from one core to another

- Select a flag from the available IPC flags with interrupt capability. For CPU1-CPU2 IPC instance, IPC\_FLAG0-3 has interrupt capability and for CPU1-CM and CPU2-CM IPC instances IPC\_FLAG0-7 has interrupt capability.

- 2. Core2 : Enable interrupt corresponding the selected flag. Driverlib function: *IPC\_registerInterrupt*.

- 3. **Core1**: Make sure the corresponding bit in IPCFLG register is not already set. Driverlib function : *IPC\_isFlagBusyLtoR*.

- 4. **Core1**: Set the corresponding bit in IPCSET register. The bit in IPCFLG register will be set automatically. Driverlib function : *IPC\_setFlagLtoR*.

- 5. Core2: The corresponding bit in IPCSTS will be set and the interrupt is triggered.

- 6. **Core2**: IPC ISR is invoked. Service the interrupt and acknowledge the flag by setting the IPCACK register. Driverlib function : *IPC\_ackFlagRtoL*.

- 7. Setting the IPCACK register will clear the corresponding bit in IPCSTS register in Core2 and the IPCFLG register in Core1.

Core 1 can optionally wait for Ack from Core2 using the function *IPC\_waitForAck*. If interrupt is not enabled on Core2, the IPC flag can be polled using the function *IPC\_waitForFlag*.

#### 4.4 Send a command from one core to another with interrupt

An IPC Command includes a 32 bit command, 32 bit address and a 32 bit data registers. Though the name suggests command, address and data, you can send any 3 32-bit data using the command registers.

- 1. Select a flag from the available IPC flags.

- 2. Core2 : Enable interrupt corresponding the selected flag. Driverlib function: *IPC\_registerInterrupt*.

- 3. **Core1 :** Call the driverlib function *IPC\_sendCommand*. The function checks if corresponding bit in IPCFLG register is not already set and sets the command, address and data registers to send to the the other core. And finally it sets the selected IPC flag.

- 4. Core2: The corresponding bit in IPCSTS will be set and the interrupt is triggered.

- 5. Core2 : IPC ISR is invoked. Read the command registers and service the interrupt. Driverlib function : *IPC\_readCommand*.

- 6. Core2 : Send response back to Core1 and acknowledge the flag by setting the IPCACK register. Driverlib functions : *IPC\_sendResponse*, *IPC\_ackFlagRtoL*.

- 7. Setting the IPCACK register will clear the corresponding bit in IPCSTS register in Core2 and the IPCFLG register in Core1.

Core 1 can optionally wait for Ack from Core2 using the function *IPC\_waitForAck*. If interrupt is not enabled on Core2, the IPC flag can be polled using the function *IPC\_waitForFlag*.

#### 4.5 Sending a large amount of data from one core to another

- 1. **Core1**: Write the data to the corresponding MSG RAM.

- 2. Core1 : Follow the steps mentioned above to send the command. The address parameter in the command can be set to address of the data in MSG RAM and data parameter can be set to the length of the data. addrCorrEnable should be set so that the function IPC\_sendCommand corrects the address of the MSGRAM. This is important while sharing data between C28x and CM cores since the addresses of the MSG RAM is different in these cores.

- 3. **Core2**: Follow the steps mentioned above to receive the command. The address and length of the data will be available in the received command.

### 4.6 Synchronize 2 cores

The IPC driverlib provides a function *IPC\_sync* for synchronizing two cores. The function is expected to be called from both the cores using the same flag. It does the following in order:

- Sets the Flag from the Local core to Remote core

- Sets the IPCSET register

- This sets the IPSTS register in remote core

- Waits for the flag from Remote core to Local core

- Waits for IPCSTS register

- This is set when remote core sets the IPCSET register

- · Acknowledges the flag from Remote core

- Sets the IPC\_ACK register

- This clears the IPCFLG register in the remote core

- Waits for Acknowledge from the Remote core

- Waits for IPC\_FLG to be cleared

- This is cleared when remote core writes to IPCACK register

This flow makes sure that neither core will return from this function before the other core enters it. That means, if Core1 reaches the sync function, it will wait until Core2 reaches the function and vice versa.

To use the IPC\_sync function:

- 1. Select a flag from the available IPC flags. Preferably one without interrupt capability since we will be using polling method for synchronizing cores.

- 2. Core1 : Call *IPC\_sync* function with the selected flag as parameter

- 3. Core2 : Call IPC\_sync function with the selected flag as parameter

### 4.7 IPC Message queues

If you are using IPC command registers, queuing of commands is not possible, That means, core 1 can send a command only after the previous command is acknowledged. To overcome this, the IPC driver has implemented message queuing mechanism using software. It uses the MSG RAM to store and send the commands. The driverlib functions *IPC\_initMessageQueue*, *IPC\_sendMessageToQueue* and *IPC\_readMessageFromQueue* can be used for this.

Please refer to the C2000ware driverlib example which showcases how to use the MSG RAMs, send IPC commands and trigger interrupt on the other core. It provides examples with and without using message queues. These examples are covered in *Examples from C2000ware* section.

# **COMMUNICATION BETWEEN C28X AND CLA**

Each CPU subsystem contains a C28x core and a CLA core. C28x core can only communicate to the CLA core in its own subsystem. The IPC module is not available to CPU-CLA communication

For sharing data between C28x and CLA, CPU-CLA MSG RAMs can be used. The device includes dedicated MSG RAMs for CPU to CLA and CLA to CPU communication.

The following table lists out various CPU-CLA Message RAMs available in the device and its accessibility across different cores. This also includes the name of the driverlib macro which holds the base address of the Message RAM.

- RW : Read and Write access

- R : Read access

| Memory             | C28x               | CLA | Driverlib macro   |

|--------------------|--------------------|-----|-------------------|

| CPU_TO_CLA MSG RAM | RW                 | R   | CPUTOCLA_RAM_BASE |

| CLA_TO_CPU MSG RAM | R RW CLATOCPU_RAM_ |     | CLATOCPU_RAM_BASE |

Table 5.1: CLA Message RAMs

To send data from CPU to CLA, CPU needs to write the data in the CPUTOCLA\_RAM which can be read by CLA and vice versa.

CLA tasks can be triggered by either C28x software or by peripheral events. C28x software can trigger CLA tasks by setting the corresponding bit in the MIFRC register. The driverlib function *CLA\_forceTasks* does the same.

Note that the global variables defined in the .cla file are global to the cla source file, which means they are shared across CLA tasks, but not with the C28x core. All of the data shared between C28x and CLA must be defined in .c or .cpp file, and not in the .cla file.

Please refer to the c2000ware driverlib example which showcases how CPU triggers CLA tasks with CPU sending a data to CLA and CLA sending back the processed data. These examples are covered in *Examples from C2000ware* section.

SIX

# **DEBUGGING MULTIPLE CORES**

# 6.1 Loading program in multiple cores

This section is applicable for CPU1, CPU2 and CM.

There are different ways to launch a debug session and load programs to various cores.

**Project Debug** : Once the CCS project is built, load the .out by selecting Run $\rightarrow$ Debug. CCS will identify compatible cores and prompt the user to select the required core(s). CCS will automatically connect to the selected cores and load the .out.

| 🔀 Launching Debug Session                                                                                       |                        |               | $\times$ |

|-----------------------------------------------------------------------------------------------------------------|------------------------|---------------|----------|

| The project cla_ex1_asin is compatible with multiple CPUs in the target co                                      | nfiguration.           |               |          |

| Please select the CPUs to load the program on. This selection will be asso                                      | ciated with the active | target config | uration. |

| Texas Instruments XDS100v2 USB Debug Probe_0/C28xx_CPU1 Texas Instruments XDS100v2 USB Debug Probe_0/C28xx_CPU2 |                        |               |          |

|                                                                                                                 | Select All             | Deselect      | All      |

| Create a debug group for selected cores<br>Make the group synchronous                                           |                        |               |          |

| ?                                                                                                               | ОК                     | Cance         | 1        |

**Project-less Debug Session** : Under Target Configurations, right click on the required target configuration file and select 'Launch selected configuration'. Connect the required targets and load the .out by selecting Run->Load.

####

- \* Texas Instruments XDS100v2 USB Debug Probe\_0/CPU1\_CLA1 (Disconnected : Unknown)

- \* Texas Instruments XDS100v2 USB Debug Probe\_0/C28xx\_CPU2 (Disconnected : Unknown)

- \* Texas Instruments XDS100v2 USB Debug Probe\_0/CPU2\_CLA1 (Disconnected : Unknown)

- \* Texas Instruments XDS100v2 USB Debug Probe\_0/Cortex\_M4\_0 (Disconnected : Unknown)

**Note:** The C28x1 is the master core in this device and must be connected and loaded prior to the other cores. The clocks and other basic system initialization must be done by the CPU1 application. For example, if you want to run a CM example, CPU1 should be loaded with a basic application that does the system initialization.

For more details on Multi-Core Debug in CCS : https://processors.wiki.ti.com/index.php/Multi-Core\_Debug\_with\_CCS

# 6.2 Loading program in CLA

The CLA program is usually embedded in the corresponding C28x program itself and is loaded as part of loading the C28x core. Once the .out is loaded to C28x core, connect to the CLA core and execute 'Load symbols'. This option adds the symbols available in the .out for debugging purposes instead of loading the actual .out in the core.

| 🏶 Debug 🛙  |                                                                                    | ₽ 🐐 | 8 <sup>–</sup> E |

|------------|------------------------------------------------------------------------------------|-----|------------------|

| ✓ ♥ F2838x | ControlCard.ccxml [Code Composer Studio - Device Debugging]                        |     |                  |

| 👻 🧬 Texa   | s Instruments XDS100v2 USB Debug Probe_0/C28xx_CPU1 (Suspended - SW Breakpoint)    |     |                  |

| ≡n         | nain() at cla_ex1_asin.c:245 0x00A6CF                                              |     |                  |

| ى ≡        | args_main() at args_main.c:131 0x00A76F                                            |     |                  |

| ≡_0        | c_int00() at boot28.asm:264 0x00A53B (_c_int00 does not contain frame information) |     |                  |

| 🔎 Texa     | s Instruments XDS100v2 USB Debug Probe_0/CPU1_CLA1 (Disconnected : Unknown)        |     |                  |

| ×® Texa    | s Instruments XDS100v2 USB Debug Probe_0/C28xx_CPU2 (Disconnected : Unknown)       |     |                  |

| ×® Texa    | s Instruments XDS100v2 USB Debug Probe_0/CPU2_CLA1 (Disconnected : Unknown)        |     |                  |

| ×® Texa    | s Instruments XDS100v2 USB Debug Probe_0/Cortex_M4_0 (Disconnected : Unknown)      |     |                  |

|            |                                                                                    |     |                  |

|            | 🔂 Load Symbols 🛛 🕹                                                                 |     |                  |

|            |                                                                                    |     |                  |

|            | Program file ex1_asin\CPU1_RAM\cla_ex1_asin.out ~ Browse Browse project            |     |                  |

|            |                                                                                    |     |                  |

|            | Code offset                                                                        |     |                  |

|            | Data offset                                                                        |     |                  |

|            |                                                                                    |     |                  |

|            |                                                                                    |     |                  |

|            | OK Cancel                                                                          |     |                  |

| L          |                                                                                    |     |                  |

|            |                                                                                    |     |                  |

The CLA program must be loaded in the LSxRAM. Note that the LSRAM must be configured as CLA program memory. In case of Flash configuration, the CLA program can be loaded in Flash, but must be copied to the LSxRAM. The linker command file should be updated to have this section load to Flash and run from LSxRAM. All the CLA data sections must be loaded into LSxRAM and RAM blocks must be configured as CLA Data RAM.

Please refer to the CLA example in C2000ware on memory configurations and linker command file updates needed.

# 6.3 Exercise 1 - Multi-core Debug Example

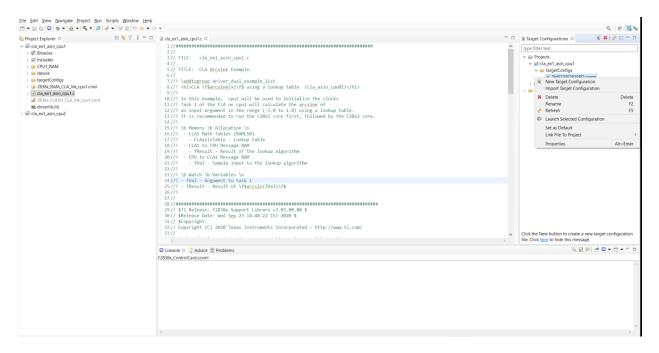

Loading program in CPU1, CPU2, CPU2.CLA using the C2000ware example. The example is available in <C2000Ware>\driverlib\f2838x\examples\c28x\_dual\cla\cla\_ex1\_asin.

This is a dual core example in which CPU1 application initializes the system clock and the CPU2 application triggers CLA tasks and shares some data to and fro. CPU2 application includes the CLA core code as well. In this exercise, we shall load both the applications in CPU1 and CPU2 cores respectively and Load symbols of CPU2 application in CPU2's CLA core.

Step 1 : Launch the Target CCXML file.

Right click on the ccxml file in Target Configurations view -> Launch selected configuration.

Step 2 : Connect to CPU1 and load the CPU1 application.

In the Debug view, right click on CPU1 core -> Connect Target.

| * Debug X       Calex1_asin_cpu1.c X         * TMS320F28388D.ccxml [Code Composer Studio - Device Debugging]       1//###################################                                                                                                                                                                                                                                                                                                                                                                             | <u>F</u> ile Edit <u>V</u> iew <u>P</u> roject <u>T</u> ools <u>R</u> un Scripts <u>W</u> indow <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                      | s <b>v</b>    | 3. o % + Ø 🗉 🛷 + 🖻                                                                                                                    |                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| CLA comparison       CLA comparison         SoC Analysis       ment in         Hide core(s)       nded to         Show all cores       nded to         Group core(s)       Allocation         Sync group core(s)       Tables         Ungroup core(s)       U Messe         Rename       - Resu         Remove All Terminated       1 Messe         Relaunch       Edit TMS320F28388D.ccxml       ariable         Edit TMS320F28388D.ccxml       ariable         Terminate and Remove       ariable         Terminate All       esult | <ul> <li>Debug II</li> <li>TMS320F28388D.ccxml [Code Composer Studio - Device Debugging]</li> <li>Texas Instruments XDS100v2 USB Debug Probe_0/C28xx_CPU1 (Disconnec<br/>Texas Instruments XDS100v2 USB Debug Probe_0/CPU1_CLA1 (Disconnec<br/>Texas Instruments XDS100v2 USB Debug Probe_0/CPU2_CLA1 (Disconnec<br/>Texas Instruments XDS100v2 USB Debug Probe_0/CPU2_CLA1 (Disconnec<br/>Texas Instruments XDS100v2 USB Debug Probe_0/Cortex_M4_0 (Disconnec<br/>Texas Instruments XDS100v2 USB Debug Probe_0/Cortex_M4_0 (Disconnec</li> </ul> | -             | Connect Target Ctrl+Alt+C<br>Disconnect Target Ctrl+Alt+D<br>Enable Global Breakpoints<br>Enable Halt On Reset<br>Enable OS Debugging | 1_asin_<br>csine E<br>river_d<br>csine(×                                                                           |

| Remove All Terminated       ample         Relaunch       Edit TMS320F28388D.ccxml       ariabl         Terminate and Remove       ment t         Terminate/Disconnect All       esult                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ×             | SoC Analysis<br>SoC Analysis<br>Hide core(s)<br>Show all cores<br>Group core(s)<br>Sync group core(s)<br>Ungroup core(s)              | <pre>&gt; le, c<br/>&gt; CLA oo<br/>ment i<br/>nded t<br/>Alloca<br/>Tables<br/>able -<br/>U Mess<br/>- Resu</pre> |

| Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>Q</b><br>© | Relaunch<br>Edit TMS320F28388D.ccxml<br>Terminate and Remove                                                                          | 1 Messa<br>ample i<br>ariable<br>ment to<br>esult o                                                                |

Run -> Load -> Load Program and select the cla\_ex1\_asin\_cpu1.out file.

Step 3 : Connect to CPU2 and load the CPU2 application.

In the Debug view, right click on CPU2 core -> Connect Target.

| <u>File Edit View Project Tools Run Scripts Window H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                        |                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 📬 🕶 🔤 🐚 💷 🕪 💷 🛋 🐟 🐟 📾 💷 🎭 🚳 🖛 🖄 🍏 🔷 🕶 🐇 🌴 🕶                                                                                                                                                                                                                                                                                                                                                                                                                      | 3. 0. <b>6 •</b> Ø C                                                                                                   | 1 🛷 🕶 📷                                                                                         |

| ‡r Debug ⊠                                                                                                                                                                                                                                                                                                                                                                                                                                                       | E 💥 🕴 🗖 🗖                                                                                                              | I cla_ex1_asin_cpu1.c ≅                                                                         |

| <ul> <li>TMS320F28388D.cccml [Code Composer Studio - Device Debugging]</li> <li>Person Texas Instruments XDS100v2 USB Debug Probe_0/C28xx_CPU1 (Suspended - Statistic)</li> <li>main() at cla_ex1_asin_cpu1.c:85 0x009289</li> <li>args_main() at args_main.c:133 0x0093E0</li> <li>_c_int00() at boot28.asm:264 0x00914D (_c_int00 does not contain frame in x<sup>®</sup> Texas Instruments XDS100v2 USB Debug Probe_0/CPU1_CLA1 (Disconnected : 1)</li> </ul> | formation)                                                                                                             | 74//<br>75 void initCpuXClal(void);<br>76<br>77 //<br>78 // Main<br>79 //<br>80 void main(void) |

| x <sup>®</sup> Texas Instruments XDS100v2 USB Debug Probe_0/C28xx_CPU2 (Disconnected<br>x <sup>®</sup> Texas Instruments XDS100v2 USB Debug Probe_0/CPU2_CLA1 (Disconnected<br>x <sup>®</sup> Texas Instruments XDS100v2 USB Debug Probe_0/Cortex_M4_0 (Disconnected                                                                                                                                                                                             | Connect Target<br>Disconnect Target<br>Enable Global Bre<br>Enable Halt On Re<br>Enable OS Debug<br>Open GEL Files Vie | Ctrl+Alt+C<br>Ctrl+Alt+D<br>evice<br>akpoints<br>eset Connect Target<br>ging                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Code Analysis<br>SoC Analysis                                                                                          | > (800)                                                                                         |

Run -> Load -> Load Program and select the cla\_ex1\_asin\_cpu2.out file.

Step 4 : Connect to CLA and load the CPU2 application symbols.

Since the CPU2 application is already loaded, we just need to Load the symbols of CPU2 application on the CLA core. In the Debug view, right click on CLA core -> Connect Target.

<u>File Edit View Project Tools Run Scripts Window Help</u>

| 🖆 🕶 🐘 📴 🕪 🗉 🔳 3. (5 . k) 🏛 🖳 % 🚇 🕶 🖄 🖄 👻 🗳 🖝 🔅                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - 3                    |                                                                                                                        | - 🔗 🗸                                                              |                                      |                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------|-----------------------|

| ✿ Debug ⊠                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        | 🖻 🐐 🕴 🗖 🗖                                                                                                              | cla                                                                | _ex1_asin_cpu1.c                     | 🖸 main()              |

| TMS320F28388D.ccxml [Code Composer Studio - Device Debugging]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |                                                                                                                        | \$ 228                                                             | Device_ini                           | t();                  |

| <ul> <li>Prexas Instruments XDS100v2 USB Debug Probe_0/C28xx_CPU1 (Suspended - main() at cla_ex1_asin_cpu1.c:85 0x009289</li> <li>_args_main() at args_main.c:133 0x0093E0</li> <li>_c_int00() at boot28.asm:264 0x00914D (_c_int00 does not contain frame i v<sup>®</sup> Texas Instruments XDS100v2 USB Debug Probe_0/CPU1_CLA1 (Disconnected v Prexas Instruments XDS100v2 USB Debug Probe_0/C28xx_CPU2 (Suspended - main() at cla_ex1_asin_cpu2.c:228 0x00C525</li> <li>_args_main() at args_main.c:133 0x00C5FC</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | infor<br>: Uni<br>SW I | mation)<br>known)<br>Breakpoint)                                                                                       | 229<br>230<br>231<br>232<br>233<br>234<br>235<br>236<br>237<br>238 | // Initial<br>//<br>// This is<br>// | ize PIE               |

| ■ _c_int00() at boot28.asm:264 0x00C440 (_c_int00 does not contain frame i<br>■ Taura Instruments XPE100.2 USB Datus Picks 0/(CPU2 CLA1 / Disconstrated)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        | mation)                                                                                                                | 239                                                                | incerrape_                           |                       |

| x <sup>®</sup> Texas Instruments XDS100v2 USB Debug Probe_0/CPU2_CLA1 (Disconnected x <sup>®</sup> Texas Instruments XDS100v2 USB Debug Probe_0/Cortex_M4_0 (Disconnected and the second secon |                        | Connect Target<br>Disconnect Target<br>Enable Global Bre<br>Enable Halt On Re<br>Enable OS Debug<br>Open GEL Files Vie | get Ctrl+Al<br>Breakpoints<br>Reset Connect Target<br>ugging       |                                      | t+D ine<br>ine<br>ine |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ×                      | Code Analysis<br>SoC Analysis<br>Hide core(s)                                                                          |                                                                    |                                      | ); ve                 |

Run -> Load -> Load Symbols and select the cla\_ex1\_asin\_cpu2.out file.

All the cores are currently in halted state. Select each core and click "Run" to execute the application. The CPU1 application should be run before running the CPU2 application. Note that this application has breakpoints inserted in the CLA code, and hence will be halted once the breakpoint is hit.

All the debugging features such as run, halt, step into, step over, breakpoints etc are available for all the cores. Make sure you select the correct core before using the controls.

### 6.4 Viewing Memories/Registers/Expressions

All the CCS views available for viewing the memory contents such as Registers, Memory Browser, Expressions, Variables, Disassembly etc are shared across cores. The contents will vary based on the active core.

### 6.5 Exercise 1 - Multi-core Debug Example (continued)

Click on the CPU2 core, the registers view displays all the registers available on the CPU2 core.