# **C6000 Integration Workshop**

# Student Guide

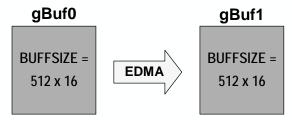

C6000 Integration Workshop Revision 3.1a August 2005

# **Important Notice**

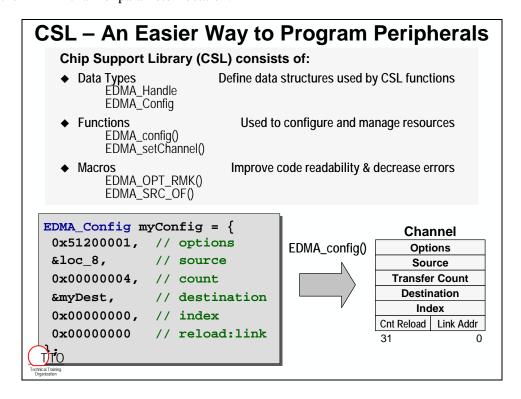

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2002, 2003, 2005 Texas Instruments Incorporated

# **Revision History**

November 2001 – Revision 0.1 (ALPHA)

March 2002 – Revision 0.8 (BETA)

April 2002 – Revision 1.0

May 2002 – Revision 1.1

June 2002 – Revision 1.2

October 2003 – Revision 2.0

April 2005 – Revision 2.1 (added Analog Interfacing – Mod 6.5)

August 2005 – Revision 3.1a (update to CCS 3.1, SIO/IOM, errata fixes)

# **Mailing Address**

Texas Instruments Training Technical Organization 7839 Churchill Way, M/S 3984 Dallas, Texas 75251-1903

# **Workshop Introduction**

## What Will You Accomplish This Week?

When you leave the workshop at the end of the week, you should be able to perform certain tasks and make critical assessments and decisions about the C6000s' capabilities. We developed this list based on customer feedback over the past 5 years and our own workshop design experience spanning the past 25 years. All of the modules exercises and labs support these accomplishments (as you'll see when we discuss the workshop's agenda).

The first two accomplishments are really the overall objectives of the entire workshop. Many students attend the workshop to meet these two needs. The rest of the list supports these two objectives and provides more insight into the expected outcomes. We hope this list meets or exceeds most of your expectations. If you think about it, we're going through the equivalent of a college semester course in 4 days! We obviously can't discuss everything given the time limitations, but we have provided the fastest path toward understanding, using and becoming confident in these activities.

# What Will You Accomplish?

When you leave the workshop, you should be able to...

- ◆ Evaluate C6000's ability to meet your system requirements

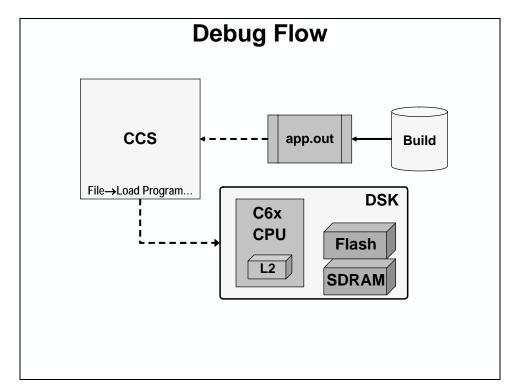

- Use <u>development tools</u> to compile, optimize, assemble, link, debug and benchmark code on the C6713 and C6416 DSKs

- **♦** Control response to real-time events using interrupts

- Configure peripherals to communicate with various devices

- ◆ Use <u>DSP/BIOS</u> APIs to perform various tasks in the system as well as analyze results

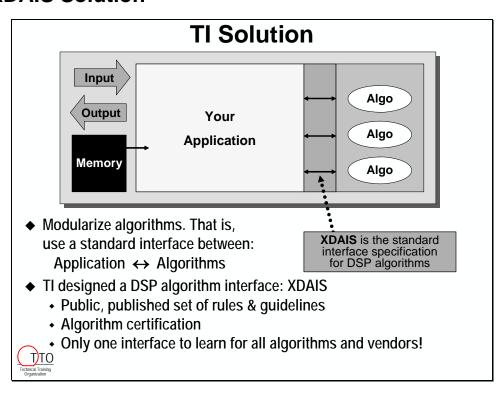

- ♦ Integrate an XDAIS algorithm into your system

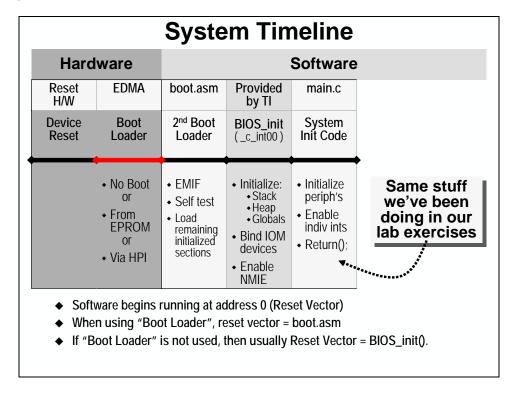

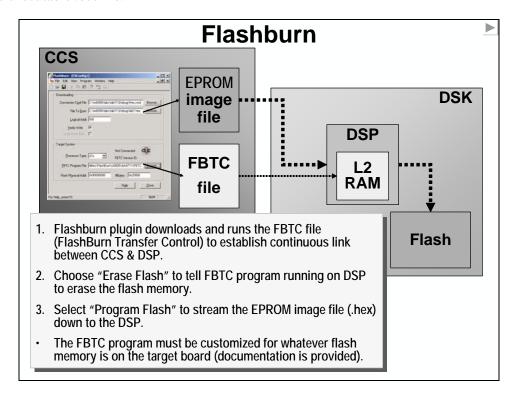

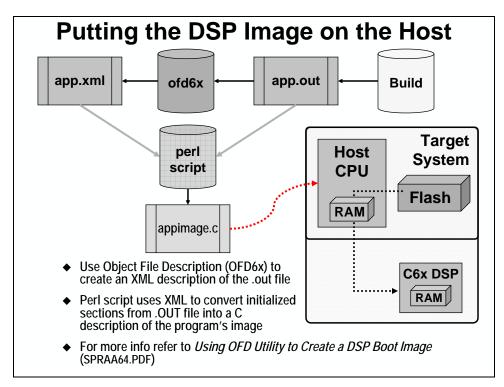

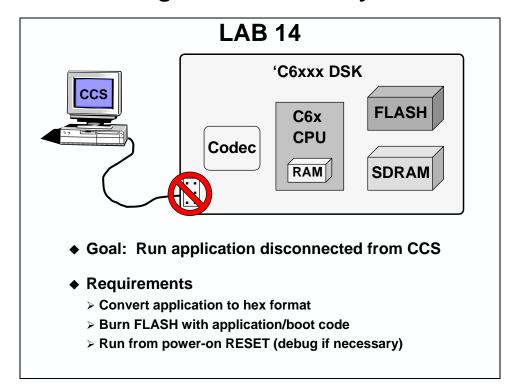

- Use the <u>bootloader</u> and <u>flash programming</u> tools to create a standalone system

- ◆ Understand other C6000 capabilities: EMIF, cache, HPI

So, if you're need falls "inside the box", be prepared to ask questions when the topic comes up. If your need falls "outside the box"...

### What We Won't Cover

It's very important to set the expectations of our student's right up front. This includes analyzing what we intend to discuss (accomplishments) as well as what we won't have time to cover. This leads us to the next discussion. We have chosen, based on time constraints, to explicitly *not* cover certain topics. Not only do we expect a certain level of knowledge coming into the workshop (pre-requisites such as some C programming, basic assembly, understanding basic engineering terms and system concepts, etc), we also want to specifically state what won't be covered during the week. This list includes DSP Theory, algorithms, and specific applications.

Regarding DSP Theory, we will not cover topics such as IIR/FIR filters, convolution, FFTs, and the rest of the topics addressed by the numerous DSP theory books and college courses. We assume that you know this theory if need to apply it. Our job is to show you *how* to use the device to accomplish these tasks (i.e. the CPU and peripherals) – instead of spending time showing the theory. We do not have time to dive into any one specific algorithm – such as PID, servo, VSELP, GSM, Viterbi, etc. If we did, it'd probably not be the one you wanted. We do provide details about on-chip hardware peripherals, which you can apply to the various hardware/software applications, required by your system – we just don't intend to show the details of any specific application.

# What We Won't Cover and Why...

What Will You Accomplish?

When you leave the workshop, you should be able to...

• Evaluate C6000's ability to meet your system requirements

• Use development tools to compile, optimize, assemble, link, debug and benchmark code on the C6711 DSK

• Control response to real-time events using interrupts

• Configure parioherals to communicate with various devices

• Use DSP/GIOS APIs to perform various tasks in the system as well as analyze results

• Integrate an XDAIS application into your system

• Use the bootloader and flash programming tools to create a standalone system

• Understand other C6000 capabilities: EMIF, cache, HPI

Issues "outside the box":

- ♦ DSP Theory / Algorithms

- Specific hardware and software applications

- Detailed ASM programming and Code Optimization

- Architectural details

### C6000 IW Workshop Scope and Depth

- ◆ In 4 days, it is impossible to cover everything. However, we do cover an equivalent of a college semester course on the C6000.

- We've chosen the "Accomplishments" list based on customer feedback and years of workshop experience.

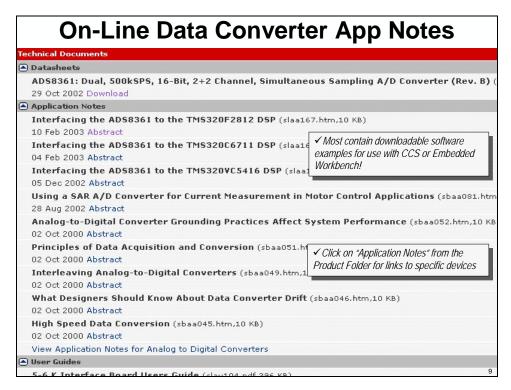

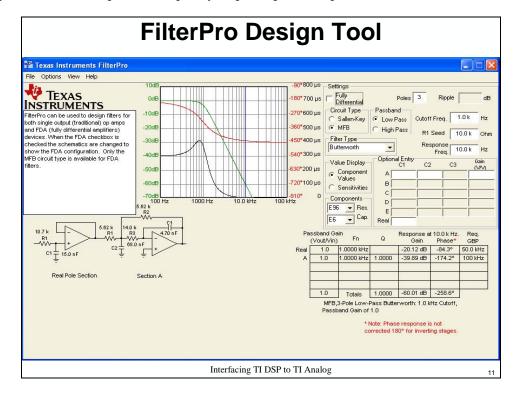

- Many app notes have been written to address specific topics not covered in the workshop (check out the TI website).

- ◆ If you have a need that falls "outside the box", please inform your instructor. Often, they can offer answers/ideas before or after class.

We've had to make some decisions about the material in the workshop based on time and what makes sense for all users. Many app notes have been written (and are available on the TI web site at http://www.dspvillage.com) which cover, in detail, many of the topics we cannot here. So, if you're need falls "outside the box" (i.e. in addition to the accomplishment list discussed previously), then you have two options: (1) ask the instructor if a manual or app note is available which addresses your specific issue; or, (2) let the instructor know before or after class time – we might be able to shed some light or direct you to other resources. If you communicate your need then we will do our best to fulfill it.

# **Workshop Outline**

On the first day of the workshop, you will be developing an audio application that requires you to set up the C6000 DMA and McBSP to send and receive audio from the PC. So, you get to hear "something" in the speakers by the end of the day. On Day 2, you will increase the complexity of the system by modifying your application to use a double-buffer instead of a single buffer. You will also be adding other threads to the system beyond the audio path and integrating a fully compliant XDAIS algorithm. On Days 3 and 4, we will cover many other system issues including EMIF, boot, cache, HPI. By the end of the workshop, you will be able to burn your application into the DSK's flash memory and boot from power-on reset *disconnected* from CCS. Wow!

# **Workshop Outline**

#### Day 1

- 1. Introduction

- 2. Code Composer Studio

- 3. Basic Memory Management

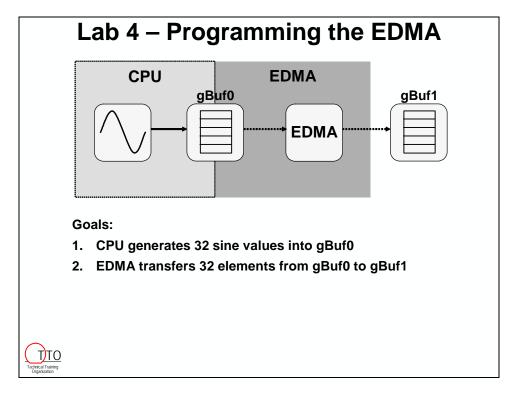

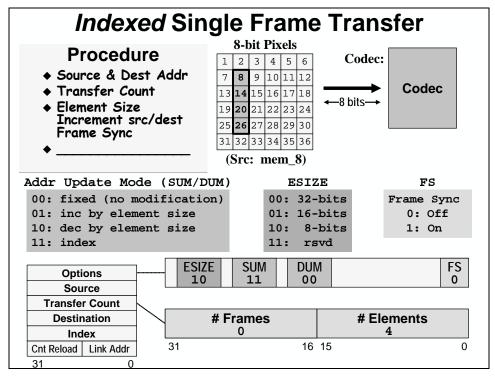

- 4. Using the EDMA (Intro to CSL)

### Day 2

- 5. Hardware Interrupts (HWI)

- 6. Configure and use McBSP

- 6.5 Analog Interfacing

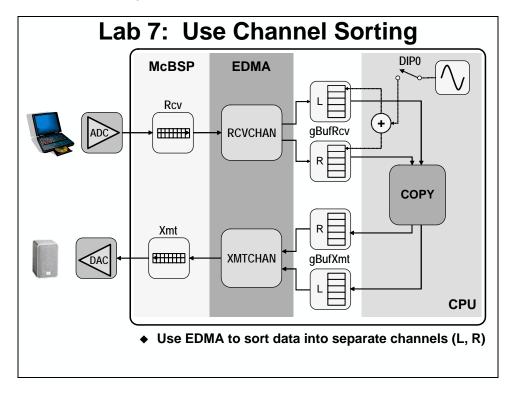

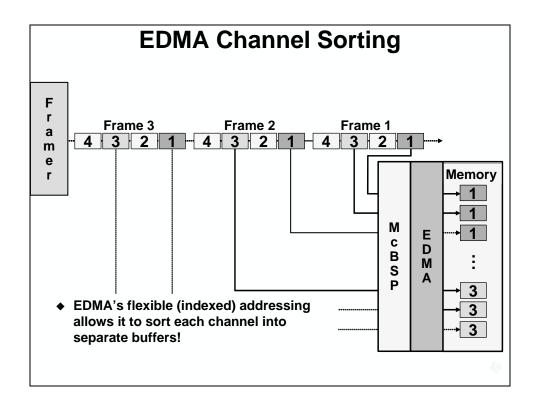

- 7. Channel Sorting using EDMA

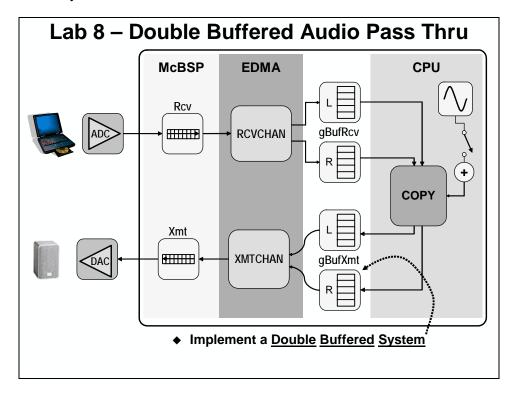

- 8. Using a Double Buffer

### Day 3

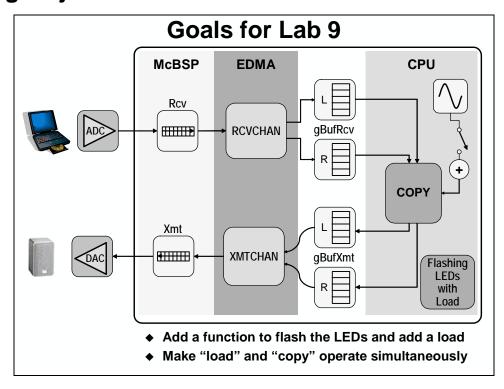

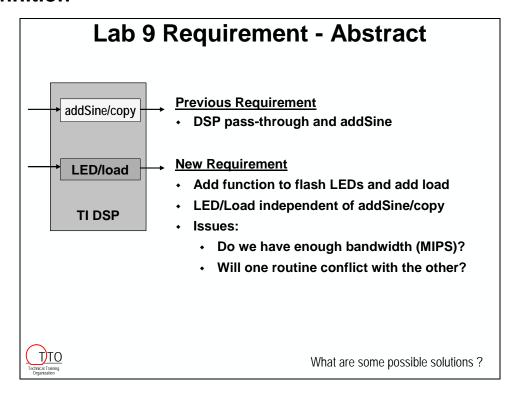

- 9. DSP/BIOS Scheduling

- 10. Advanced Memory Mgmt.

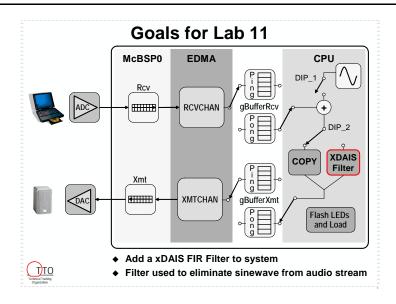

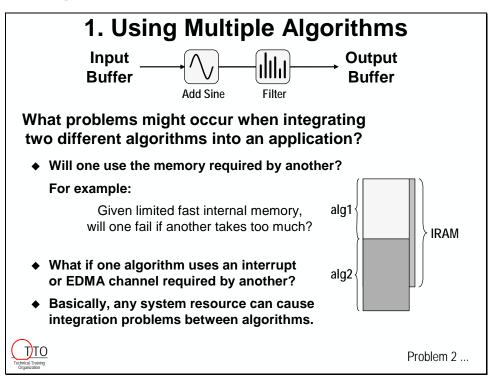

- 11. Integrating a XDAIS

Compliant Algorithm

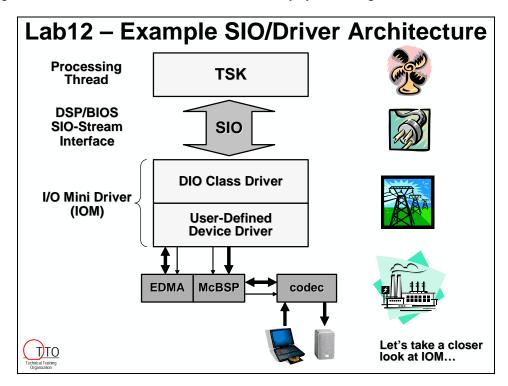

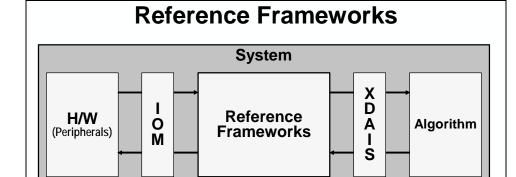

- 12. Using Reference Frameworks and IOM Device Drivers

- 13. External Memory Interface

### Day 4

- 14. Creating a Stand-alone System (Flash, Boot)

- 15. Using the Cache

- 16. Using the HPI

- 17. Wrap Up

The outline describes which day each module should fall within. Please understand, though, that each class moves at it's own pace, therefore, you may find the daily breakout differs in your workshop from that described above.

### Introductions

Learning more about you, your application, and your experience will help your instructor tailor the materials to the class needs. This is important since there is more information than can be taught during a single week.

## **Introduce Yourself**

# Briefly, a little about your application:

- Name & Company

- Application

- · Which C6000 DSP do you plan to use?

# And, a little about your experience:

- Do you have experience with:

- TI DSP's (TMS320)

- Another DSP

- Other microprocessors

- · C, Assembly, or both

- Have you used an OS or RTOS?

## TI DSP and 'C6x Family Positioning

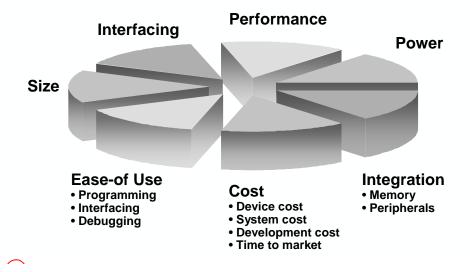

# Applications / System Needs

DSP systems today face a host of system needs:

These needs challenge the designer with a series of tradeoffs. For example, while performance is important in a portable MP3 player, more important would be efficiency of power dissipation and board space. On the other hand, a cellular base station might require higher performance to maximize the number of channels handled by each processor.

Wouldn't it be nice if the fastest DSP consumed the lowest amount of power? While TI is working on providing this (and making it software compatible), it provides you with a broad assortment of DSP families to cover a varying set of system needs. Think of them as different shoes for different chores ...

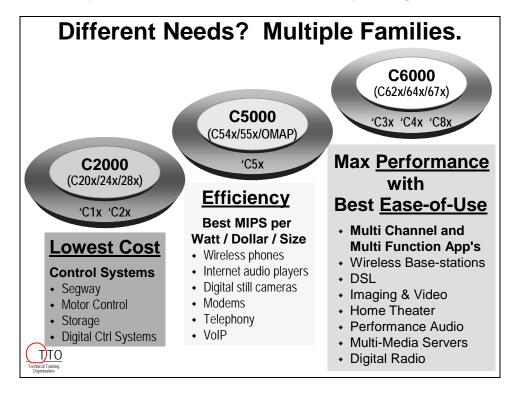

### **TI DSP Families**

TI provides a variety of DSP families to handle the tradeoffs in system requirements.

The TMS320C2000 ('C2000) family of devices is well suited to lower cost, microcontroller-oriented solutions. They are well suited to users who need a bit more performance than today's microcontrollers are able to provide, but still need the control-oriented peripherals and low cost.

The 'C5000 family is the model of processor efficiency. While they boast incredible performance numbers, they provide this with just as incredible low power dissipation. No wonder they are the favorites in most wireless phones, internet audio, and digital cameras (just to name a few).

Rounding out the offerings, the 'C6000 family provides the absolute maximum performance offered in DSP. Couple this with its phenomenal C compiler and you have one fast, easy-to-program DSP. When performance or time-to-market counts, this is the family to choose. It also happens to be the family the course was designed around, thus, the rest of the workshop will concentrate only on it.

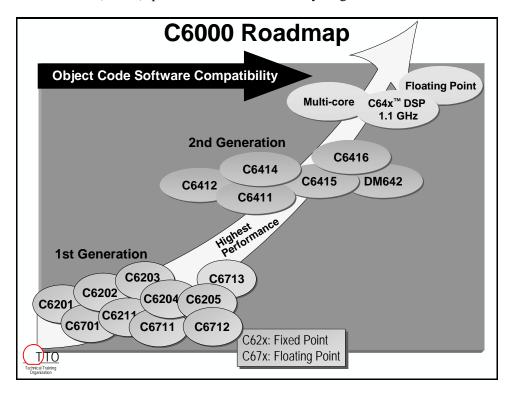

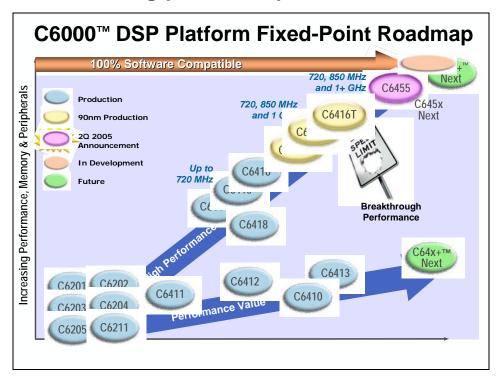

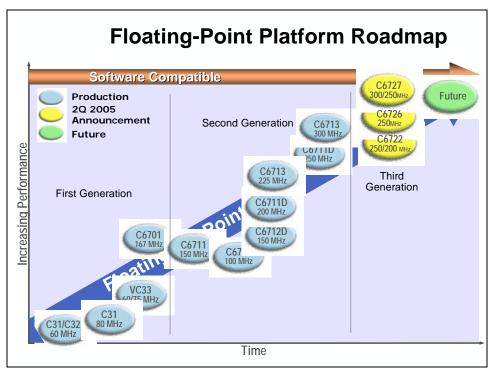

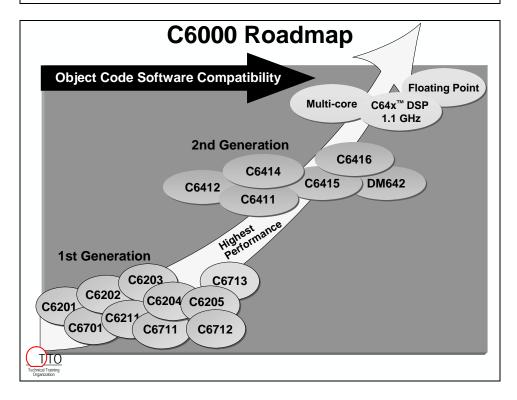

# 'C6000 Roadmap

The 'C6000 family has grown considerably over the past few years. With the addition of the 2<sup>nd</sup> generation of devices ('C64x), performance has increased yet again.

Yet, the ease of design within the 'C6000 architecture has not been abandoned with its growing family of devices. Software compatibility is addressed by the architecture, rather than by the hard-work of the programmer. With both the 'C67x and 'C64x devices being able to run 'C62x *object* code, upgrading DSP's is much easier.

# **Fixed- and Floating-pt Roadmaps**

## **Additional Information**

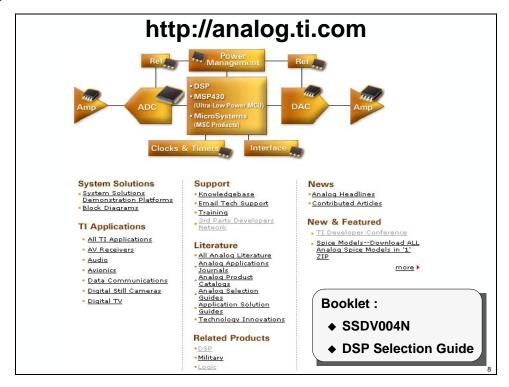

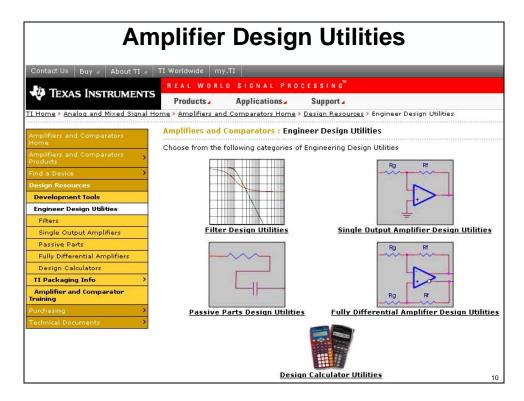

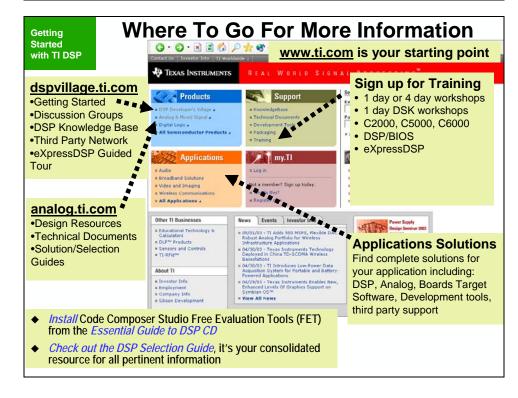

# For More Information and Support

For support we suggest you try TI's web site first. Then call your local support – either your local TI representative or Authorized Distributor Sales/FAE. Finally, here are a few other places to go for support and information:

## For More Information . . .

### Internet

Website: http://www.ti.com

http://www.dspvillage.com

FAQ: http://www-k.ext.ti.com/sc/technical\_support/knowledgebase.htm

Device information

my.ti.comNews and events

Application notesTechnical documentation

Training

Enroll in Technical Training: http://www.ti.com/sc/training

### **USA - Product Information Center (PIC)**

Phone: 800-477-8924 or 972-644-5580

Email: support@ti.com

Information and support for <u>all</u> TI Semiconductor products/tools

Submit suggestions and errata for tools, silicon and documents

## In Europe ...

## **European Product Information Center (EPIC)**

| European Froduct information center (EFTC) |                                                                                                                                                      |                                                                                                                                                                                                                                        |  |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Web:                                       | http://www-k.ext.ti.com/sc/technical_support/pic/euro.htm                                                                                            |                                                                                                                                                                                                                                        |  |

| Phone:                                     | Language Belgium (English) France Germany Israel (English) Italy Netherlands (English) Spain Sweden (English) United Kingdom                         | Number<br>+32 (0) 27 45 55 32<br>+33 (0) 1 30 70 11 64<br>+49 (0) 8161 80 33 11<br>1800 949 0107 (free phone)<br>800 79 11 37 (free phone)<br>+31 (0) 546 87 95 45<br>+34 902 35 40 28<br>+46 (0) 8587 555 22<br>+44 (0) 1604 66 33 99 |  |

|                                            | Finland (English)                                                                                                                                    | +358(0) 9 25 17 39 48                                                                                                                                                                                                                  |  |

| Fax:                                       | All Languages                                                                                                                                        | +49 (0) 8161 80 2045                                                                                                                                                                                                                   |  |

| Email:                                     | epic@ti.com                                                                                                                                          |                                                                                                                                                                                                                                        |  |

|                                            | <ul> <li>Literature, Sample Requests and Analog EVM Ordering</li> <li>Information, Technical and Design support for <u>all</u> Catalog TI</li> </ul> |                                                                                                                                                                                                                                        |  |

Information, Technical and Design support for <u>all</u> Catalog TI Semiconductor products/tools

Submit suggestions and errata for tools, silicon and documents

### For More Generic DSP Information

# **Looking for Literature on DSP?**

◆ "A Simple Approach to Digital Signal Processing" by Craig Marven and Gillian Ewers; ISBN 0-4711-5243-9

\* "DSP Primer (Primer Series)" by C. Britton Rorabaugh; ISBN 0-0705-4004-7

◆ "A DSP Primer: With Applications to Digital Audio and Computer Music"

by Ken Steiglitz; ISBN 0-8053-1684-1

◆ "DSP First: A Multimedia Approach" James H. McClellan, Ronald W. Schafer, Mark A. Yoder; ISBN 0-1324-3171-8

# Looking for Books on 'C6000 DSP?

◆ "Digital Signal Processing Implementation using the TMS320C6000TM DSP Platform" by Naim Dahnoun; ISBN 0201-61916-4

"C6x-Based Digital Signal Processing"

by Nasser Kehtarnavaz and Burc Simsek;

ISBN 0-13-088310-7

◆ "Real-Time Digital Signal Processing: Based on the TMS320C6000" by Nasser Kehtarnavaz; Newnes; Book & CD-Rom (July 14, 2004) ISBN 0-7506-7830-5

"Digital Signal Processing and Applications with the C6713 and C6416 DSK (Topics in Digital Signal Processing)" Wiley-Interscience; Book & CD-Rom (December 3, 2004 by Rulph Chassaing; ISBN 0-4716-9007-4

# **Key TI Manuals**

# **Key C6000 Manuals**

### **Hardware**

SPRU189 - CPU and Instruction Set Ref. Guide

SPRU190 - Peripherals Ref. Guide

SPRZ122 - SPRU190 Manual Update Sheet (important!)

SPRU401 - Peripherals Chip Support Lib. Ref.

SPRU609 - C67x Two-Level Internal Memory Reference SPRU610 - C64x Two-Level Internal Memory Reference

SPRU656 - Cache Memory Users Guide

### **Software**

SPRU198 - Programmer's Guide

SPRU423 - C6000 DSP/BIOS User's Guide SPRU403 - C6000 DSP/BIOS API Guide

## **Code Generation Tools**

SPRU186 - Assembly Language Tools User's Guide

SPRU187 - Optimizing C Compiler User's Guide

Refer to the C6000 Product Update handout for full list

# **TI DSP Workshops**

# **DSP Workshops Available from TI**

- ◆ Attend another workshop:

- 4-day C2000 Workshops

- 4-day C5000 Integration Workshops

- 4-day C6000 Integration Workshop

- 4-day C6000 Optimization Workshop

- 4-day DSP/BIOS Workshop

- 4-day OMAP Software Workshop

- 1-day Workshops (C2000, C5000, C6000)

- 1-day Reference Frameworks and XDAIS

- ♦ Sign up at:

Technical Training

http://www.ti.com/sc/training

| C6000 Workshop Comparison                                         |        |        |  |

|-------------------------------------------------------------------|--------|--------|--|

| Audience                                                          | IW6000 | OP6000 |  |

| Algorithm Coding and Optimization                                 |        | ✓      |  |

| System Integration (data I/O, peripherals, real-scheduling, etc.) | ✓      |        |  |

| C6000 Hardware                                                    |        |        |  |

| CPU Architecture & Pipeline Details                               |        | ✓      |  |

| Using Peripherals (EDMA, McBSP, EMIF, HPI, XBUS)                  | ✓      |        |  |

| Tools                                                             |        |        |  |

| Compiler Optimizer, Assembly Optimizer, Profiler, PBC             |        | ✓      |  |

| CSL, Hex6x, Absolute Lister, Flashburn, BSL                       | ✓      |        |  |

| Coding & System Topics                                            |        |        |  |

| C Performance Techniques, Adv. C Runtime Environment              |        | ✓      |  |

| Calling Assembly From C, Programming in Linear Asm                |        | ✓      |  |

| Software Pipelining Loops                                         |        | ✓      |  |

| DSP/BIOS, Real-Time Analysis, Reference Frameworks                | ✓      |        |  |

|                                                                   | ./     |        |  |

# **Administrative Details**

# **Administrative Topics**

- ♦ What you have in front of you

- ♦ Name Cards

- ♦ Sign-in Sheet

- **◆** Refreshments

- ◆ Facilities

- ♦ Phones

- ◆ Lunch

- ◆ Cell Phones please silence them

\*\*\* this page is not blank...it's an optical illusion...\*\*\*

# **C6000 Introduction**

# Introduction

This chapter introduces the TMS320C6000 (C6000) DSP architecture and peripherals as well as the C6416 and C6713 DSP Starter Kit's (DSK's).

The chapter ends with a simple lab to setup the (DSK) and Code Composer Studio (CCS). We like to start small and easy and then build to much more complicated topics and exercises later.

# **Learning Objectives**

Introduction to the:

- C6000 CPU Architecture

- C6000 Peripherals

- C6000 DSK's

# **Chapter Topics**

| C6000 Introduction                   | 1-1  |

|--------------------------------------|------|

| What Problem are we Trying to Solve  |      |

| Goals of 'C6000 Architecture         | 1-3  |

| C6000 Architecture                   |      |

| CPU Architecture Overview            | 1-5  |

| The C6000 (zooming out from the CPU) | 1-8  |

| Connecting to a C6000 Device         |      |

| C6000 DSK's                          | 1-14 |

| Overview                             |      |

| DSK Diagnostic Utility               |      |

| Memory Map                           |      |

| In the DSK Package                   |      |

| Lab 1 - Prepare Lab Workstation      | 1-19 |

| C64x or C67x Exercises?              |      |

| Computer Login                       | 1-21 |

| Connecting the DSK to your PC        |      |

| Testing Your Connection              |      |

| CCS Setup                            |      |

| Set up CCS – Customize Options       |      |

| Appendix (For Reference Only)        | 1-31 |

| Power On Self-Test stages            |      |

| DSK Help                             | 1-32 |

# What Problem are we Trying to Solve

### Goals of 'C6000 Architecture

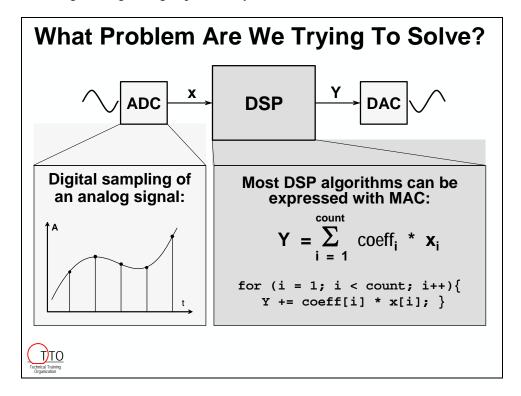

Conundrum: How to define Digital Signal Processing (DSP) in one slide.

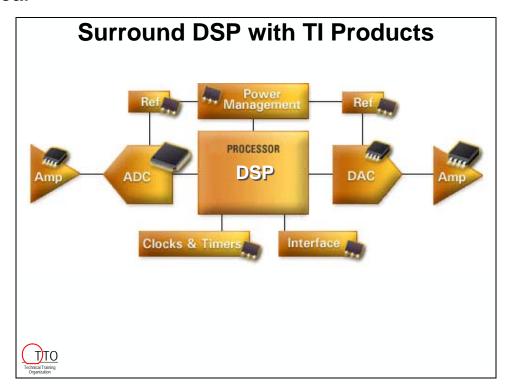

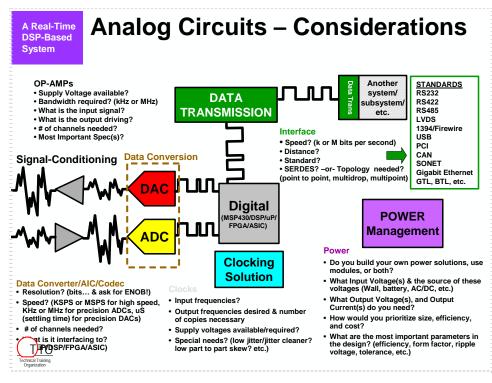

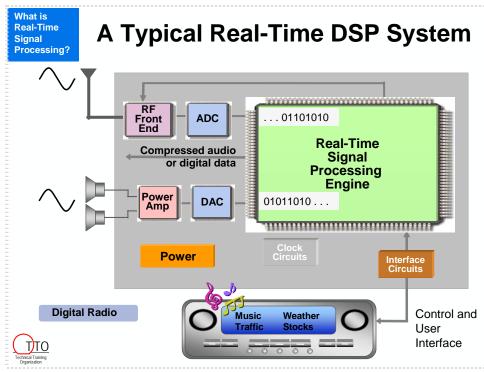

In its simplest form, most DSP systems receive data from an ADC (analog to digital converter). The data is processed by the Digital Signal Processor (also called DSP) and the results are then transformed back to analog to be output. Digitizing the analog signal (by evaluating it to a number on a periodic basis) and the subsequent numerical (a.k.a. digital) analysis provides a more reliable and efficient means of manipulating the signal vs. performing the manipulation in the analog domain. With the growing interest in multimedia, the demand for DSPs to process the various media signals is growing exponentially.

While interest in DSP is constantly growing today, the DSProcessor grew out of TI over 20 years ago in its educational products group, namely the *Speak and Spell*. These products demanded speech synthesis and other traditional DSProcessing (like filters) but with quick time-to-market constraints.

The heart of DSP algorithms hasn't changed from the early days of TI DSP; they still rely on the fundamental difference equation (shown above). Often this equation is referred to as a MAC (multiply-accumulate) or SOP (sum-of-products). TI has concentrated for years on providing solutions to MAC based algorithms. The wide variety of TI DSPs is a testament to this focus, even with the widely varying system tradeoffs discussed earlier.

For the 'C6000 to achieve its goal, TI wanted to provide record setting performance while coding with the universal ANSI C language.

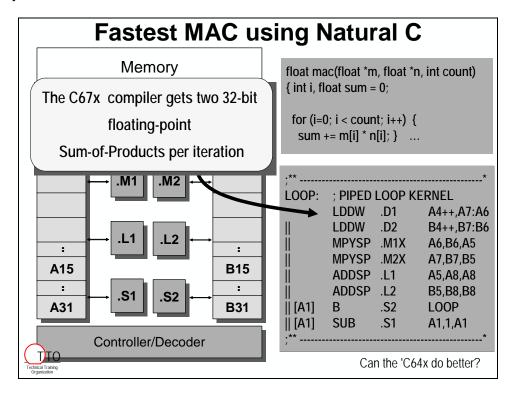

# Fast MAC using only C

### Multiply-Accumulate (MAC) in Natural C Code

```

for (i = 1; i < count; i++){

Y += coeff[i] * x[i]; }</pre>

```

- Fastest Execution of MACs

- The 'C6x roadmap ... from 200 to 4000 MMACs

- **♦** Ease of C Programming

- Even using natural C, the 'C6000 Architecture can perform 2 to 4 MACs per cycle

- · Compiler generates 80-100% efficient code

How does the 'C6000 achieve such performance from C?

TI 'C6000 devices deliver 200 to 4000 MMACs of performance, where MMAC is mega-MAC or millions of MACs. It's stellar performance, in any case. When this can be achieved using C code, it's even better. While providing efficiency ratings for a compiler is difficult, TI has benchmarked a large number of common DSP kernels to provide an example of the compiler's efficiency please visit the TI website for more information and benchmarking examples.

## **C6000 Architecture**

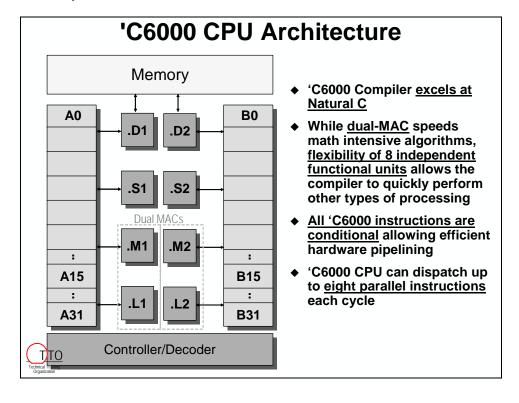

## **CPU Architecture Overview**

How does the 'C6000 deliver its performance, the CPU is built to dispatch 8 instructions per cycle – and the cycle rates run as fast as about 1 ns.

The following example demonstrates the capability of the 'C6000 architecture. Specifically, the 'C67x floating-point DSP can execute these eight instructions in parallel, allowing two single-precision floating point MACs to be performed in just one processor cycle. Oh, and all that from ordinary C code.

How does it look from a benchmark perspective?

| Algorithm                                                                                                                                                               | Used In                               | Asm<br>Cycles | Assembly<br>Time (μs) | C Cycles<br>(Rel 4.0) | C Time (μs) | % Efficiency<br>vs<br>Hand Codeo |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------|-----------------------|-----------------------|-------------|----------------------------------|

| Block Mean Square Error<br>MSE of a 20 column<br>image matrix                                                                                                           | For motion compensation of image data | 348           | 1.16                  | 402                   | 1.34        | 87%                              |

| Codebook Search                                                                                                                                                         | CELP based<br>voice coders            | 977           | 3.26                  | 961                   | 3.20        | 100%                             |

| Vector Max<br>40 element input vector                                                                                                                                   | Search<br>Algorithms                  | 61            | 0.20                  | 59                    | 0.20        | 100%                             |

| All-zero FIR Filter<br>40 samples,<br>10 coefficients                                                                                                                   | VSELP based voice coders              | 238           | 0.79                  | 280                   | 0.93        | 85%                              |

| Minimum Error Search Table Size = 2304                                                                                                                                  | Search<br>Algorithms                  | 1185          | 3.95                  | 1318                  | 4.39        | 90%                              |

| IIR Filter<br>16 coefficients                                                                                                                                           | Filter                                | 43            | 0.14                  | 38                    | 0.13        | 100%                             |

| IIR – cascaded biquads<br>10 Cascaded biquads<br>(Direct Form II)                                                                                                       | Filter                                | 70            | 0.23                  | 75                    | 0.25        | 93%                              |

| MAC<br>Two 40 sample vectors                                                                                                                                            | VSELP based<br>voice coders           | 61            | 0.20                  | 58                    | 0.19        | 100%                             |

| Vector Sum<br>Two 44                                                                                                                                                    |                                       | E4            | 0.17                  | 47                    | 0.16        | 100%                             |

| MSE be element ◆ Code available at dspvillage.com  Great out-of-box experience  Completely natural C code (non 'C6000 specific)  Code available at dspvillage.com  100% |                                       |               |                       |                       |             |                                  |

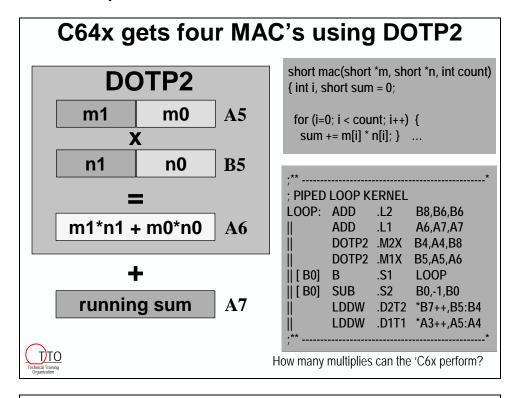

The C64x devices provide tremendous Multiply-Accumulate performance. Not only are they running at frequencies 2-3 times faster than other C6000 processors, but each of the multiply units can now perform two 16x16 multiplies plus a 32-bit add in one cycle. This is accomplished by the DOTP2 assembly instruction

# MMAC's

♦ How many 16-bit MMACs (millions of MACs per second) can the 'C6201 perform?

**400 MMACs** (two .M units x 200 MHz)

♦ How about 16x16 MMAC's on the 'C64x devices?

♦ How many 8-bit MMACs on the 'C64x?

8000 MMACs (on 8-bit data)

# The C6000 (zooming out from the CPU)

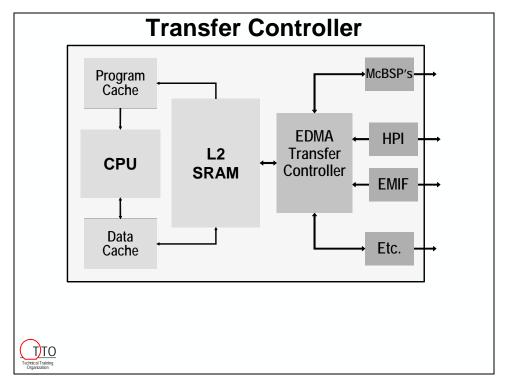

Zooming out from the CPU, we find a number of internal busses connected to it. The peripherals shown here will be discussed next.

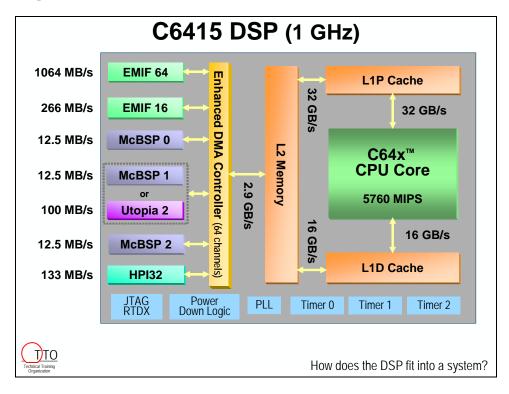

As an example, here is an internal view of the C6415 device:

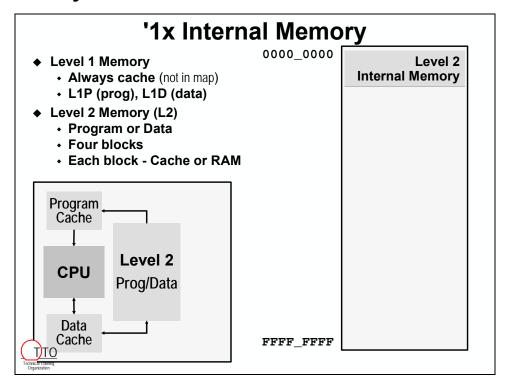

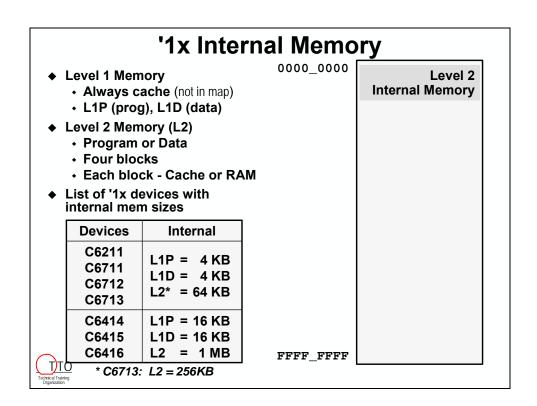

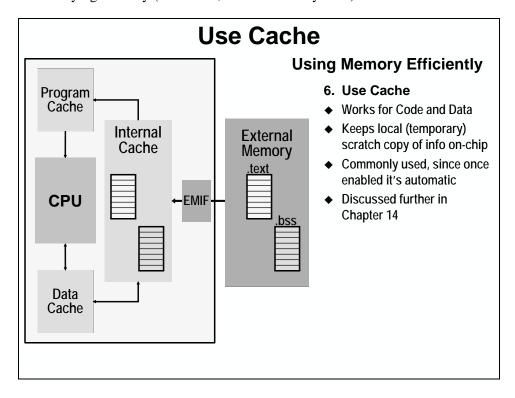

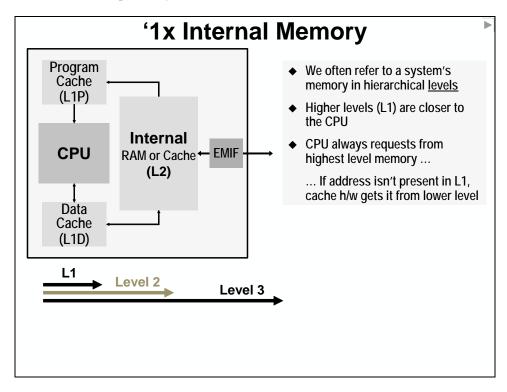

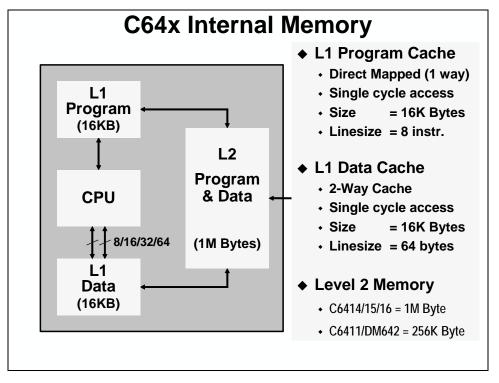

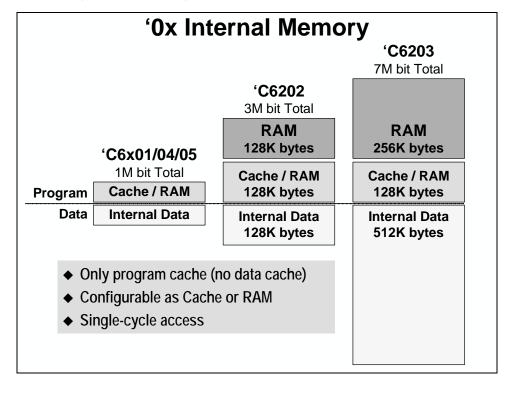

From this diagram notice two things:

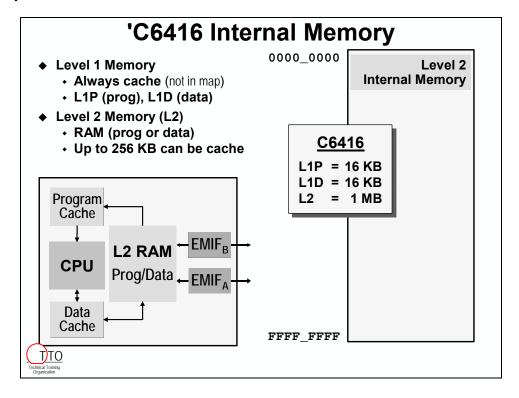

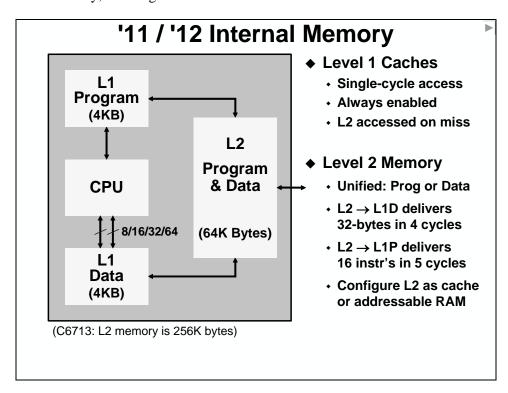

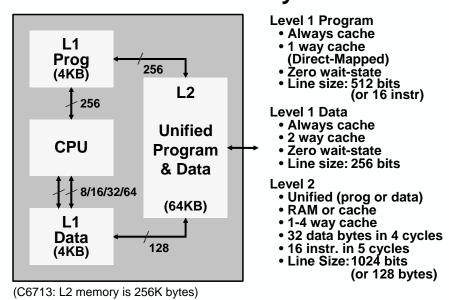

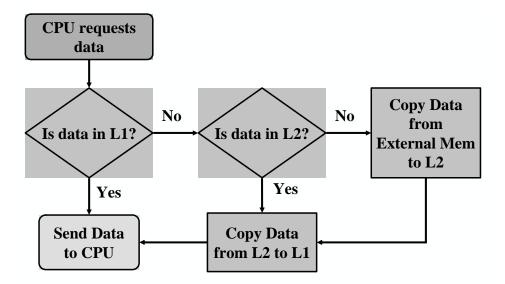

- Dual-level memory (this will be discussed further in Chapter 4):

- L1 (level 1) program and data caches

- L2 (level 2) combined program/data memory

- High-performance, internal buses

- Buses as large as 64- and 256-bits allow an enormous amounts of info to be moved

- Multiple buses allow simultaneous movement of data in a C6000 system

- Both the EDMA and CPU can orchestrate moving information

**Note:** While we have been looking into the C6415, you can extrapolate these same concepts to other C6000 device types. All device types have multiple, fast, internal buses. Most have a dual-level memory architecture, while a few have a single-level, flat memory.

# Connecting to a C6000 Device

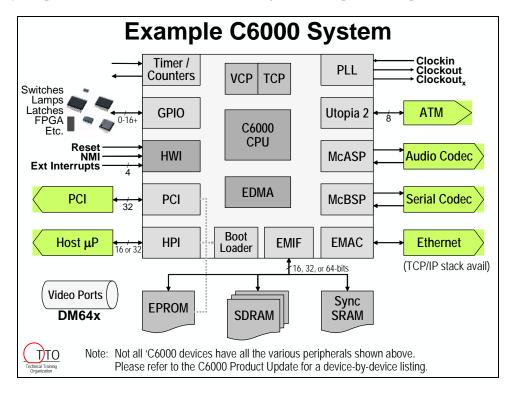

C6000 devices contain a variety of peripherals to allow easy communication with off-chip memory, co-processors, and other devices. The diagram below provides a quick overview:

Let's quickly look at each of these connections beginning with VCP/TCP and working counterclockwise around the diagram.

## **Viterbi Coprocessor (VCP)**

- Used for 3G Wireless applications

- Supports >500 voice channels at 8 kbps

- Programmable decoder parameters include constraint length, code rate, and frame length

- Available on the 'C6416

## **Turbo Coprocessor (TCP)**

- Used for 3G Wireless applications

- Supports 35 data channels at 384 kbps

- 3GPP / IS2000 Turbo coder

- Programmable parameters include mode, rate and frame length

- Available on the 'C6416

### **Timer / Counters**

- Two (or three) 32-bit timer/counters

- Use as a Counter (counting pulses from input pin) or as a Timer (counting internal clock pulses)

- Can generate:

- Interrupts to CPU

- Events to DMA/EDMA

- Pulse or toggle-value on output pin

- Each timer/counter as both input and output pin

### **General Purpose Input/Output (GPIO)**

- Observe or control the signal of a single-pin

- Dedicated GPIO pins on 'C6713 and all 'C64x devices

- All 'C6000 devices have shared GPIO with unused peripheral pins

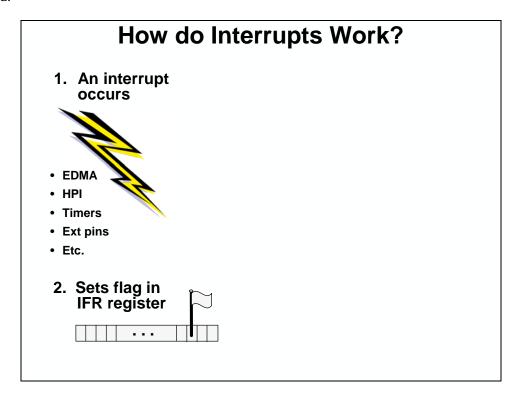

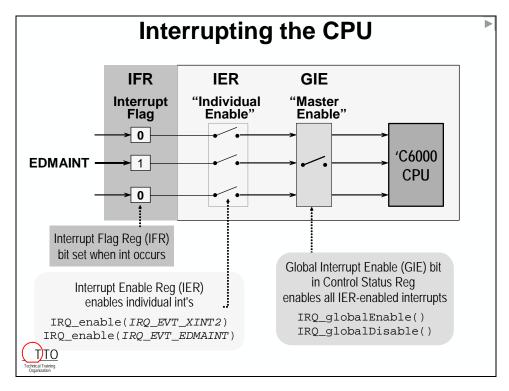

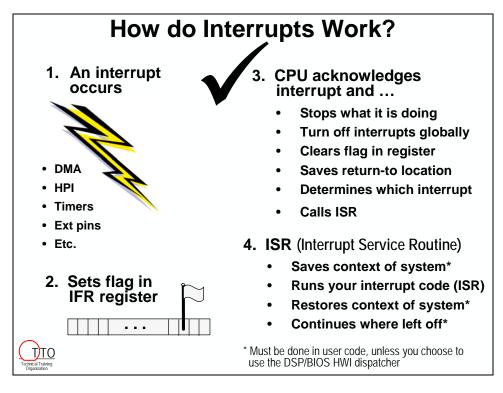

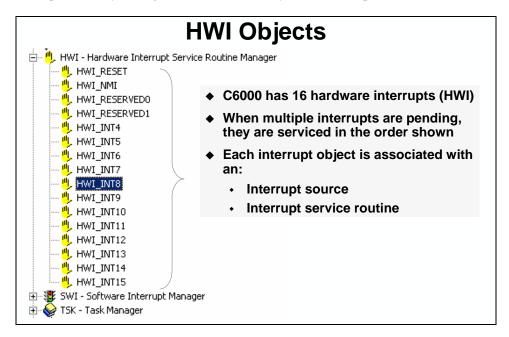

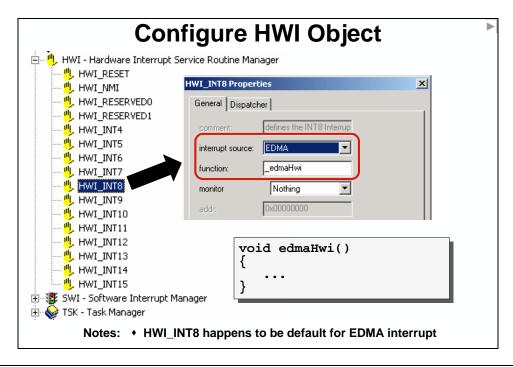

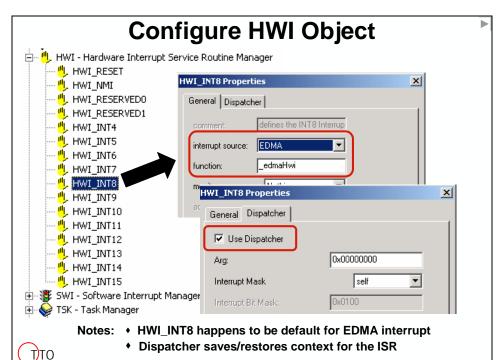

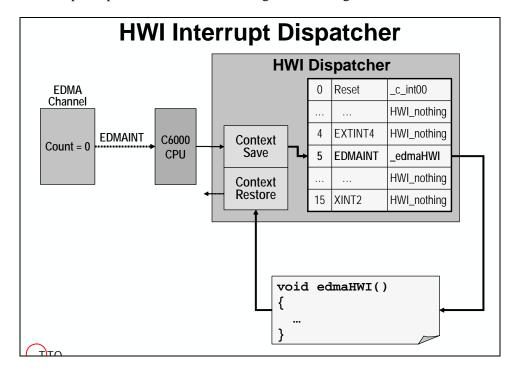

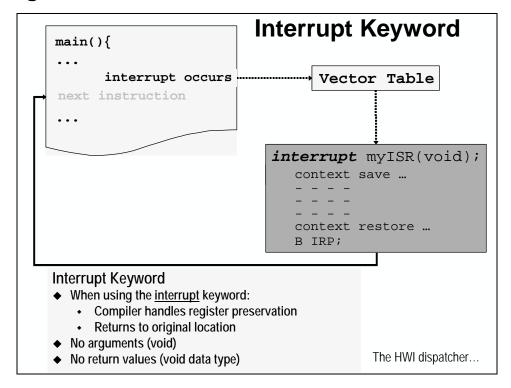

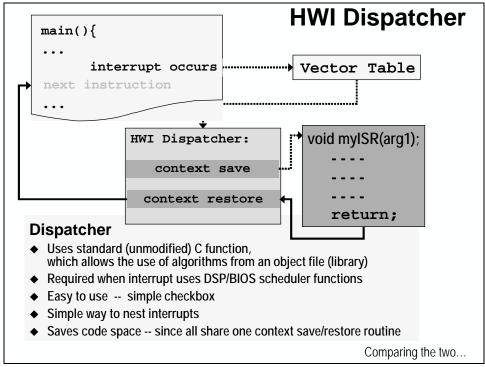

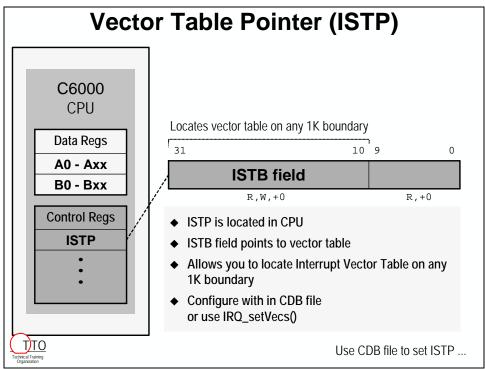

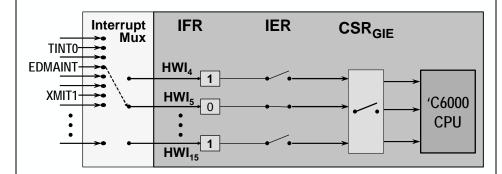

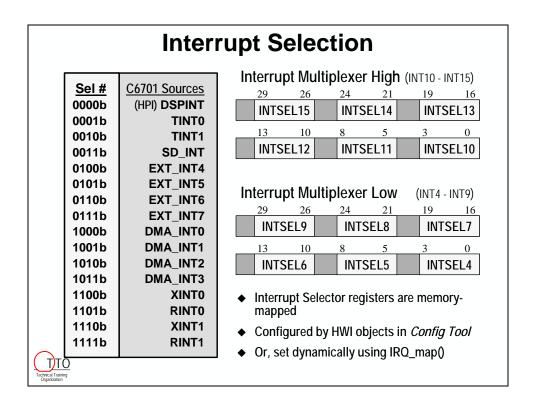

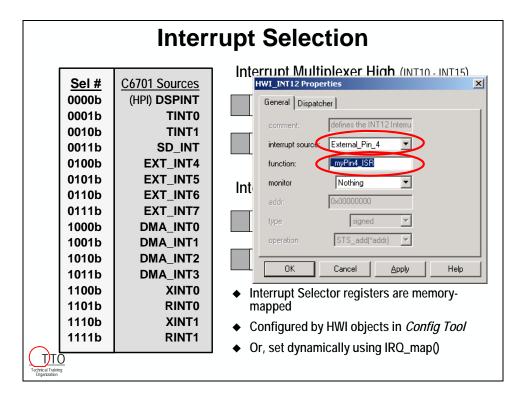

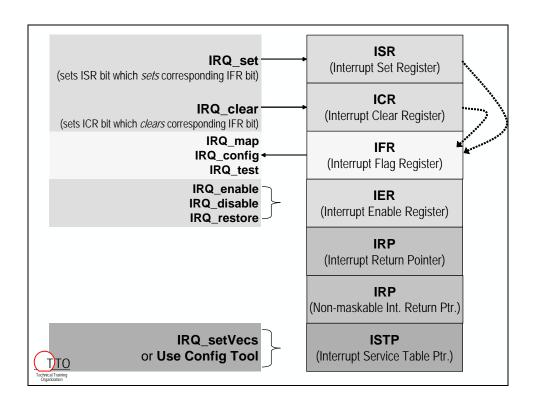

### **Hardware Interrupts (HWI)**

- Allows synchronization with outside world:

- Four configurable external interrupt pins

- One Non-Maskable Interrupt (NMI) pin

- Reset pin

- C6000 CPU has 12 configurable interrupts.

Some of the properties that can be configured are:

- Interrupt source (for example: Ext Int pin, McBSP receive, HPI, etc.)

- Address of Interrupt Service Routine (i.e. interrupt vector)

- Whether to use the HWI dispatcher

- Interrupt nesting

- The DSP/BIOS HWI Dispatcher makes interrupts easy to use

## **Parallel Peripheral Interface**

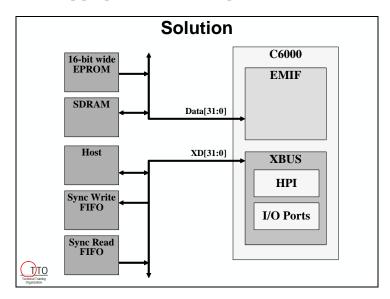

- C6000 provides three different parallel peripheral interfaces; the one you have depends upon which C6000 device you are using (see *C6000 Product Update* for which device has which interface)

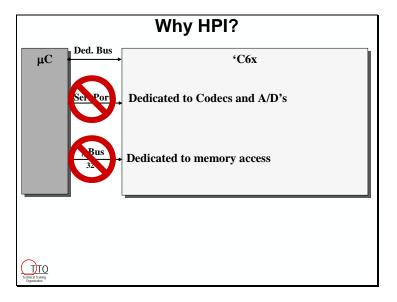

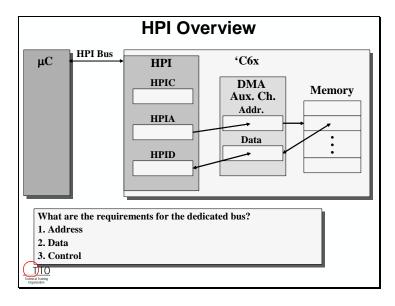

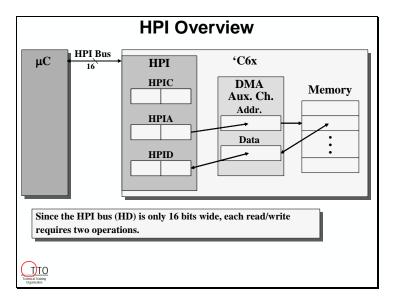

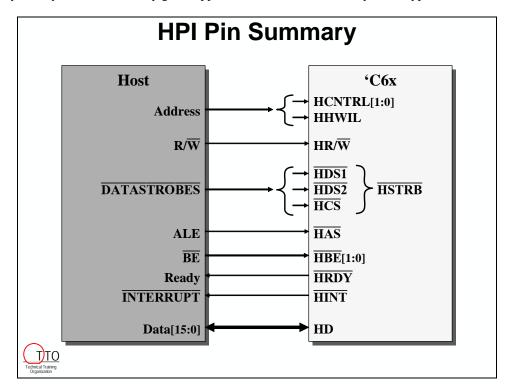

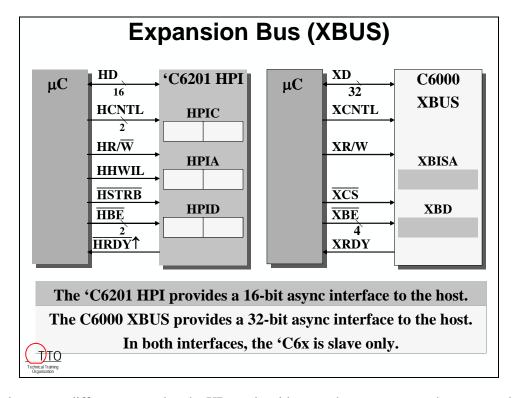

- HPI: Allows another processor access to C6000's memory using a dedicated, async 16/32-bit bus; where C6000 is slave-only to host.

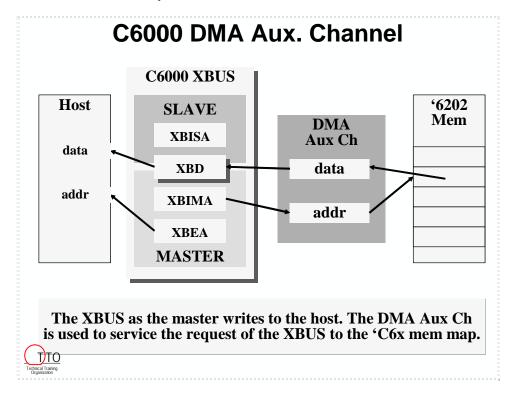

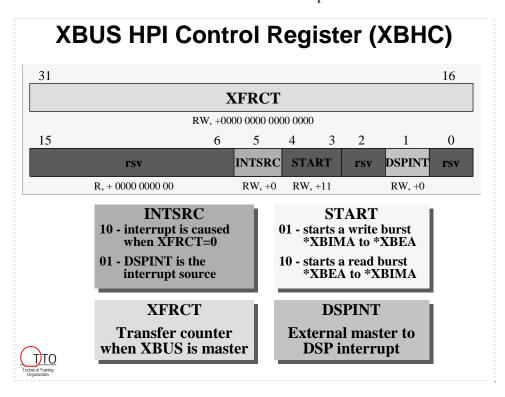

- XBUS: Similar to HPI but provides but adds: 32-bit width, Master or slave modes, sync modes, and glueless I/O interface to FIFOs or memory (memory I/O can transfer up to full processor rates, i.e. single-cycle transfer rate).

- PCI: Standard master/slave 32-bit PCI interface (latest devices e.g. DM642 now allow 66MHz PCI communication)

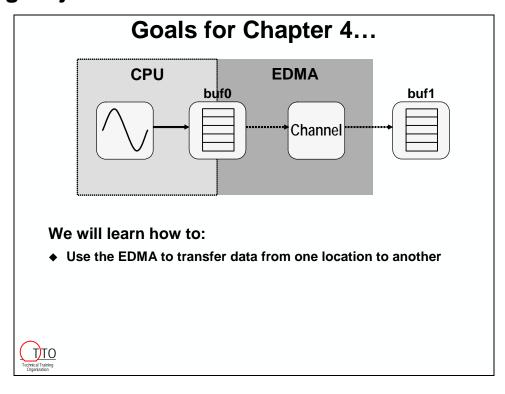

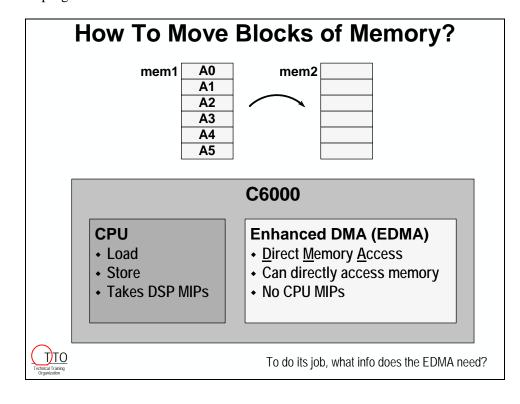

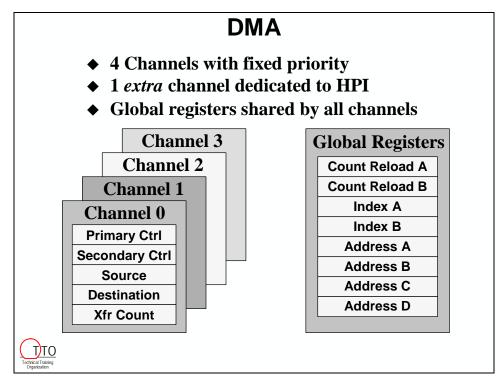

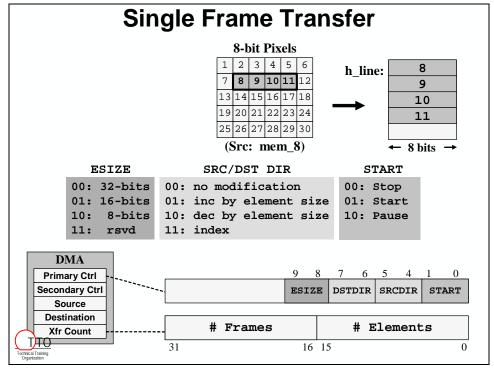

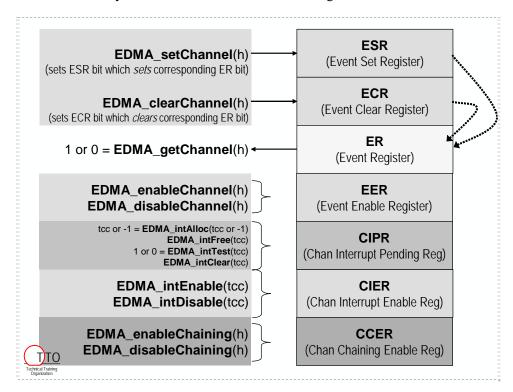

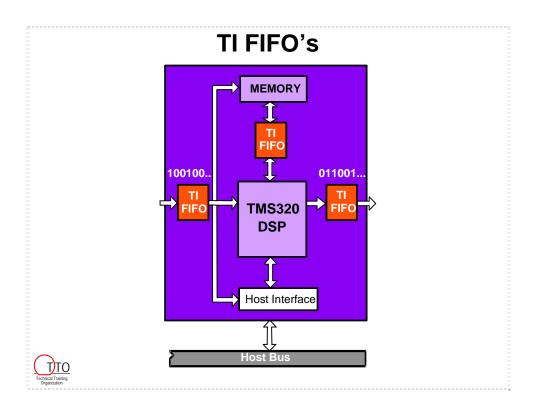

## **Direct Memory Access (DMA / EDMA)**

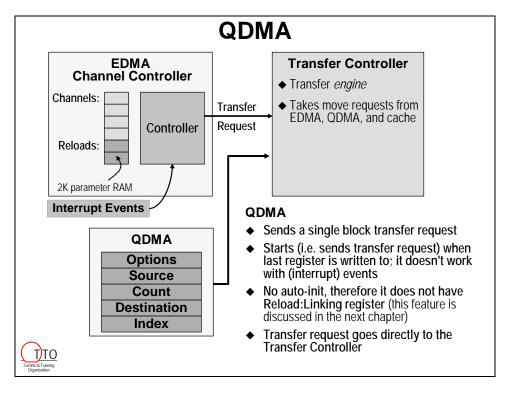

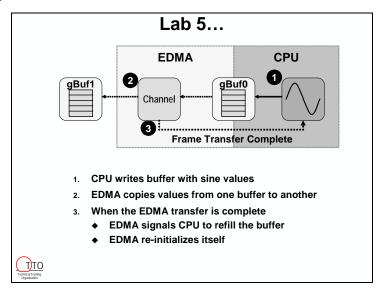

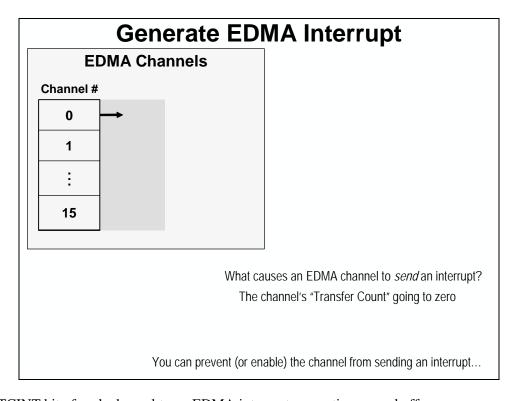

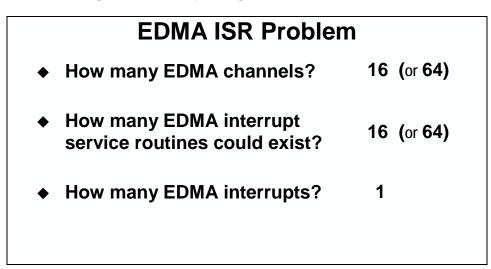

- EDMA stands for the Enhanced DMA (each C6000 has either a DMA or EDMA)

- Transfers any set of memory locations to any another (internal or external)

- Allows synchronized transfers; that is, they can be triggered by any event (i.e. interrupt)

- Operates independent of CPU

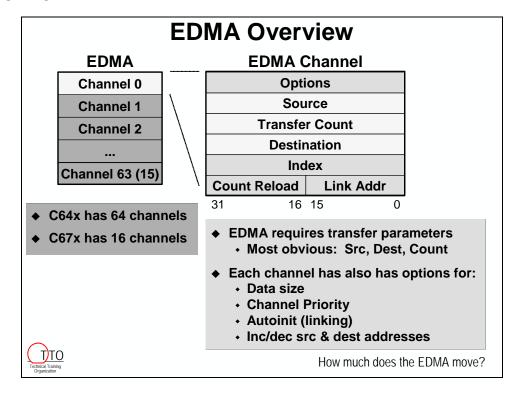

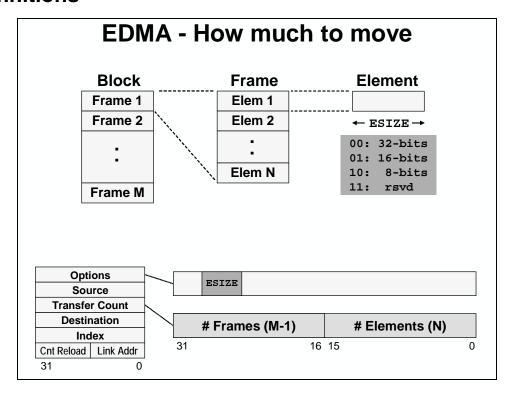

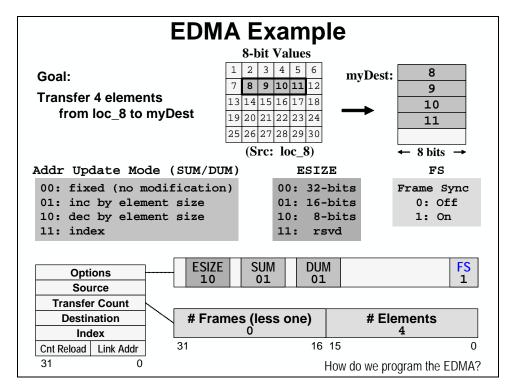

- 4 / 16 / 64 channels (set's of transfer parameters) (various by C6000 device type)

- "If you are not using the DMA/EDMA, you're probably not getting the full performance from your 'C6000 device."

DMA: Offers four fully configurable channels (additional channel for the HPI), Event synchronization, Split mode for use with McBSP, and Address/count reload

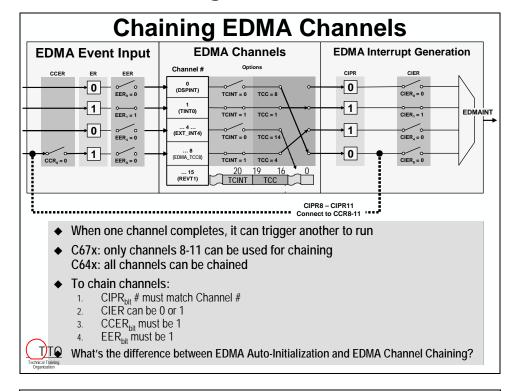

EDMA: Enhanced DMA (EDMA) offers 16 fully configurable channels (64 channels on 'C64x devices), Event synchronization, Channel linking, and Channel autoinitialization.

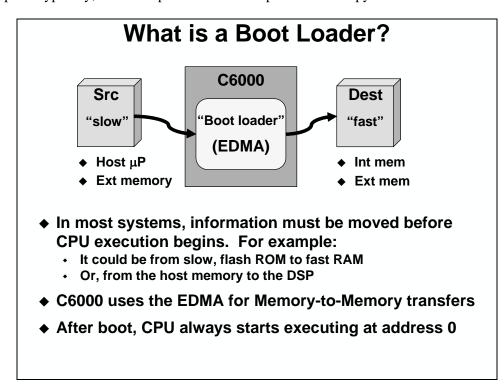

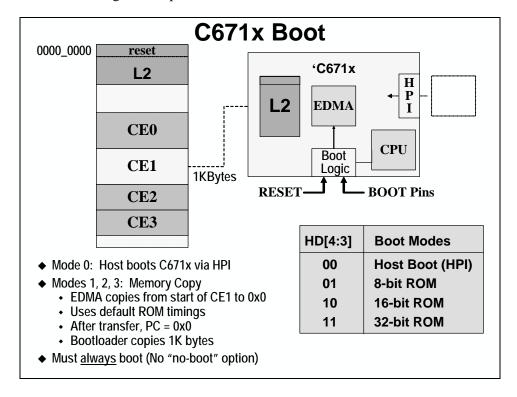

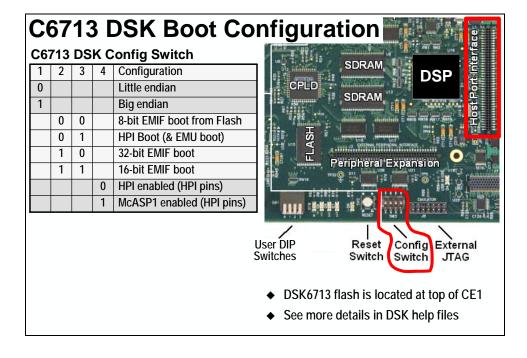

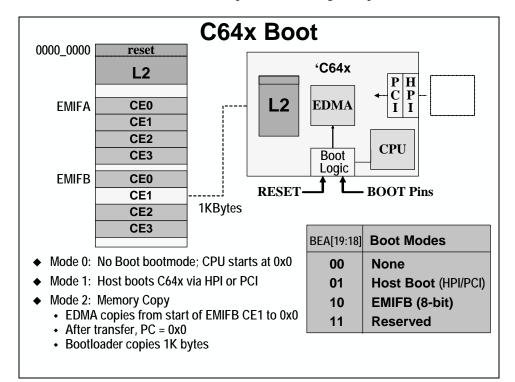

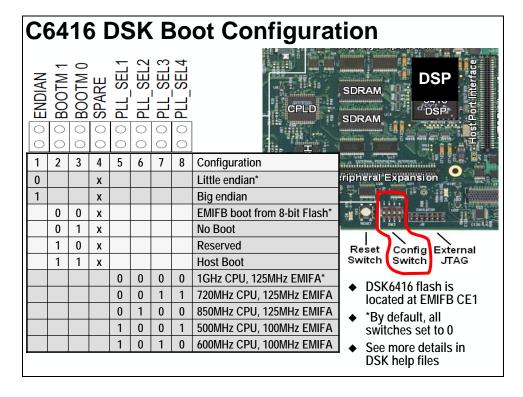

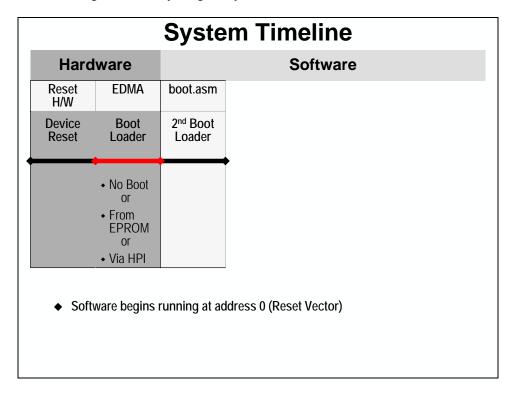

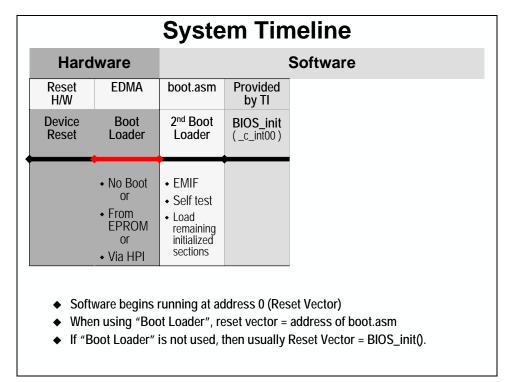

### **Boot Loader**

- After reset but before the CPU begins running code, the "Boot Loader" can be configured to either:

- Automatically copy code and data into on-chip memory

- Allow a host system (via HPI, XBUS, or PCI) to read/write code and data into the C6000's internal and external memory

- Do nothing and let the CPU immediately begin execution from address zero

- Boot mode pins allow configuration

- Please refer to the C6000 Peripherals Guide and each device's data sheet for the modes allowed for each specific device.

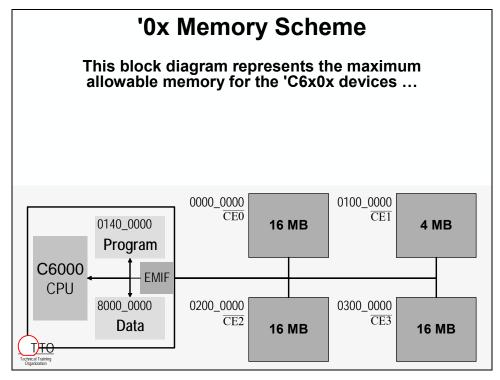

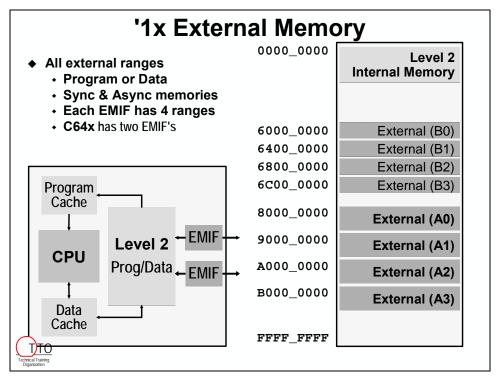

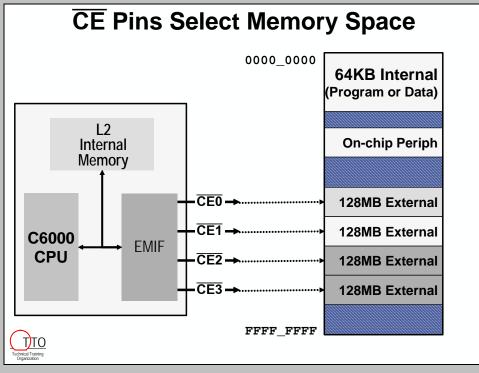

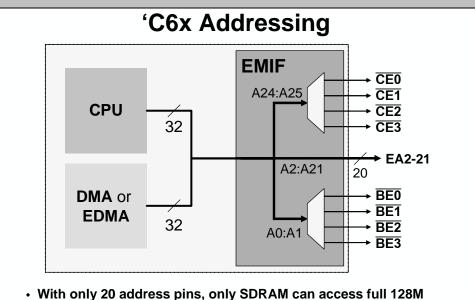

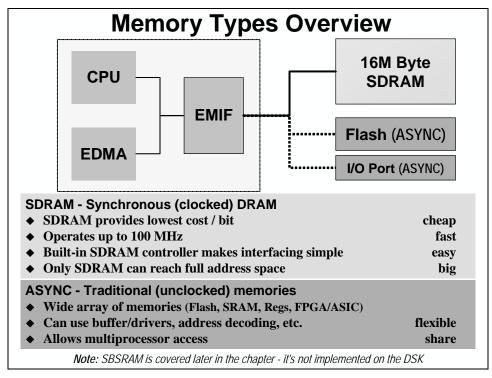

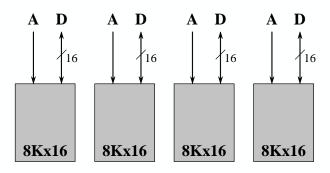

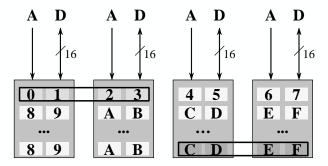

## **External Memory Interface (EMIF)**

EMIF is the interface between the CPU (or DMA/EDMA) and the external memory and provides all of the required pins and timing to access various types of memory.

- Glueless access to async or sync memory

- Works with PC100 SDRAM cheap, fast, and easy!

(more recent designs now allow use of PC133 SDRAM)

- Byte-wide data access

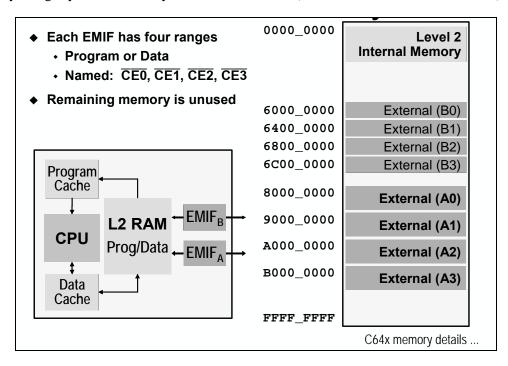

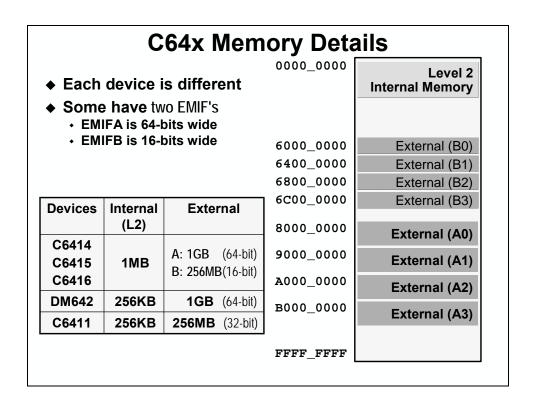

- C64x devices have two EMIFs (16-bit and 64-bit width)

- 16, 32, or 64-bit bus widths (please check the specifics for your device)

### **Ethernet**

- 10/100 Ethernet interface

- To conserve cost, size and power Ethernet pins are muxed with PCI (you can use one or the other)

- Optimized TCP/IP stack available from TI (under license)

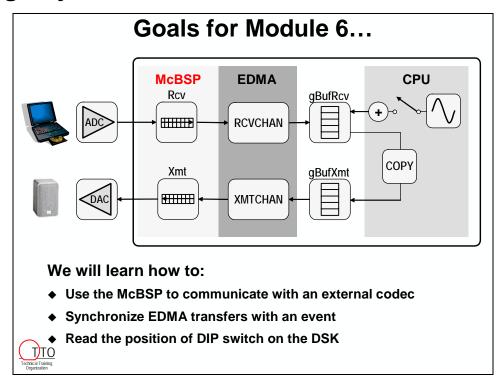

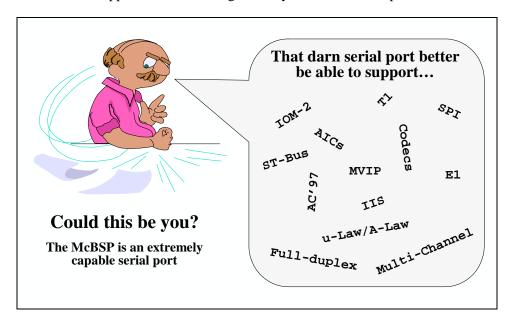

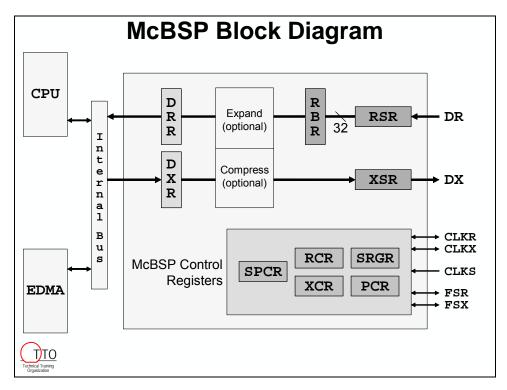

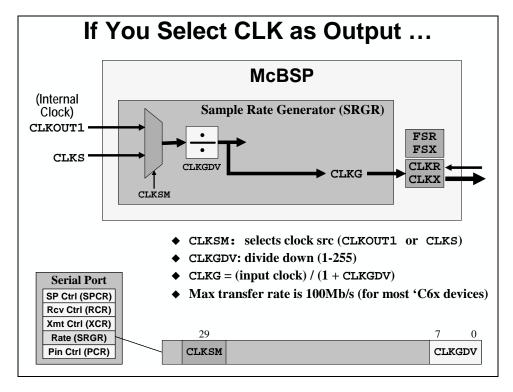

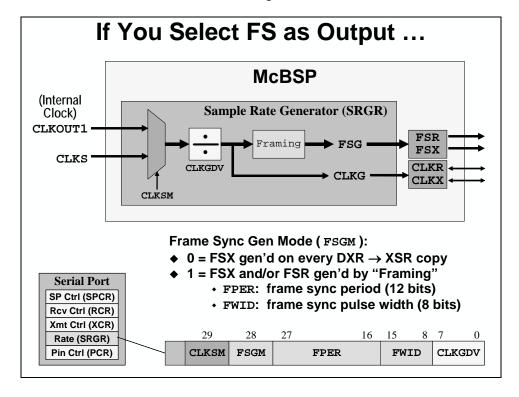

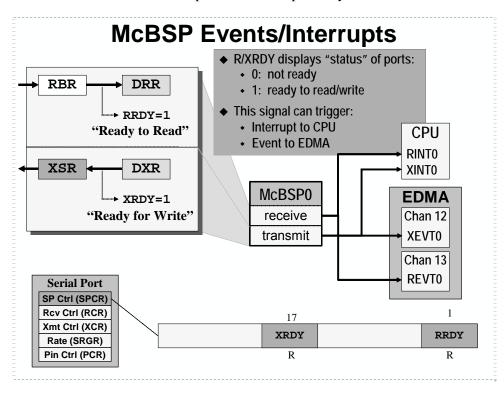

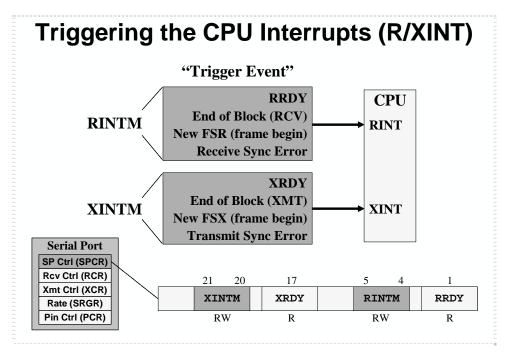

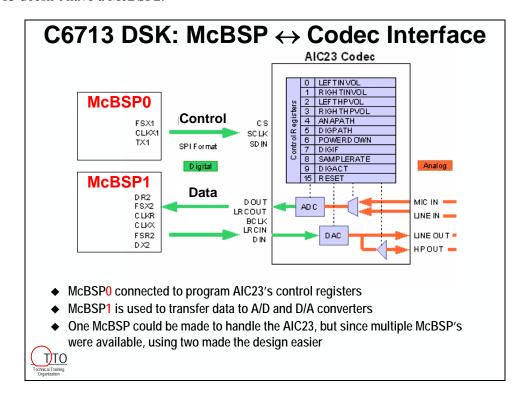

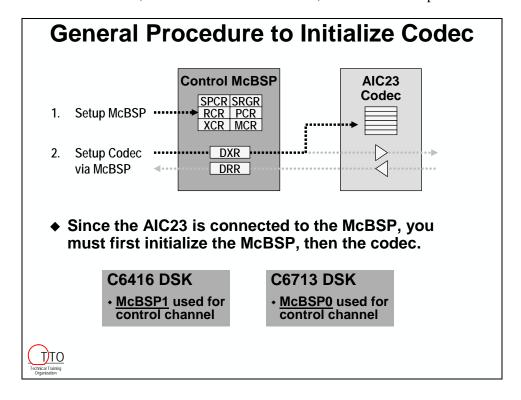

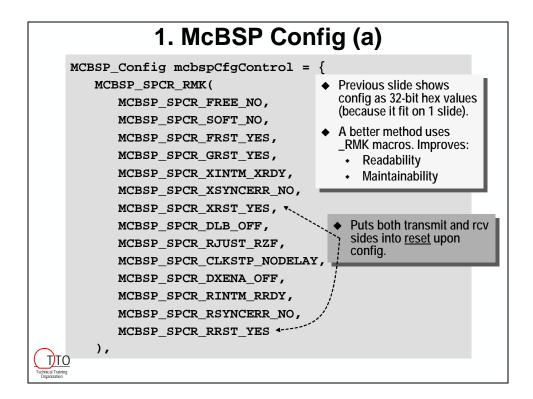

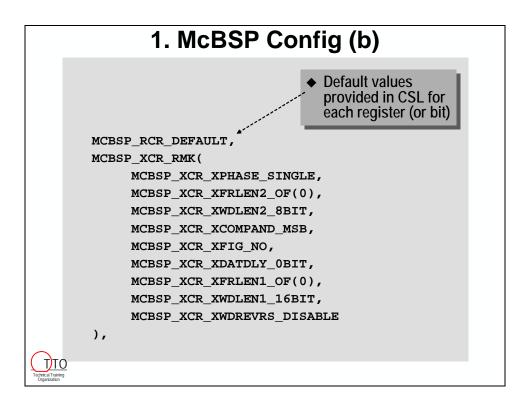

### Multi-Channel Buffered Serial Port (McBSP)

- Commonly used to connect to serial codecs (codec: combined A/D and D/A devices), but can be used for any type of synchronous serial communication

- Two (or three) synchronous serial-ports

- Full Duplex: Independent transmit and receive sections (each can be individually sync'd)

- High speed, up to 100 Mb/sec performance

- Supports:

- SPI mode

- AC97 codec interface standard

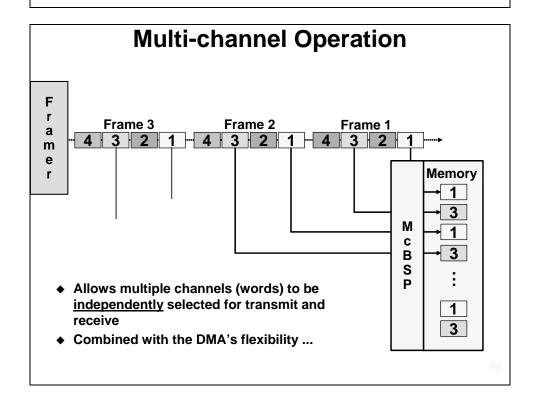

- Supports multi-channel operation (T1, E1, MVIP, ...)

- And many other modes

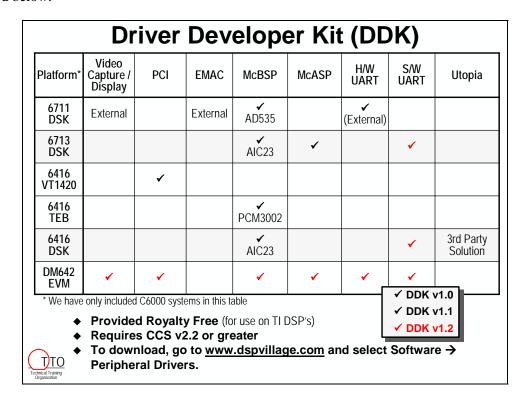

- Software UART available for most C6000 devices (Check the DSP/BIOS Drivers Developer Kit (DDK))

### **McASP**

- All McBSP features plus more ...

- Targeted for multi-channel audio applications such as surround sound systems

- Up to 8 stereo lines (16 channels) supported by 16 serial data pins configurable as transmit or receive

- Throughput: 192 kHz (all pins carrying stereo data simultaneously)

- Transmit formats:

- Multi-pin IIS for audio interface

- Multi-pin DIT for digital interfaces

- Receive format:

- Multi-pin IIS for audio interface

- Available on C6713 and DM642 devices.

### **Utopia**

- For connection to ATM (async transfer mode)

- Utopia 2 slave interface

- 50 MHz wide area network connectivity

- Byte wide interface

- Available on 'C64x devices

### **PLL**

- On-chip PLL provides clock multiplication. The 'C6000 family can run at one or more times the provided input clock. This reduces cost and electrical interference (EMI).

- Clock modes are pin configurable.

- On most devices, along with the *Clock Mode* (configuration) pins, there are three other clock pins:

- CLKIN: clock input pin

- CLKOUT: clock output from the PLL (multiplied rate)

- CLKOUT2: a reduced rate clockout. Usually ½ or less of CLKOUT

Please check the datasheet for the pins, pin names, and CKKOUT2 rates available for your device.

• Here are the PLL rates for a sample of C6000 device types:

| Device                           | Clock Mode Pins                  | PLL Rate                            |

|----------------------------------|----------------------------------|-------------------------------------|

| C6201<br>C6204<br>C6205<br>C6701 | CLKMODE                          | x1, x4                              |

| C6202<br>C6203                   | CLKMODE0<br>CLKMODE1<br>CLKMODE2 | x1, x4, x6, x7,<br>x8, x9, x10, x11 |

| C6211<br>C6711<br>C6712          | CLKMODE                          | x1, x4                              |

| C6414<br>C6415<br>C6416          | CLKMODE0<br>CLKMODE1             | x1, x6, x12                         |

### **Power Down**

• While not shown in the previous diagram, the 'C6000 supports power down modes to significantly reduce overall system power.

For more detailed information on these peripherals, refer to the 'C6000 Peripherals Guide.

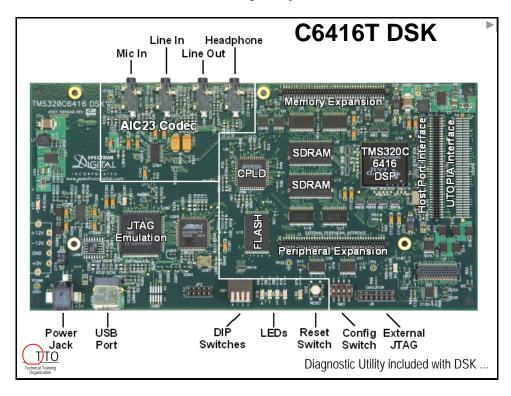

## C6000 DSK's

### Overview

Here's a detailed look at the DSK board and its primary features:

### **C6416 / C6713 DSK Features**

• TMS320C6416 DSP: 1GHz, fixed-point, 1M Byte internal RAM

or

TMS320C6713 DSP: 225MHz, floating-point, 256K Byte internal RAM

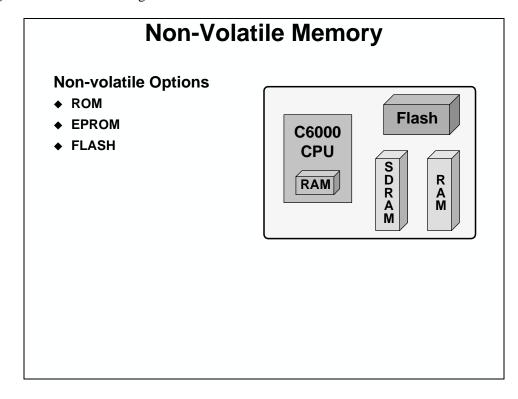

• External SDRAM: 16M Bytes,

C6416 – 64-bit interface C6713 – 32-bit interface 512K Bytes, 8-bit interface

• **External Flash:** 512K Bytes, 8-bit interface

• AIC23 Codec: Stereo, 8KHz –96KHz sample rate, 16 to 24-bit samples;

mic, line-in, line-out and speaker jacks

CPLD: Programmable "glue" logic

4 User LEDs: Writable through CPLD

4 User DIP Switches: Readable through CPLD

3 Configuration Switches: Selects power-on configuration and boot modes

Daughtercard Expansion I/F: Allows user to enhance functionality with add-on

daughtercards

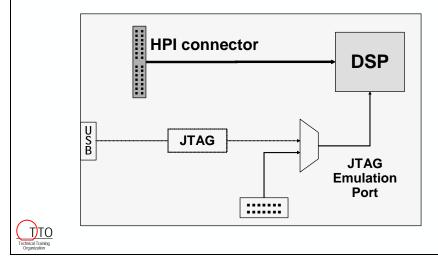

HPI Expansion Interface: Allows high speed communication with another DSP

Embedded JTAG Emulator: Provides high speed JTAG debug through widely

accepted USB host interface

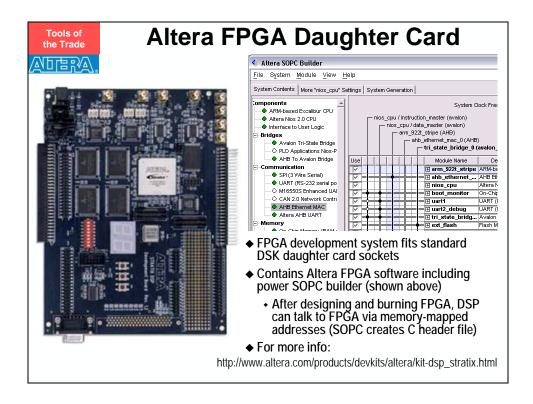

### Daughter-Card I/F

The daughter card sockets included on the DSK are similar to those found on other the C5000/C6000 DSKs and EVMs available from Texas Instruments. Thus, any work (by you or any 3<sup>rd</sup> Party) applied to daughter card development can be reused with the DSK. If you're interested in designing a daughter card for the DSK/EVM, check the TI website for an application note which describes it in detail.

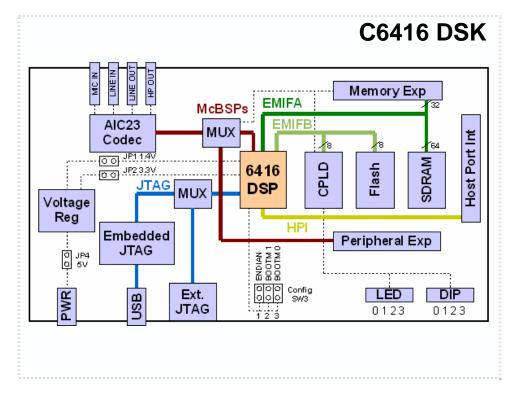

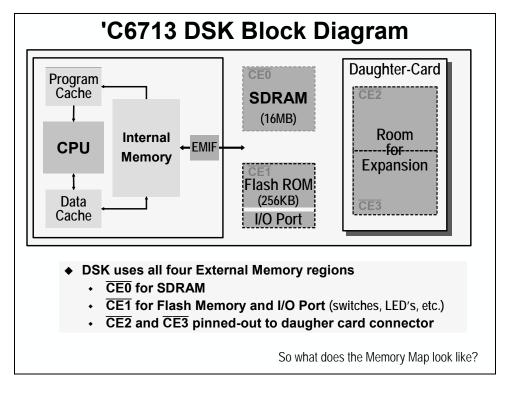

### **Block Diagram**

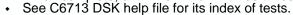

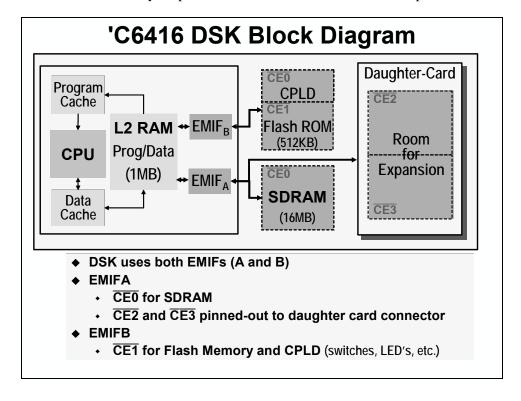

Here's a block diagram view of the C6416 DSK.

The C6713 would be almost exactly the same. (We pulled this diagram from the C6416 help file. Look in the C6713 help file <CCS Help menu> to find a similar diagram for that platform.)

# **DSK Diagnostic Utility**

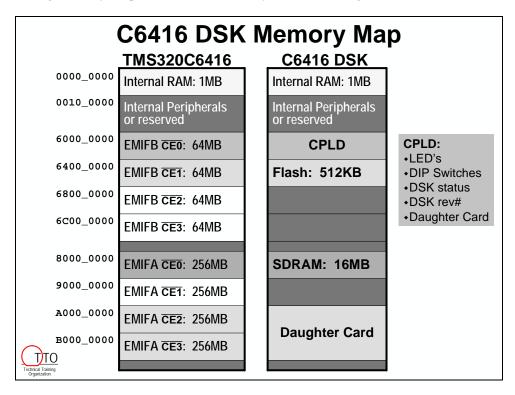

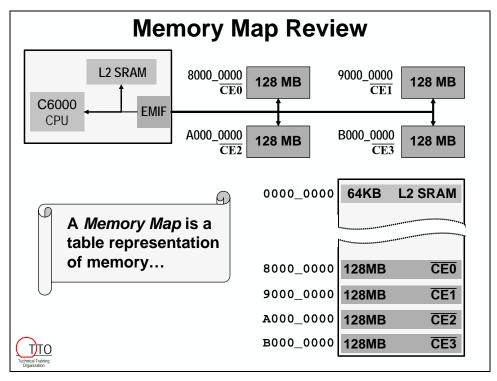

# **Memory Map**

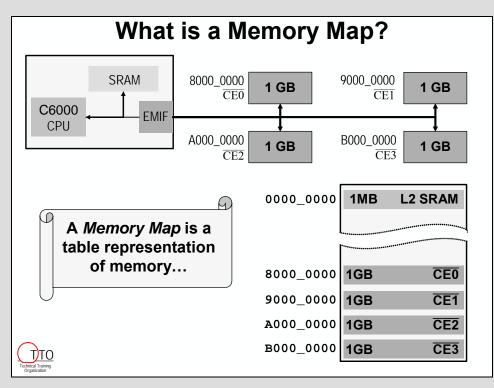

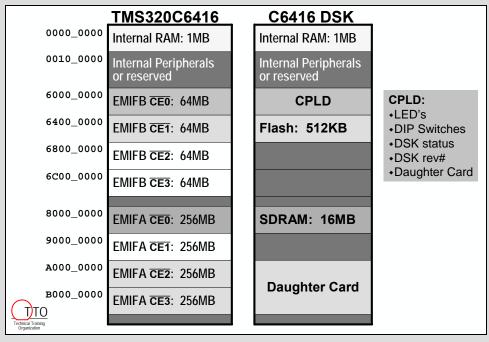

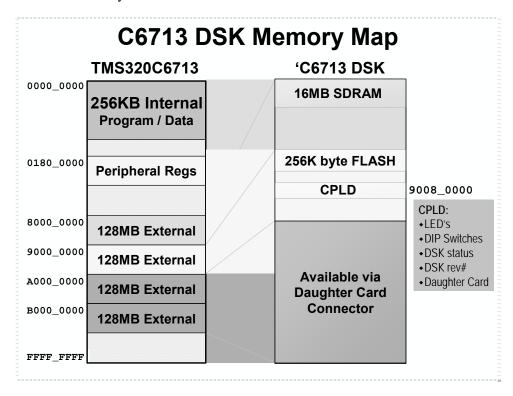

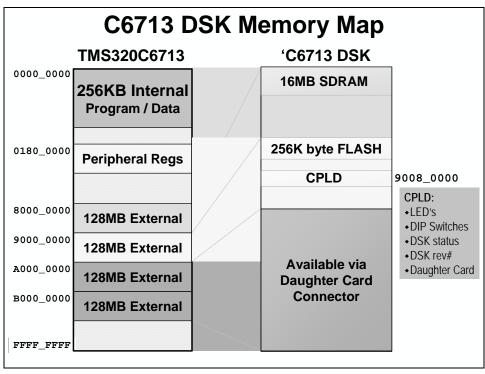

The following memory-map describes the memory resources designed into the 'C6416 DSK.

The left map describes the resources available on the 'C6416 DSP, the right map details how the external memory resources were used on the DSK.

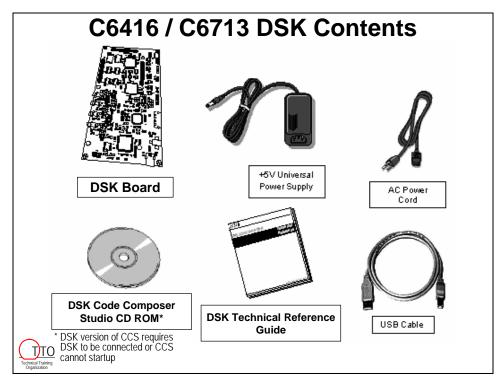

# In the DSK Package

# DSK Contents (i.e. what you get...)

### **Documentation**

- ◆ DSK Technical Reference

- ◆ eXpressDSP for Dummies

### Software

- ◆ Code Composer Studio

- ◆ SD Diagnostic Utility

- ◆ Example Programs

#### Hardware

- ◆ 1GHz C6416T DSP or 225 MHz C6713 DSP

- ◆ TI 24-bit A/D Converter (AIC23)

- ◆ External Memory

- 8 or 16MB SDRAM

- Flash ROM C6416 (512KB)

- C6713 (256KB)

### MISC Hardware

- ♦ LEDs and DIPs

- ◆ Daughter card expansion

- ♦ 1 or 2 additional expansions

- ◆ Power Supply & USB Cable

# **Lab 1 - Prepare Lab Workstation**

The computers used in TI's classrooms and dedicated workshops may be configured for one of ten different courses. The last class taught may have been DSP/BIOS, TMS320 Algorithm Standard, or a C5000 workshop. To provide a consistent starting point for all users, we need to have you complete a few steps to reset the CCS environment to a known starting point.

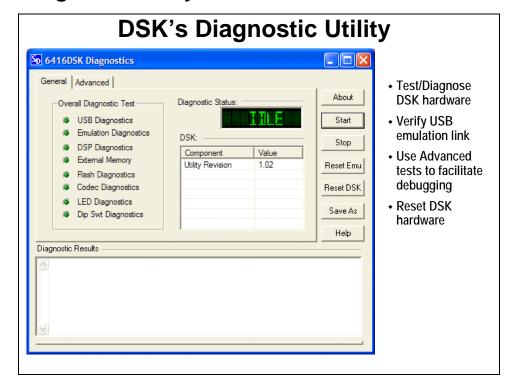

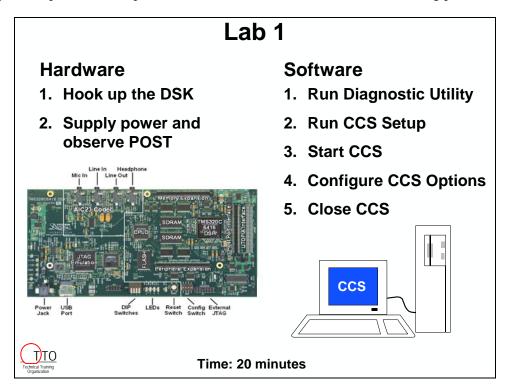

In Lab 1, we're going to prepare your lab workstations. This involves:

- Hooking up your DSK

- Running the DSK Diagnostic Utility to verify the USB connection and DSK are working

- Running CCS Setup to select the proper emulation driver (DSK vs. Simulator)

- Starting CCS and setting a few environment properties

## C64x or C67x Exercises?

We support two processor types in these workshop lab exercises. Please see the specific callouts for each processor as you work. Overall, there are very little differences between the procedures.

# Lab Exercises – C67x vs. C64x

- Which DSK are you using?

- ♦ We provide instructions and solutions for both C67x and C64x.

- ♦ We have tried to call out the few differences in lab steps as explicitly as possible:

## **Computer Login**

1. If the computer is not already logged-on, check to see if the log-on information is posted on the workstation. If not, please ask your instructor.

### Connecting the DSK to your PC

The software should have already been installed on your lab workstation. All you should have to do physically connect the DSK

2. Connect the supplied USB cable to your PC or laptop.

If you connect the USB cable to a USB Hub, be sure the hub is connected to the PC or laptop and power is applied to the hub.

**Note:** After plugging in the USB cable, if a message appears indicating that the USB driver needs to be installed, put the CCS CD from the DSK into the CD-ROM drive and allow the driver to be installed. In most classroom installations, this has already been completed for you.

- 3. Plug-in the appropriate audio connections.

- Connect your headphone or speaker to the audio output.

- An audio patch cable is provided to connect your computer's soundcard (or your music source) to the line-in connector on the DSK board.

**Note:** Make sure you insert the audio source and headphone plugs all the way into their respective sockets. Failing to do this may allow audio to short from the input to the output. While this may not hurt the board, it will prevent you from effectively evaluating your DSP code.

4. Plug the AC power cord into the power supply and AC source.

**Note:** Power cable must be plugged into AC source prior to plugging the 5 Volt DC output connector into the DSK.

- 5. Plug the power cable into the board. (note: when the POST runs in the next step and you have the earpiece in your ear, it will HURT!)

- 6. When power is applied to the board, the Power On Self Test (POST) will run. LEDs 0-3 will flash. When the POST is complete all LEDs blink on and off then stay on.

**Hint:** At this point, if you were installing the DSK for the first time on your own machine you would now finish the USB driver installation. We have already done this for you on our classroom PC's.

## **Testing Your Connection**

7. Test your USB connection to the DSK by launching the DSK Diagnostic Utility from the icon on the PC desktop.

From the diagnostic utility, press the start button to run the diagnostics. In approximately 20 seconds all the on-screen test indicators should turn green.

**Note:** If using the C6713 DSK, the title on this icon will differ accordingly.

If the utility fails while testing the DSK:

- Check to make sure the DSK is receiving power.

- Also, verify the USB cable is plugged into both the DSK and the PC.

- After ruling out cabling, a failure is most often caused by an incomplete USB driver installation. Deleting and reinstalling the driver often solves this problem. (Again, you should rarely see this problem.)

## **CCS Setup**

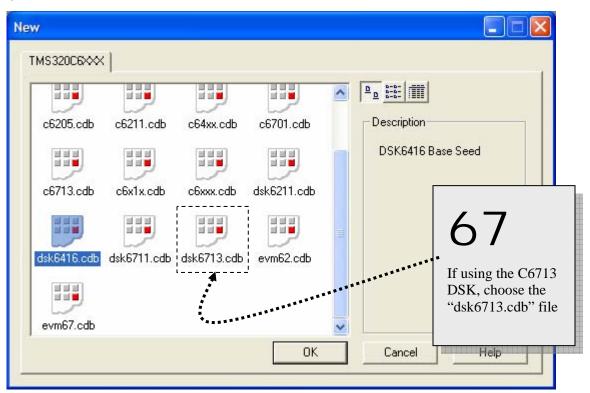

While Code Composer Studio (CCS) has been installed, you will need to assure it is setup properly. CCS can be used with various TI processors – such as the C6000 and C5000 families – and each of these has various target-boards (simulators, EVMs, DSKs, and XDS emulators). Code Composer Studio must be properly configured using the CCS\_Setup application.

In this workshop, you should initially configure CCS to use either the *C6713 DSK* or the *C6416 V1.1 DSK*. Between you and your lab partner, choose one of the DSK's and the appropriate driver. In any case, the learning objectives will be the same whichever target you choose.

8. Start the CCS Setup utility using its desktop icon:

Be aware there are two CCS icons, one for setup, and the other to start the CCS application. You want the **Setup CCS** C6000 icon.

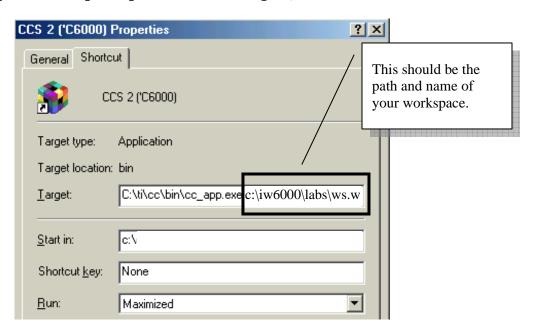

#### Sidebar: CCS Setup

The version of CCS that ships with the DSK will not place the *Setup CCS 2* icon on the desktop, nor will the shortcut appear under the Windows start menu:

$Start \rightarrow Programs \rightarrow Texas\ Instruments \rightarrow Code\ Composer\ Studio\ 2\ (`C6000) \rightarrow Setup\ Code\ Composer\ Studio\ 2\ (`C6000) \rightarrow Setup\ Code\ Composer\ Studio\ Code\ Composer\ Studio\ Code\ Composer\ Studio\ Code\ Code\$

The setup program <cc\_setup.exe> is installed to the hard drive for both the full and DSK versions of CCS, although the desktop icon and Start menu shortcut are only added when installing the full version of CCS.

For your convenience, during installation of the workshop labs and solutions an icon for CCS Setup was placed on the desktop. If, for some unexpected reason, this icon has been deleted, you can find and run the program from:

c:\ti\cc\bin\cc\_setup.exe

(where "\ti\" is the directory you installed CCS)

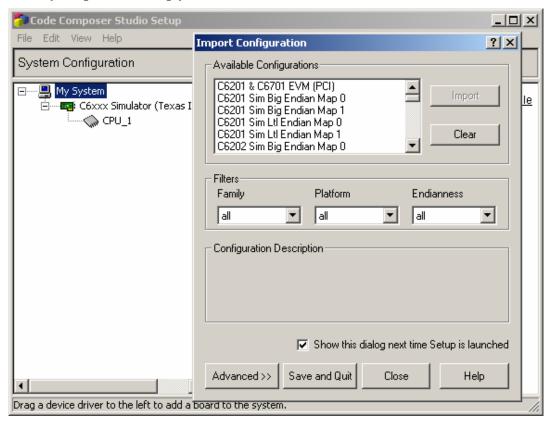

### 9. When you open CC\_Setup you should see a screen similar to this:

**Note:** If you don't see the *Import Configuration* dialog box, you should open it from the menu using **File** → **Import...**

Once the *Import Configuration* dialog box is open, you can change the CC\_Setup default to force this dialog to open every

time you start CC\_Setup. Just check the box in the bottom of the import dialog.

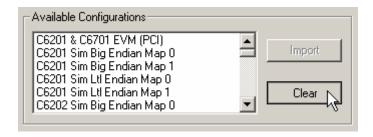

10. Clear the previous configuration.

Before you select a new configuration you should delete the previous configuration. Click the Clear System Configuration button. CC\_Setup will ask if you really want to do this, choose "Yes" to clear the configuration.

11. Select a new configuration from the list and click the "Import" button.

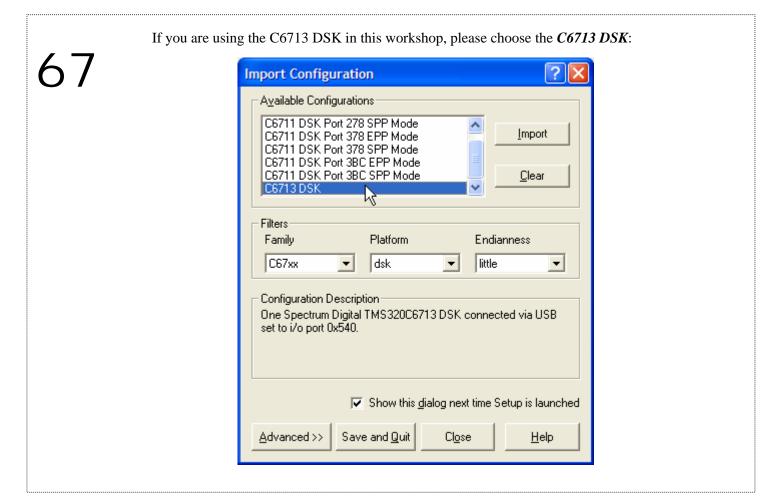

If you are using the C6416 DSK in this workshop, please choose the C6416 V1.1 DSK:

- 12. Save and Quit the *Import Configuration* dialog box.

- 13. Go ahead and start CCS upon exiting CCS Setup.

### **Set up CCS – Customize Options**

There are a few option settings that need to be verified before we begin. Otherwise, the lab procedure may be difficult to follow.

- Disable open Disassembly Window upon load

- Go to main() after load

- Program load after build

- Clear breakpoints when loading a new program

- Set CCS Titlebar information

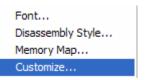

### 14. Use the Customize Dialog box to set specific options.

Select:

Option → Customize...

Uncheck the box for *Open the Diasassembly Window automatically*. Check the *Perform Go Main automatically* box. Check the following check box: *Connect to the target when a control window is open*.

Here are a couple options that can help make debugging easier.

Unless you want the Window popping up every program (which annoys deselect this option.

Disassembly time you load a many folks),

Many find it convenient to choose the "Perform Go Main automatically". Whenever

a program is loaded the debugger will automatically run thru the compilers

initialization code to your main() function.

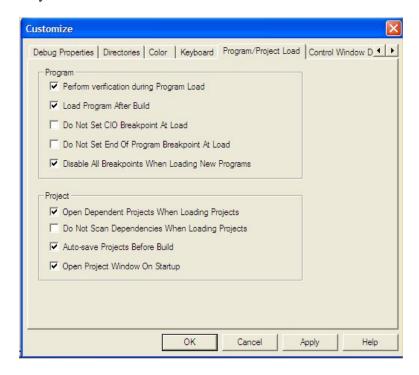

#### 15. Set Program Load Options

On the "Program/Project Load" tab, make sure the options shown below are checked:

- Load Program After Build

- Clear All Breakpoints When Loading New Programs

By default, these options are not enabled, though a previous user of your computer may have already enabled them.

Conceptually, the CCS Integrated Development Environment (IDE) is made up of two parts:

- *Edit* (and Build) programs (uses editor and code gen tools to create code).

- *Debug* (and Load) programs (communicates with DSP/simulator to download/run code.

The *Load Program After Build* option automatically loads the program (.out file) created when you build a project. If you disabled this automatic feature, you would have to manually load the program via the File—Load Program menu.

**Note:** You might even think of IDE as standing for Integrated Debugger Editor, since those are the two basic modes of the tool

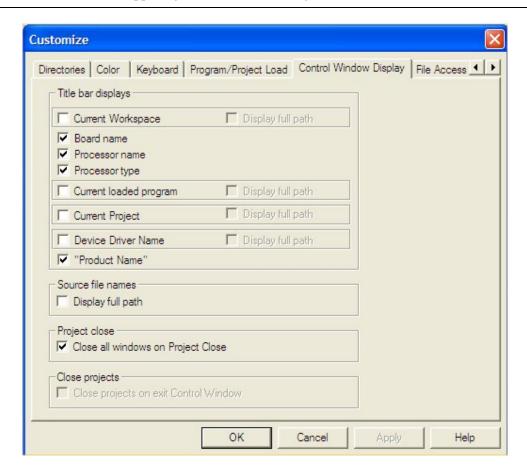

#### 16. CCS Title Bar Properties

CCS allows you to choose what information you want displayed on its title bar.

**Note:** To reach this tab of the "Customize" dialog box, you may have to scroll to the right using the arrows in the upper right corner of the dialog.

Make sure that the options shown above are checked.

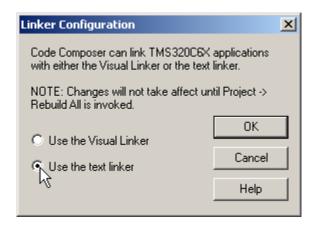

### **Choose Text-Based Linker**

CCS includes two different linkers. The Visual Linker is now obsolete – therefore we want to make sure it is not selected. Do NOT use or experiment with the Visual Linker.

17. Open the CCS linker selection dialog.

$Tools \rightarrow Linker Configuration$

**18.** Select *Use the text linker* and click OK (as shown below).

19. Quit Code Composer Studio.

You're Done

\*\*\* can you explain why you're reading a blank page? \*\*\*

# **Appendix (For Reference Only)**

## **Power On Self-Test stages**

The following table details the various states of the POST routine and how you can visually track its progress.

# **C6416 DSK - Power On Self Test (POST)**

| Test | LED4 | LED 3 | LED 2 | LED 1        | <u>Description</u>                     |

|------|------|-------|-------|--------------|----------------------------------------|

| 1    | 0    | 0     | 0     | 1            | DSP's Internal Memory test             |

| 2    | 0    | 0     | 1     | 0            | External SDRAM test                    |

| 3    | 0    | 0     | 1     | 1            | Check manufacture ID of Flash chip     |

| 4    | 0    | 1     | 0     | 0            | McBSP 0 loopback test                  |

| 5    | 0    | 1     | 0     | 1            | McBSP 1 loopback test                  |

| 6    | 0    | 1     | 1     | 0            | McBSP 2 loopback test                  |

| 7    | 0    | 1     | 1     | 1            | Transfer small array with EDMA         |

| 8    | 1    | 0     | 0     | 0            | Codec test (output 1KHz tone)          |

| 9    | 1    | 0     | 0     | 1            | Timer test (cfg and wait for 100 ints) |

|      | BLIN | K ALL |       | All tests of | completed successfully                 |

- Stored in FLASH memory and runs every time DSK is powered on Source code on DSK CD-ROM

- When test is performed, index number is shown on LED's. If test fails, the index of that test will blink continuously.

more than 15-30 seconds, then there might be a problem.)

Don't worry if it takes a few seconds to perform Test 2 (External SDRAM test). It can take a while to test all the SDRAM memory included on the DSK. (Of course, if it takes

# **DSK Help**

This file describes the board design, its schematics, and how the DSK utilities work.

# **Using Code Composer Studio**

### Introduction

The importance of the C language in DSP systems has grown significantly over the past few years. TI has responded by creating an efficient silicon and compiler architecture to provide efficient C performance. Additionally, TI has worked hard to provide easy-to-use software development tools.

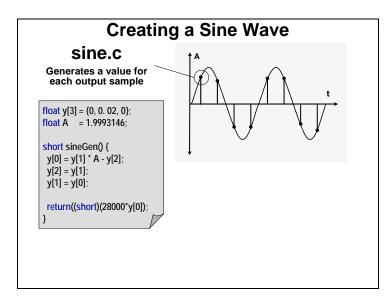

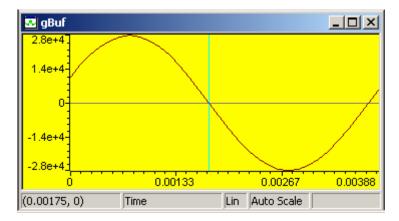

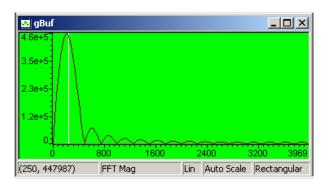

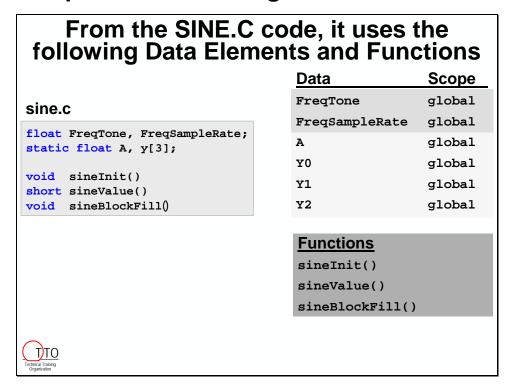

Using these tools, all it takes is a couple of minutes to get your C code running on the 'C6000. That's the goal of this module: compile, debug, and graph a simple C sine-wave routine.

# **Learning Objectives**

## **Outline**

- ◆ Code Composer Studio (CCS)

- Projects

- **♦ Build Options**

- **♦ Build Configurations**

- **◆** Configuration Tool

- ◆ C Data Types and Header Files

- ♦ Lab 2

# **Module Topics**

| Using Code Composer Studio                | 2-1  |

|-------------------------------------------|------|

| Code Composer Studio (CCS)                | 2-3  |

| Projects                                  | 2-6  |

| Build Options                             | 2-8  |

| CCS Graphical Interface for Build Options |      |

| Linker Build Options                      |      |

| Configuration Tool                        |      |

| C – Data Types and Header Files           | 2-13 |

| C Data Types                              | 2-13 |

| C Header (.h) Files.                      | 2-14 |

| LAB 2: Using Code Composer Studio         | 2-15 |

| main.c                                    | 2-17 |

| sine.h                                    | 2-18 |

| sine.c                                    | 2-19 |

| sine.c (continued)                        | 2-20 |

| sine.c (continued)                        | 2-21 |

| Start CCS                                 | 2-22 |

| Create the Lab2 project                   | 2-22 |

| Create a CDB file                         | 2-23 |

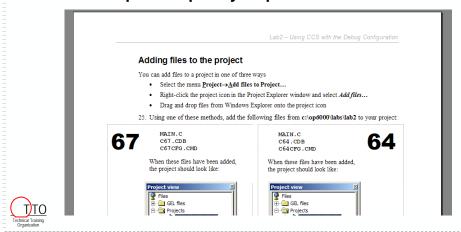

| Adding files to the project               | 2-24 |

| Examine the C Code                        |      |

| Examine/Modify the Build Options          | 2-25 |

| Building the program (.OUT)               | 2-26 |

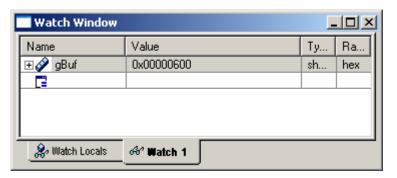

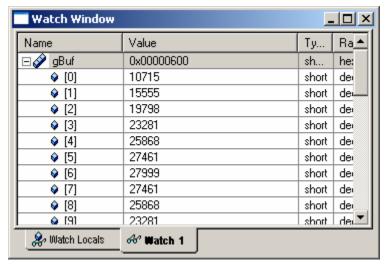

| Watch Variables                           | 2-27 |

| Viewing and Filling Memory                | 2-27 |

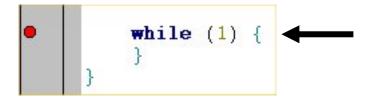

| Setting Breakpoints                       | 2-28 |

| Running Code                              | 2-29 |

| Windows and Workspaces                    | 2-30 |

| Graphing Data                             | 2-31 |

| Shut Down and Close                       | 2-32 |

| Optional Exercises                        | 2-33 |

| Lab2a – Customize CCS                     | 2-33 |

| Lab2b – Using GEL Scripts                 | 2-35 |

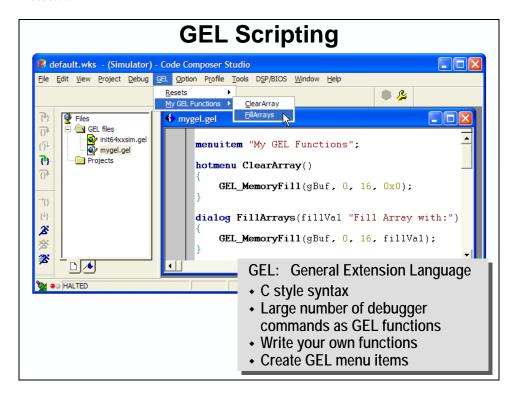

| Using GEL Scripts                         | 2-35 |

| Lab2c – Fixed vs Floating Point           | 2-38 |

| Optional Topics                           | 2-40 |

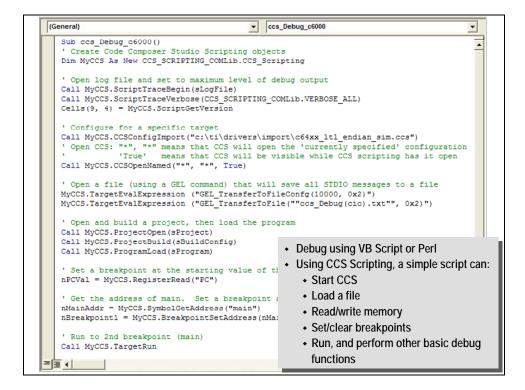

| Optional Topic: CCS Automation            |      |

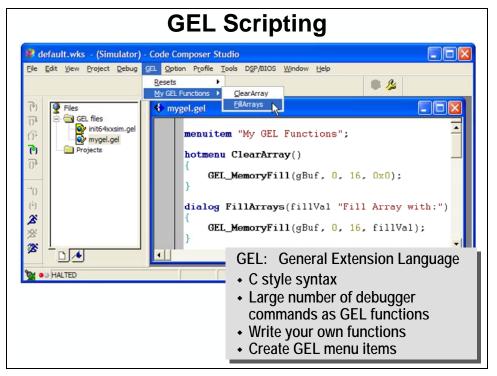

| GEL Scripting                             | 2-40 |

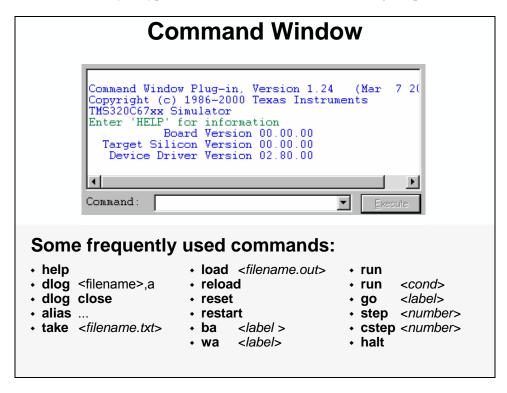

| Command Line Window                       | 2-41 |

| CCS Scripting                             |      |

| TCONF Scripting (Textual Configuration)   |      |

# **Code Composer Studio (CCS)**

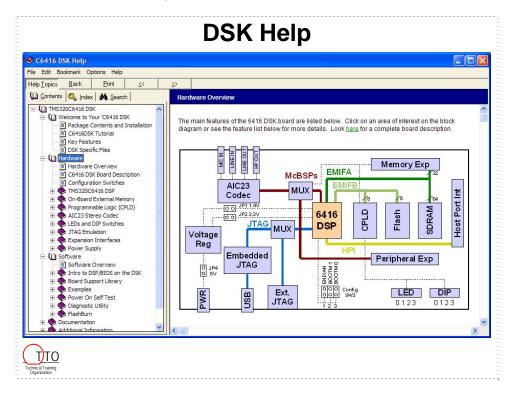

The Code Composer Studio (CCS) application provides all the necessary software tools for DSP development. At the heart of CCS you'll find the original Code Composer IDE (integrated development environment). The IDE provides a single application window in which you can perform all your code development; from entering and editing your program code, to compilation and building an executable file, and finally, to debugging your program code.

When TI developed Code Composer Studio, it added a number of capabilities to the environment. First of all, the code generation tools (compiler, assembler, and linker) were added so that you wouldn't have to purchase them separately. Secondly, the simulator was included (only in the full version of CCS, though). Third, TI has included DSP/BIOS. DSP/BIOS is a real-time kernel consisting of three main features: a real-time, pre-emptive scheduler; real-time capture and analysis; and finally, real-time I/O.

Finally, CCS has been built around an extensible software architecture which allows third-parties to build new functionality via *plug-ins*. See the TI website for a listing of 3<sup>rd</sup> parties already developing for CCS.

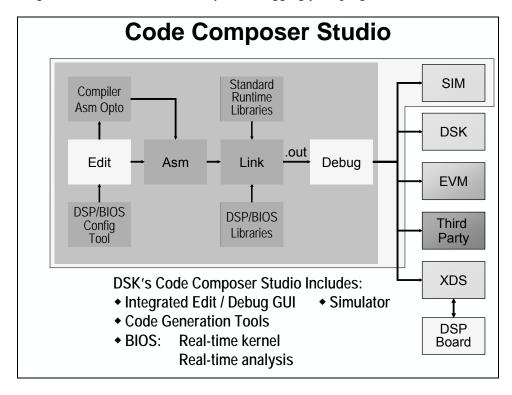

Here's a snapshot of the CCS screen:

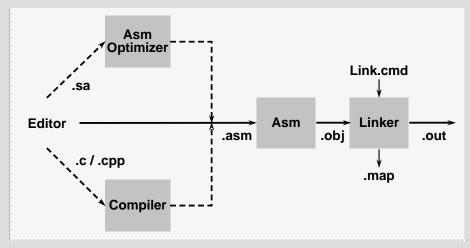

### A Short Review of CCS File Extensions

Using Code Composer Studio (CCS) you may not need to know all these file extension names, but we included a basic review of them for your reference:

- C and C++ use the standard .C and .CPP file extensions.

- Linear Assembly is written in a .SA file.

- You can either write standard assembly directly, or it can be created by the compiler and Assembly Optimizer. In all cases, standard assembly uses .ASM.

- Object files (.OBJ), created by the assembler, are linked together to create the DSP's executable output (.OUT) file. The map (.MAP) file is an output report of the linker.

- The .OUT file can be loaded into your system by the debugger portion of CCS.

If you want to use your own extensions for file names, they can be redefined with code generation tool options. Please refer to the *TMS320C6000 Assembly Tools Users Guide* for the appropriate options.

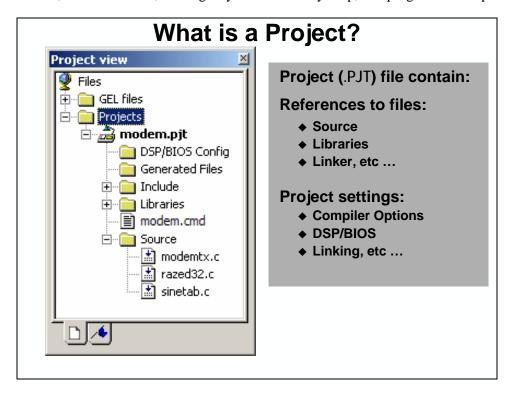

# **Projects**

Code Composer works with a *project* paradigm. If you've done code development with most any sophisticated IDE (Microsoft, Borland, etc.), you've no doubt run across the concept of projects.

Essentially, within CCS you create a project for each executable program you wish to create. Projects store all the information required to build the executable. For example, it lists things like: the source files, the header files, the target system's memory-map, and program build options.

The project information is stored in a .PJT file, which is created and maintained by CCS. To create a new project, you need to select the **Project:New**... menu item.

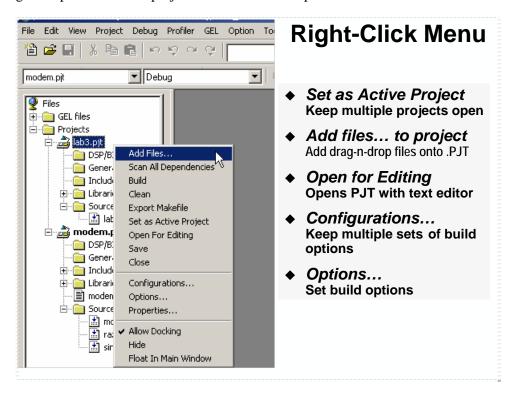

Along with the main **Project** menu, you can also manage open projects using the right-click popup menu. Either of these menus allows you to **Add Files...** to a project. Of course, you can also drag-n-drop files onto the project from Windows Explorer.

There are many other project management options. In the preceding graphic we've listed a few of the most commonly used actions:

- If your project team builds code outside the CCS environment, you may find Export Makefile (and/or Source Control) useful.

- CCS now allows you to keep multiple projects open simultaneously. Use the **Set as Active Project** menu option or the project drop-down to choose which one is active.

- If you like digging below the surface, you'll find that the .PJT file is simply an ASCII text file. **Open for Editing** opens this file within the CCS text editor.

- Configurations... and Options... are covered in detail, next.

## **Build Options**

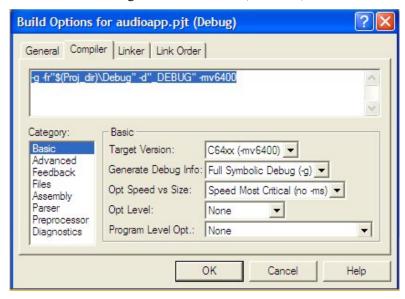

Project options direct the code generation tools (i.e. compiler, assembler, linker) to create code according to your system's needs. Do you need to logically debug your system, improve performance, and/or minimize code size? Your C6000 results can be dramatically affected by compiler options.

# **Compiler Build Options**

- ♦ Nearly one-hundred compiler options available to tune your code's performance, size, etc.

- ◆ Following table lists most commonly used options:

|           | Options         | Description                                  |

|-----------|-----------------|----------------------------------------------|

|           | -mv6700         | Generate 'C67x code ('C62x is default)       |

|           | -mv67p          | Generate 'C672x code                         |

|           | -mv6400         | Generate 'C64x code                          |

|           | -mv6400+        | Generate 'C64x+ code                         |

|           | -fr <dir></dir> | Directory for object/output files            |

|           | -fs <dir></dir> | Directory for assembly files                 |

| Debug     | -g              | Enables src-level symbolic debugging         |

| Debug     | -SS             | Interlist C statements into assembly listing |

| Optimize  | -03             | Invoke optimizer (-o0, -o1, -o2/-o, -o3)     |

| (release) | -k              | Keep asm files, but don't interlist          |

<u>Debug</u> and <u>Optimize</u> options conflict with each other, therefore they should be not be used together

There are probably about a 100 options available for the compiler alone. Usually, this is a bit intimidating to wade through. To that end, we've provided a condensed set of options. These few options cover about 80% of most users needs.

As you probably learned in college programming courses, you should probably follow a two-step process when creating code:

- Write your code and debug its logical correctness (without optimization).

- Next, optimize your code and verify it still performs as expected.

As demonstrated above, certain options are ideal for debugging, but others work best to create highly optimized code. When you create a new project, CCS creates two sets of build options – called *Configurations*: one called *Debug*, the other *Release* (you might think of as Optimize). Configurations will be explored in the next section.

**Note:** As with any compiler or toolset, learning the various options requires a bit of experimentation, but it pays off in the tremendous performance gains that can be achieved by the compiler.

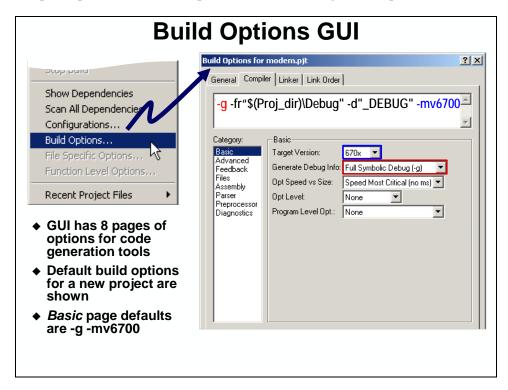

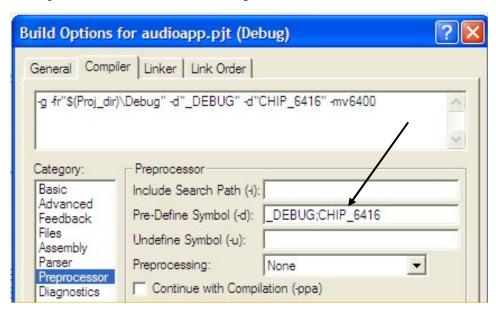

## **CCS Graphical Interface for Build Options**

To make it easier to choose build options, CCS provides a graphical user interface (GUI) for the various compiler options. Here's a sample of the *Debug* configuration options.

There is a one-to-one relationship between the items in the text box and the GUI check and drop-down box selections. Once you have mastered the various options, you'll probably find yourself just typing in the options.

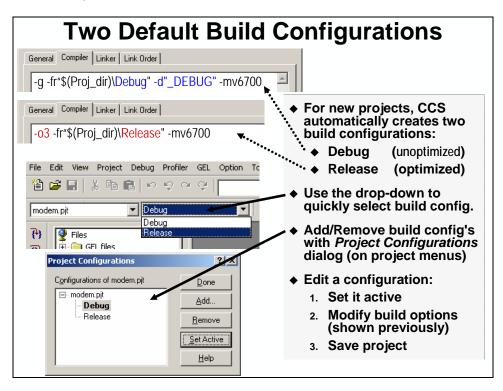

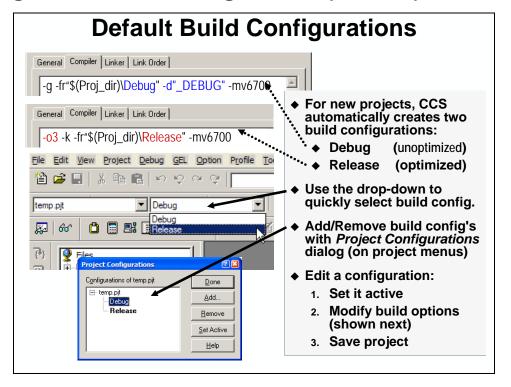

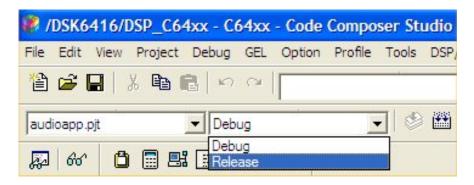

## **Build Option Configurations (Sets of Build Options)**

To help make sense of the many compiler and linker options, you can create sets of build options. These sets of options are called *configurations*. TI provides two default configurations in each new project you create. For example, if you created a project called *modem.pjt*, it would contain:

| Debug   | -g -fr"\$(Proj_dir)\Debug" -d"_DEBUG" -mv6700 |

|---------|-----------------------------------------------|

| Release | -o3 -fr"\$(Proj_dir)\Release" -mv6700         |

The two main differences between the *Debug* and *Release* configurations:

- Debug uses the –g option to enable source-level debugging

- **Release** invokes the optimizer with -o3 (and doesn't use -g)

**Note:** \$(**Proj\_dir**) indicates the current project directory. This aids in project portability. See SPRA913 (*Portable CCS Projects*) for more information.

The following graphic summarizes the default configurations for a project called "modem". Additionally, it shows how to:

- Select the configuration before building your project

- Add or Remove configurations from a project (*Project* → *Configurations*... menu)

Steps to edit a configuration

**Note:** The examples shown here are for a C67x DSP, hence the –mv6700 option.

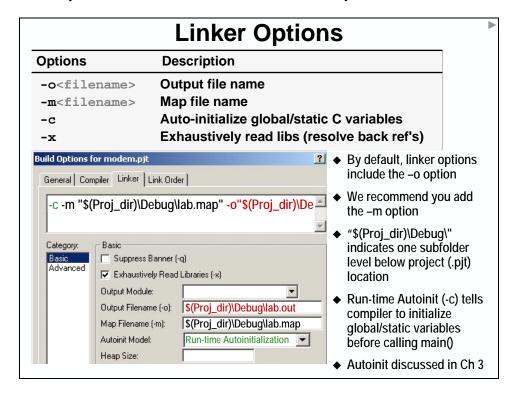

## **Linker Build Options**

There are many linker options but these four handle all of the basic needs.

- -o <filename> specifies the output (executable) filename.

- -m <filename> creates a map file. This file reports the linker's results.

- -c tells the compiler to autoinitialize your global and static variables.

- -x tells the compiler to exhaustively read the libraries. Without this option libraries are searched only once, and therefore backwards references may not be resolved.

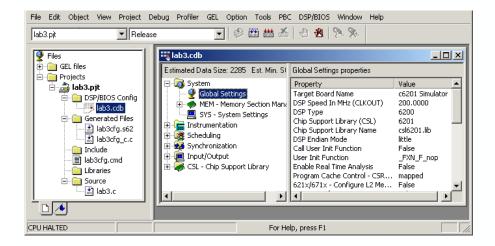

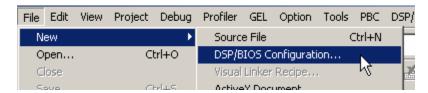

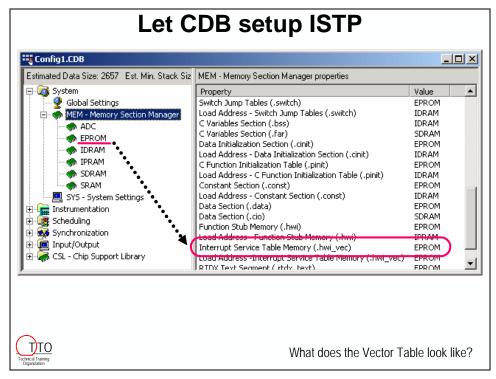

## **Configuration Tool**

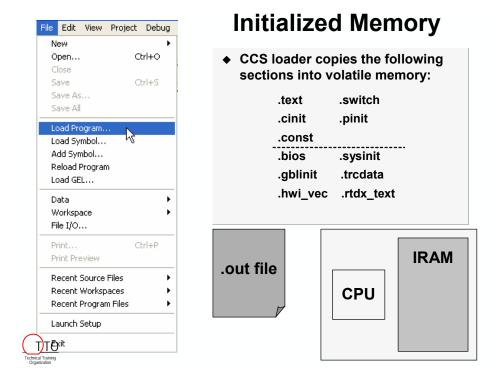

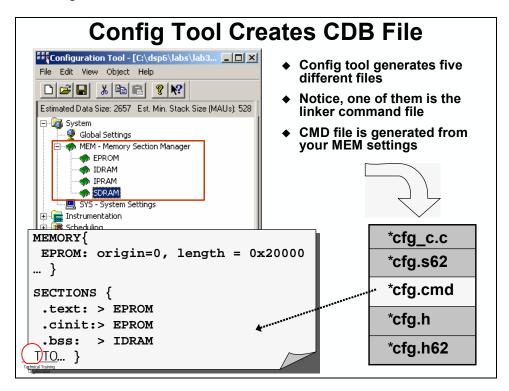

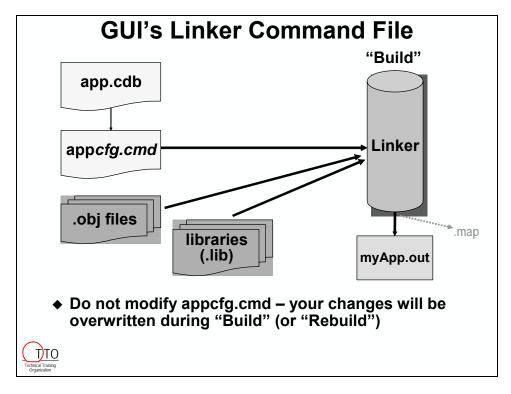

The DSP/BIOS Configuration Tool (often called Config Tool or GUI Tool or GUI) creates and modifies a system file called the Configuration DataBase (.CDB). If we talk about using CDB files, we're also talking about using the Config Tool.

The following figure shows a CDB file opened within the configuration tool:

The GUI (graphical user interface) simplifies system design by:

- Automatically including the appropriate runtime support libraries

- Automatically handles interrupt vectors and system reset

- Handles system memory configuration (builds CMD file)

- When a CDB file is saved, the Config Tool generates 5 additional files:

| Filename.cdb            | Configuration Database          |

|-------------------------|---------------------------------|

| Filename <b>cfg_c.c</b> | C code created by Config Tool   |

| Filenamecfg.s62         | ASM code created by Config Tool |

| Filename <b>cfg.cmd</b> | Linker commands                 |

| Filename <b>cfg.h</b>   | header file for *cfg_c.c        |

| Filenamecfg.h62         | header file for *cfg.s62        |

When you add a CDB file to your project, CCS automatically adds the C and assembly (.S62) files to the project under the *Generated Files* folder. (You must manually add the CMD file, yourself.)

• Many of the CDB objects will be discussed in this workshop. To get all the details on this tool, though, we recommend you attend the 4-day *DSP/BIOS Workshop*.

# C - Data Types and Header Files

## C Data Types

| Type        | Bits | Representation         |

|-------------|------|------------------------|

| char        | 8    | ASCII                  |

| short       | 16   | Binary, 2's complement |

| int         | 32   | Binary, 2's complement |

| long        | 40   | Binary, 2's complement |

| long long   | 64   | Binary, 2's complement |

| float       | 32   | IEEE 32-bit            |

| double      | 64   | IEEE 64-bit            |

| long double | 64   | IEEE 64-bit            |

| pointers    | 32   | Binary                 |

Here are a few guidelines to keep in mind regarding C data types on the C6000:

- 1. Use *short* types for integer multiplication. As with most fixed-point DSPs, our 'C62x devices use a 16x16 integer multiplier. If you specify an *int* multiply, a software function in the runtime support library will be called. (Note, the 'C67x devices do have a 32x32→64-bit multiply instruction, MPYID.)

- 2. Use *int* types for counters and indexes. As we examine during the next chapter, all registers and data paths are 32-bits wide.

- 3. Avoid accidentally mixing *long* and *int* variables. Many compilers allocate 32-bits for both types, thus some users interchange these types. The 'C6000 allocates *longs* at 40-bits to take advantage of 40-bit hardware within the CPU. If you mix types, the compiler may be forced to manage this which will most likely cost you some performance.

- Why 40-bits? The extra 8-bits are often used to provide headroom in integer operations. Also, they can act like an 8-bit "carry bit".

- 4. On 'C67x devices, 32-bit *float* operations are performed in hardware. The 'C6000 supports IEEE 32-bit floating-point math.

- 5. The *double* precision floating-point hardware supports IEEE 64-bit floating-point math.

- 6. Pointers, at 32-bits, can reach across the entire 'C6000 memory-map.

## C Header (.h) Files

# **Including Header Files in C**

```

/*

* ======= Include files =======

*/

#include <csl.h>

#include <csl_edma.h>

#include "sine.h"

#include "edma.h"

```

- 1. What is #include used for?

- 2. What do header (.h) files contain?

- 3. What is the difference between <.h> and ".h"?

# **Example Header Files**

```

===== sine.h ======

This file contains prototypes for all

functions and global datatypes

contained in sine.c

#ifndef SINE_Obj

typedef struct {

float freqTone;

float fregSampRate;

float a;

float b;

float y0;

float y1;

float y2;

} SINE_Obj;

#endif

void copyData(short *inbuf, ...);

void SINE_init(SINE_Obj *sineObj, ...);

```

```

/*

* ======= edma.h ======

* This file contains references for all

* functions contained in edma.c

*/

void initEdma(void);

void edmaHwi(int tcc);

extern EDMA_Handle hEdma;

```

- Header files can contain any C code to be used over and over again

- Usually a header file is paired with a C file or library object file. Essentially, the header file provides a description of the global items in the "paired" file.

- ◆ Most commonly, header files contain:

- Function prototypes

- Global data references, such as new type definitions

- 1. What is #include used for?

- It adds the contents of the header file to your C file at the point of the #include statement.

- 2. What do header (.h) files contain?

- They can contain any C statements. Usually, they contain code that would otherwise need to be entered into every C file. They're a shortcut.

- 3. What is the difference between <.h> and ".h"?

- Angle brackets <.h> tell the compiler to look in the specified include path.

- Quotes ".h" indicate the file is located in the same location as the file which includes it.

# **LAB 2: Using Code Composer Studio**

This lab has four goals:

- Build a project using C source files.

- Load a program onto the DSK.

- Run the program and view the results.

- Use the CCS graphing feature to verify the results.

### Lab 2 - Creating/Graphing a Sine Wave

#### Introduction to Code Composer Studio (CCS)

- ◆ Create and build a project

- ♦ Examine variables, memory, code

- ♦ Run, halt, step, breakpoint your program

- ◆ Graph results in memory (to see the sine wave)

**Note:** You will find that in this lab, the code is working VERY inefficiently. Using the proper optimization techniques (later in the workshop), you will experience vast improvements in the code's performance.

A block sine-wave generator function creates data samples which we can then graph. The block sine-wave generator function is a basic *for* loop that uses the following routine to generate individual sine values:

The algorithm used in the workshop is similar to that shown above. It uses a monostable IIR filter to generate a sine wave.

The lab's version of the sine-wave generator, though, provides an sine initialization function which calculates the value for A and y[1] based on the tone & sampling frequencies.

There are many ways to create sine values, we have chosen this simple IIR based model. While generating a sine wave using a table is probably more MIPs efficient, this method is more memory efficient. Also, since this function calculates each sine wave value, it gives the processor some "work" to perform.

### main.c

For your convenience, we've provided a print out of the code that you will be starting with on the next few pages.

```

====== main.c ======

* This file contains all the functions for Lab2 except

SINE_init() and SINE_blockFill().

====== Include files ======

#include "sine.h"

====== Declarations ======

#define BUFFSIZE 32

====== Prototypes ======

====== Global Variables ======

short gBuf[BUFFSIZE];

SINE_Obj sineObj;

====== main ======

void main()

SINE_init(&sineObj, 256, 8 * 1024);

SINE_blockFill(&sineObj, gBuf, BUFFSIZE); // Fill the buffer

with sine data

while (1) {

// Loop Forever

```

#### sine.h

```

====== sine.h ======

This file contains prototypes for all functions

contained in sine.c

#ifndef SINE_Obj

typedef struct {

float freqTone;

float freqSampRate;

float a;

float b;

float y0;

float y1;

float y2;

float count;

float aInitVal;

float bInitVal;

float y0InitVal;

float y1InitVal;

float y2InitVal;

float countInitVal;

} SINE_Obj;

#endif

void copyData(short *inbuf, short *outbuf ,int length);

void SINE_init(SINE_Obj *sineObj, float freqTone, float freqSampRate);

void SINE_blockFill(SINE_Obj *myObj, short *buf, int len);

void SINE_addPacked(SINE_Obj *myObj, short *inbuf, int length);

void SINE_add(SINE_Obj *myObj, short *inbuf, int length);

```

#### sine.c

```

// ====== sine.c ======

// The coefficient A and the three initial values

// generate a 200Hz tone (sine wave) when running

// at a sample rate of 48KHz.

//

// Even though the calculations are done in floating // point, this function returns a short value since // this is what's needed by a 16-bit codec (DAC).

// ====== Includes ======

#include "sine.h"

#include <std.h>

#include <math.h>

// ====== Definitions ======

#define PI 3.1415927

// ====== Prototypes ======

void SINE_init(SINE_Obj *sineObj, float freqTone, float freqSampRate);

void SINE_blockFill(SINE_Obj *sineObj, short *buf, int len);

void SINE_addPacked(SINE_Obj *sineObj, short *inbuf, int length);

void SINE_add(SINE_Obj *sineObj, short *inbuf, int length);

static short sineGen(SINE_Obj *sineObj);

static float degreesToRadiansF(float d);

void copyData(short *inbuf, short *outbuf ,int length );

// ====== Globals ======

// ====== SINE_init ======

// Initializes the sine wave generation algorithm

void SINE_init(SINE_Obj *sineObj, float freqTone, float freqSampRate)

float rad = 0;

if(freqTone == NULL)

sineObj->freqTone = 200;

else

sineObj->freqTone = freqTone;

if(freqSampRate == NULL)

sineObj->freqSampRate = 48 * 1024;

else

sineObj->freqSampRate = freqSampRate;

rad = sineObj->freqTone / sineObj->freqSampRate;

rad = rad * 360.0;

rad = degreesToRadiansF(rad);

sineObj->a = 2 * cosf(rad);

sineObj->b = -1;

sineObj->y0 = 0;

sineObj->y1 = sinf(rad);

sineObj->y2 = 0;

sineObj->count = sineObj->freqTone * sineObj->freqSampRate;

```

### sine.c (continued)

```

sineObj->aInitVal = sineObj->a;

sineObj->bInitVal = sineObj->b;

sineObj->y0InitVal = sineObj->y0;

sineObj->y1InitVal = sineObj->y1;

sineObj->y2InitVal = sineObj->y2;

sineObj->countInitVal = sineObj->count;

// ====== SINE_blockFill ======

// Generate a block of sine data using sineGen

void SINE_blockFill(SINE_Obj *sineObj, short *buf, int len)

int i = 0;

for (i = 0;i < len; i++) {

buf[i] = sineGen(sineObj);

// ====== SINE_addPacked ======

// add the sine wave to the indicated buffer of packed

// left/right data

// divide the sine wave signal by 8 and add it

void SINE_addPacked(SINE_Obj *sineObj, short *inbuf, int length)

int i = 0;

static short temp;

for (i = 0; i < length; i+=2) {

temp = sineGen(sineObj);

inbuf[i] = (inbuf[i]) + (temp>>4);

inbuf[i+1] = (inbuf[i+1]) + (temp>>4);

// ====== SINE_add ======

// add the sine wave to the indicated buffer

void SINE_add(SINE_Obj *sineObj, short *inbuf, int length)

int i = 0;

short temp;

for (i = 0; i < length; i++) {

temp = sineGen(sineObj);

inbuf[i] = (inbuf[i]) + (temp>>4);

```

### sine.c (continued)

```

====== sineGen ======

// Generate a single sine wave value

static short sineGen(SINE_Obj *sineObj)

if (sineObj->count > 0) {

float result;

sineObj->count = sineObj->count - 1;

else {

sineObj->a = sineObj->aInitVal;

sineObj->b = sineObj->bInitVal;

sineObj->y0 = sineObj->y0InitVal;

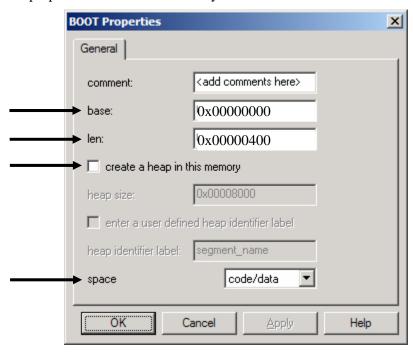

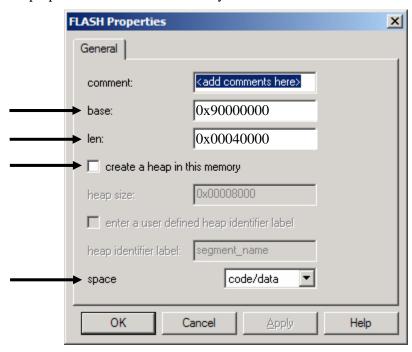

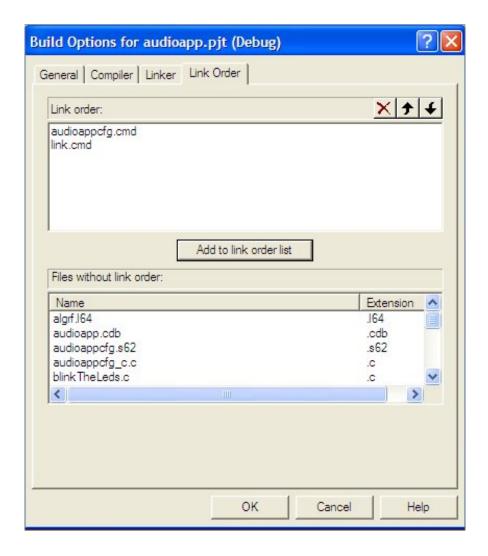

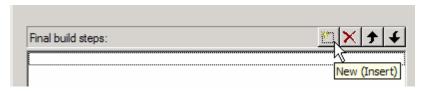

sineObj->y1 = sineObj->y1InitVal;