# TMS320C240x DSP Design Workshop

Student Guide

DSP24 Revision 4.2 February 2002

## **Important Notice**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, 1999, 2000, 2001, 2002 Texas Instruments Incorporated

## **Revision History**

September 1998 – Revision 1.0

March 1999 – Revision 2.0

April 2000 – Revision 3.0

May 2000 - Revision 3.1

January 2001 – Revision 4.0

June 2001 – Revision 4.1

February 2002 – Revision 4.2

## **Mailing Address**

Texas Instruments Training Technical Organization 7839 Churchill Way M/S 3984 Dallas, Texas 75251-1903

# Introduction

# TMS320C240x DSP Design Workshop

**Texas Instruments Technical Training**

### Introductions

- ◆ Name

- **♦** Company

- ◆ Project Responsibilities

- **♦ DSP / Microcontroller Experience**

- **◆ TMS320 DSP Experience**

- ◆ Hardware / Software Assembly / C

- ♦ Interests

### TMS320C240x Workshop Outline

- 1. Introduction and Architectural Overview

- 2. Program Development Tools

- 3. Addressing Modes

- 4. Basic Programming Techniques

- 5. Advanced Programming Techniques

- 6. Numerical Issues

- 7. Implementing Algorithms

- 8. Logical Operations

- 9. System Initialization

- 10. Interrupts

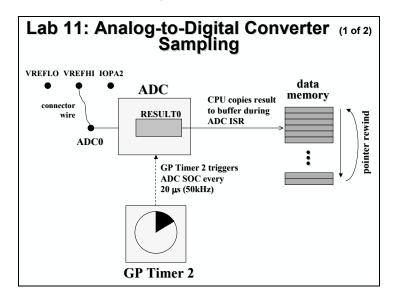

- 11. Analog-to-Digital Converter

- 12. Event Manager

- 13. System Design

- 14. Communications

- 15. C Compiler

- 16. Development Support

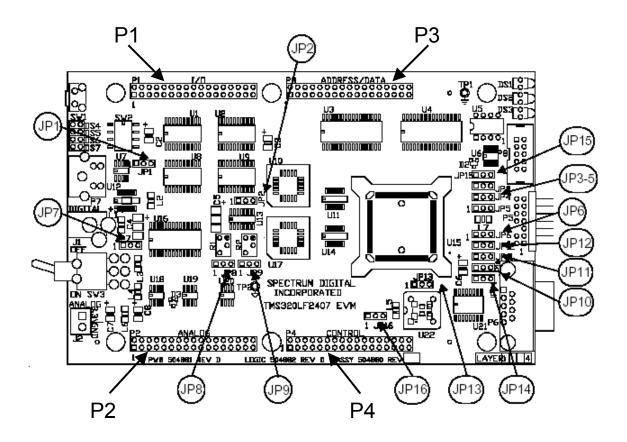

## Spectrum Digital TMS320LF2407 EVM

# Introduction and Architectural Overview

### Introduction

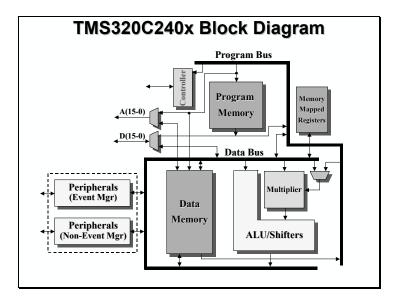

The TMS320C240x family of Digital Signal Processors combines the enhanced C2xx architectural CPU core with peripherals optimized for digital motor/motion control applications. This module will give an overview to the device architecture and serve as the basic foundation to this workshop.

Unless otherwise noted, the terms TMS320C240x and C240x refer to TMS320C24x, TMS320F24x, TMS320LC240x, and TMS320LF240x throughout the remainder of these notes. For specific details and differences please refer to the device data sheet and user's guide.

# **Learning Objectives**

#### **Learning Objectives**

- ◆ Explain basic TMS320C240x block diagram

- List key features of C240x memory map, bus structures, and peripherals

- ◆ Describe differences among C240x devices

# **Module Topics**

| Introduction and Architectural Overview | 1-1  |

|-----------------------------------------|------|

| Module Topics                           |      |

| TMS320C240x Architecture Basics         |      |

| CPU                                     | 1-4  |

| Program Memory                          | 1-5  |

| Data Memory                             | 1-5  |

| Memory Map                              |      |

| Pipeline                                |      |

| Peripherals                             |      |

| TMS320C240x Instruction Set             |      |

| Review                                  | 1-10 |

#### TMS320C240x Architecture Basics

The TMS320C240x uses a *modified Harvard* architecture. These modifications consist of enhancements to the strict Harvard architecture in the form of features from the von Neumann architecture. Those features include the ability to initialize data memory from program memory, and the ability to transfer data memory to program memory. This capability allows the C240x to time-division multiplex its memory between tasks as well as to initialize its data memory with constants (for example, a coefficient) stored in the system's program ROM. This minimizes system cost by eliminating the need for a data ROM and maximizes data memory utilization by allowing dynamic redefinition of data memory's function.

The most important reason for basing the C240x on the Harvard architecture is speed. Separate data and program space allow simultaneous fetching of program instructions and data. In a mathematically intensive application, this effectively doubles algorithm throughput compared to (standard) von Neumann-type processors.

#### **CPU**

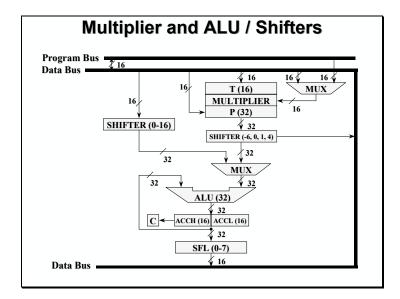

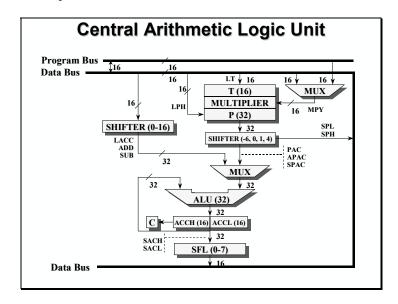

The Central Processing Unit (CPU) incorporates the multiplier and central arithmetic logic unit (CALU) along with three shifters and several program control registers.

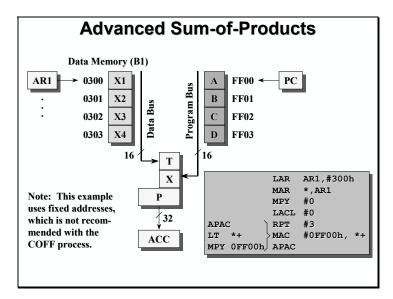

# Multiplier

The hardware multiplier is designed to perform a multiply in a single machine cycle. One input comes from the temporary register (T) and the other comes from the data bus or the program bus. The 32-bit result is stored in the product register (P), which is then available to the CALU.

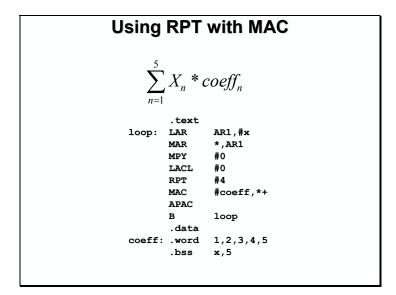

The C240x has multiply/accumulate instructions which execute in a single cycle when used in repeat instructions.

## Central Arithmetic Logic Unit (CALU)

The Central Arithmetic Logic Unit (CALU) contains the ALU and three separate shifters. The ALU performs single-cycle logical or arithmetic operations. Results are stored in the 32-bit accumulator (ACC).

The C240x has a pre-scaling shifter from the data bus to the ALU, a post-scaling barrel shifter from the ACC to the data bus and a product shifter for scaling the multiplier results.

An ALU instruction is always performed as follows:

- 1. Data is read from RAM on the data bus.

- 2. Data is passed through the scaling shifter and to the ALU where the operation is performed.

- 3. The result is found in the accumulator.

One input to the ALU is always provided by the accumulator. The other may be transferred from the product register (P) or from the scaling shifter that is loaded from data memory.

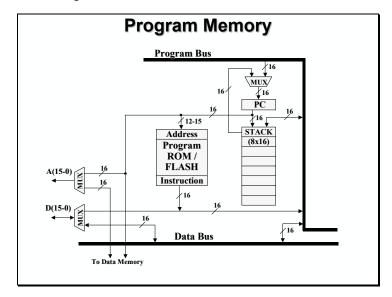

# **Program Memory**

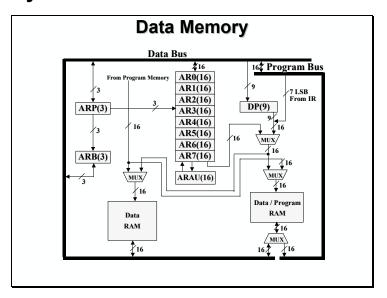

# **Data Memory**

# **Memory Map**

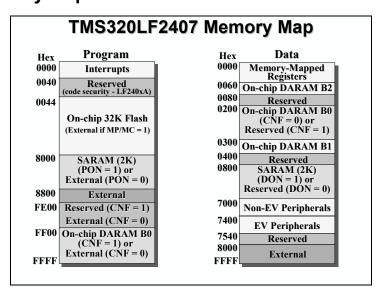

The C240x memory space is divided into three regions:

- 64K program

- 64K data

- 64K I/O

The C240x has a minimum of 544 words of on-chip RAM, which is sometimes referred to as dual-access RAM. It can implement the action of a delay line without the need for "circular buffering" as any other memory would. On reset, this memory is found in data space, but a portion of it may be relocated under software control to program space.

The second on-chip memory is ROM, which is located at the beginning of program space. It may be used or bypassed under control of the  $MP/\overline{MC}$  signal line. The amount of on-chip non-volatile memory (ROM or flash) varies based on the C240x device.

| 0000 Interrupts<br>0040 Reserved      | 0000 Memory-Mapped<br>Registers   |

|---------------------------------------|-----------------------------------|

| 0040 Decomod                          |                                   |

| (code security - LF240xA)             | 0060 On-chip DARAM B2             |

| 0044                                  | 0080 Reserved                     |

| On-chip 32K Flash                     | (CNF = 0) or                      |

| (External if $MP/\overline{MC} = 1$ ) | Reserved (CNF = 1)                |

|                                       | On-chip DARAM B1                  |

| SARAM (2K)<br>(PON = 1) or            | 0800 Reserved<br>SARAM (2K)       |

| External (PON = 0)                    | (DON = 1) or Reserved $(DON = 0)$ |

| External                              | 7000                              |

| TE00 Reserved (CNF = 1)               | Non-Ev Peripherals                |

| External (CNF = 0) On-chip DARAM B0   | 7400 EV Peripherals               |

| (CNF = 1) or                          | 7540 Reserved<br>8000             |

# **Pipeline**

The C240x has an instruction pipeline which results in a more efficient operation of program execution. The instruction fetch-decode-read-execute pipeline phases are independent of each other. Instructions overlap such that, in a given cycle, up to four different instructions can be active, each at a different stage completion.

|       | F                                        | Pipel          | line l         | Proc           | ess            |                |                |

|-------|------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|

|       |                                          | Cycle          |                |                |                |                |                |

|       | 100                                      | 101            | 102            | 103            | 104            | 105            | 106            |

| Add   | F <sub>1</sub>                           | $\mathbf{D}_1$ | R <sub>1</sub> | E <sub>1</sub> |                |                |                |

| Sub   |                                          | F <sub>2</sub> | D <sub>2</sub> | R <sub>2</sub> | E <sub>2</sub> |                |                |

| Мру   |                                          |                | F <sub>3</sub> | $D_3$          | R <sub>3</sub> | E <sub>3</sub> |                |

| Store |                                          |                |                | F <sub>4</sub> | D <sub>4</sub> | R <sub>4</sub> | E <sub>4</sub> |

|       | Fully loaded pipeline (normal operation) |                |                |                |                |                |                |

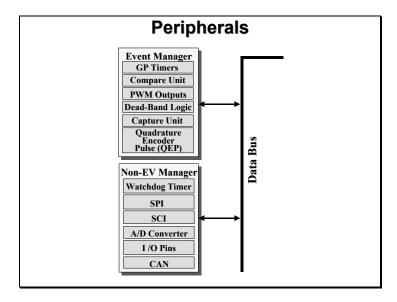

# **Peripherals**

The C240x devices contain peripherals optimized for motor/motion control applications. For many systems, this could provide a low-cost, high performance solution.

#### TMS320C24xx Family TMS320 Devices PWM Channels I/O Pins ROM Compares / Captures GP Time ARAM QEP CAN C/F240 16K 9/4 Yes 28 12 F241 8K 5/3 2 26 2 Yes Yes 2 Yes F243 8K 5/3 2 Yes 32 LF2401 8K 0.5K 4/1 2 13 No No 5/3 2 LC/F2402 6 / 8K 8 2 No 21 0.5K 5/3 2 Yes 21 Yes 41 LC2404 1K 10/6 4 No Yes LC/F2406 32K 2K 16 10/6 4 Yes Yes 41 LF2407 10/6 Yes 41

ONLY - C/F240, F243, and F2407 includes an external memory interface All Devices Include - 544 Words of DARAM, Watchdog Timer, SCI (UART), and ADC

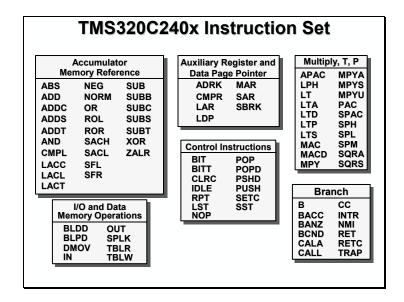

#### TMS320C240x Instruction Set

The instruction set for the TMS320C240x is identical to that of the TMS320C2xx. This instruction set supports numerically intensive signal processing operations, as well as general-purpose applications. The instruction set is compatible with the TMS320C2x instruction set, and is a subset of the TMS320C5x instruction set.

#### **C Language Programming**

The C compiler is a full implementation of the ANSI standard and outputs assembly language source code. The C compiler supports in-line assembly code; calling assembly language from C and calling C from assembly. Additionally, variables defined in C source can be addressed in the assembly code and vice versa. By allowing a mixture of C and assembly languages, the programmer can use C to achieve faster code development and use assembly language to write those segments that require optimal performance.

C code is relatively efficient on the TMS320, given the availability of an optimizer which may be invoked during compilation. Special internal hardware, such as the eight auxiliary registers, greatly improves the speed of stack and pointer operations.

The module, "C Compiler," covers many of the issues associated with the C compiler for fixed-point devices.

## **Review**

#### **Review**

- 1. Why a modified "Harvard" Architecture?

- 2. What are the two major buses?

- 3. Describe on-chip memory resources.

- 4. Arithmetic Logic Unit width?

- 5. Multiplier input and results width?

# **Program Development Tools**

### Introduction

The goal of this module is to understand the basics of writing assembly language programs using the standard Common Object File Format (COFF) tools used by Texas Instruments. This involves understanding the basic structure of the assembly file, along with the basic operation of the assembler and linker.

# **Learning Objectives**

#### **Learning Objectives**

- Describe steps to create executable output files

- **◆** Create an assembly file containing:

- Code

- Constants (initialized data)

- Variables

- **♦** Create a linker command file which:

- Describes a system's available memory

- Indicates where code and data shall be located

- Write system reset code

# **Module Topics**

| Program Development Tools                                                                                                          | 2-1                        |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Module Topics                                                                                                                      | 2-2                        |

| COFF Concepts                                                                                                                      |                            |

| Assembly Tools Assembler Linker                                                                                                    |                            |

| Assembly Conventions                                                                                                               |                            |

| Creating the Assembly File  Program Code  Constants (initialized data)  Variables (uninitialized data)  Completed Example  Summary | 2-9<br>2-9<br>2-10<br>2-11 |

| Exercise 1                                                                                                                         |                            |

| Lab 2a                                                                                                                             | 2-13                       |

| Linking Assembly Code                                                                                                              | 2-15                       |

| Linker Command Files (.cmd)  Files - input and output  Memory-Map Description  Section Placement  Exercise 2.                      | 2-16<br>2-16<br>2-18       |

| Summary: Linker Command File                                                                                                       |                            |

| Lab 2b                                                                                                                             | 2-21                       |

| Multiple SectionsCreating Your Own Sections                                                                                        |                            |

| Reset Vector Setting Up a Reset Vector Referencing Labels Linker Command File                                                      |                            |

| Exercise 3                                                                                                                         | 2-30                       |

| Summary                                                                                                                            | 2-32                       |

| Lab 2c                                                                                                                             | 2-33                       |

| ReviewSolutions                                                                                                                    | 2-36                       |

## **COFF Concepts**

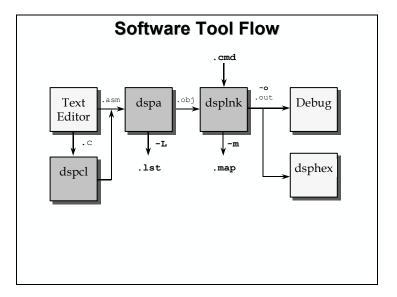

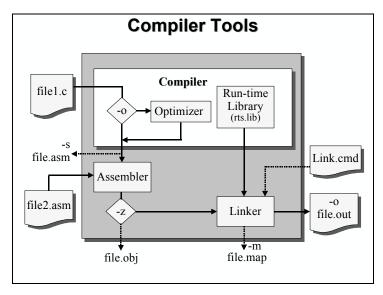

In an effort to standardize the software development process, TI has selected the Common Object File Format (COFF). COFF has several features which make it a powerful software development system. It is most useful when the development task is split between several programmers.

Each file of code, called a *module*, may be written independently, including the specification of all resources necessary for the proper operation of the module. Modules are written in assembly-level mnemonics using any word processor capable of providing a simple ASCII file output. The expected extension of a source file is .ASM, which stands for *assembly*.

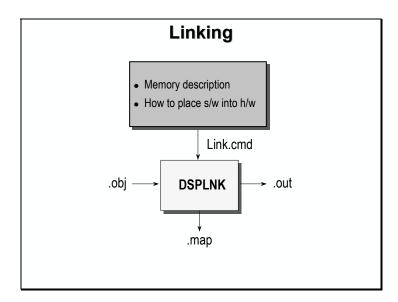

Next, each of these modules is *assembled* to translate the mnemonic-level code to a binary representation which is recognizable by the TMS320; this results in the object file .OBJ. A list, .LST, file is optionally produced to document the assembled results.

Numerous modules may be joined to form a complete program. The linker is a software tool capable of efficiently allocating the resources available on the TMS320 to each module in the system. The linker is able to refer to a command (.CMD) file which identifies all the input and output file names, the resources available on the TMS320, and where the various sections within each module are to go. Outputs of the linking process may include the linked object file (.OUT), which runs on the TMS320, and a .MAP file which identifies where each linked section is located.

The high level of modularity and portability resulting from this system simplifies the processes of verification, debug and maintenance. The process of COFF development is presented in greater detail in the following paragraphs.

The concept of COFF tools is to allow modular development of software independent of hardware concerns. An individual assembly language file is written to perform a single task and may be linked with several other tasks to achieve a more complex total system.

Writing code in modular form permits code to be developed by several people working in parallel so the development cycle is shortened. Debugging and upgrading code is faster, since components of the system, rather than the entire system, is being operated upon. Also, new systems may be developed more rapidly if previously developed modules can be used in them.

Code developed independently of hardware concerns increases the benefits of modularity by allowing the programmer to focus on the code and not waste time managing memory and moving code as other code components grow or shrink. A linker is invoked to allocate systems hardware to the modules desired to build a system. Changes in any or all modules, when re-linked, create a new hardware allocation, avoiding the possibility of memory resource conflicts.

# **Assembly Tools**

#### **Assembler**

The assembler translates assembly-language source code using instruction mnemonics and symbols into relocatable object code.

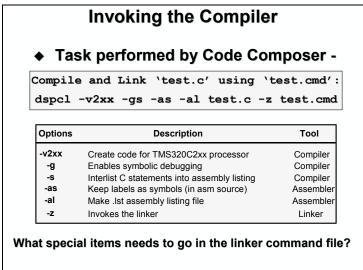

The most common options are summarized in the table below:

| Option  | Action                                 |

|---------|----------------------------------------|

| -v10    | Produce 'C1x code                      |

| -v25    | Produce 'C2x code                      |

| -v2xx   | Produce 'C2xx code                     |

| -v50    | Produce 'C5x code                      |

| -L (-l) | Create listing file (none by default)  |

| -s      | Put all symbols in .obj file for debug |

When the -L option is specified, the resultant listing file is useful because it contains the output of the assembler and shows any errors and warnings with the associated line of code. The fields in the listing file are shown in the *Fixed-Point Assembly Language Tools User's Guide*.

#### Linker

The linker maps relocatable software (object-level code) to the users system hardware.

The command file includes:

- System memory configuration

- Allocation of code and data across system memory

# **Assembly Conventions**

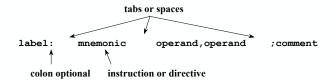

Before we begin writing code let's look at some assembly coding conventions.

#### **Assembly Conventions**

- ♦ Use any ASCII text editor

- ♦ Use .asm extension

- Instructions and directives <u>cannot</u> be in first column

- Comments O.K. in any column after semicolon or "\*" (asterisk) in column one

#### **Assembly Files**

- **♦** Mnemonics

- Lines of TMS320 code, "processor code"

- Become components of program memory

- Directives

- Begin with a period (.) and are lower case

- Can create constants and variables

- May occupy no memory space when used to control ASM and LNK process

### **Assembler Constants**

| Туре              | Examples                                    |

|-------------------|---------------------------------------------|

| Binary            | 1110001b or 11111001B                       |

| Octal             | 226q or 572Q                                |

| Decimal           | 1234 or +1234 or -1234 (Default)            |

| Hexadecimal       | 2A40h or 2A40H or 0FF00h                    |

| Floating-point    | 1.623e-23 (sign and decimal point optional) |

| Character         | 'D'                                         |

| Character strings | "this is a string"                          |

**Note:** A Hexadecimal constant cannot begin with a letter, start it with "0" instead; for example, use 0FF00h, not FF00h.

# **Creating the Assembly File**

Assembly files consists of three main sections:

- Program Code

- Initialized data (constants)

- Uninitialized data (variables)

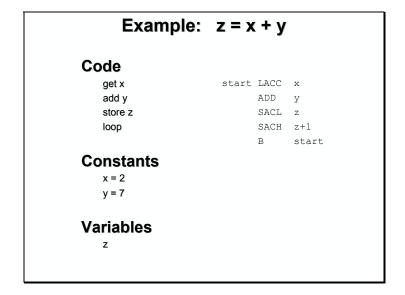

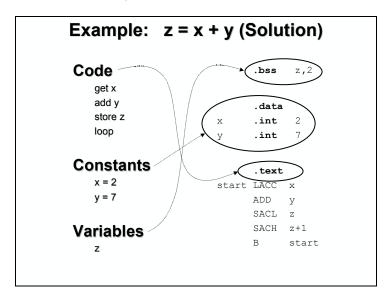

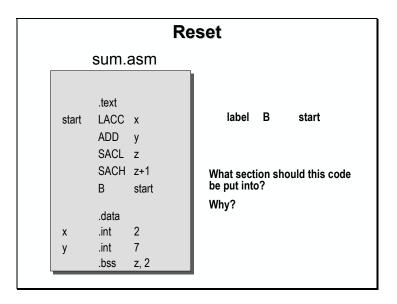

These sections are examined in the following assembly file which solves: z = x + y

### **Program Code**

Program code consists of the sequence of instructions used to manipulate data. Specific instructions are discussed in detail later in the workshop.

Program code must be defined upon system reset (power turn-on). Due to this basic system constraint, it is usually necessary to place program code into non-volatile memory chips, such as EPROM's.

The previous example used boldface titles to indicate the different sections of the assembly file. The assembler requires you to 'tag' each section, but its command uses a slightly different syntax.

#### > Define the Code Section

The assembler directive (assembler command) to delineate the code section is .text.

|       | .text |       |

|-------|-------|-------|

| start | LACC  | X     |

|       | ADD   | У     |

|       | SACL  | Z     |

|       | SACH  | z+1   |

|       | В     | start |

## **Constants (initialized data)**

Initialized data are those data memory locations defined at reset. They contain constants or initial values for variables. Similar to program code, constant data is expected to be valid upon reset of the system. It is often found in EPROM or other non-volatile memory.

#### > Define the Constants Section

Defining initialized data requires two assembler directives:

- 1. One to define the section: .data

- 2. The second "builds" a constant by reserving a memory location and placing a value into it: .int

Our previous example used two integer constants, which are defined using two .int directives. The constant's name, called 'label' or 'symbol' is on the left, while the initial value assigned is placed on the right:

|   | .data |   |

|---|-------|---|

| Х | .int  | 2 |

| V | .int  | 7 |

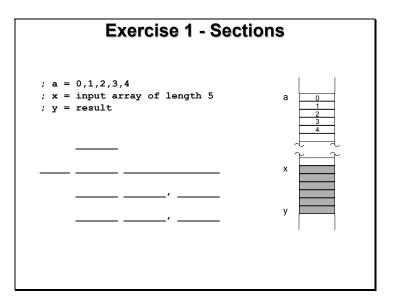

### Variables (uninitialized data)

Uninitialized data memory locations can be changed and manipulated by the program code during runtime execution. Unlike program code or constants, variables must reside in volatile memory, such as RAM. These memories can be modified and updated, supporting the way variables are used in math formulas, high-level languages, and such.

Each variable must be declared with an assembler directive to reserve memory to contain its value. By their nature, no value is assigned by the assembler or linker; instead they must be loaded at runtime by the program code.

#### > Define the Variables Section

The syntax for variables includes the:

- assembler directive (.bss)

- symbol (label) on the *right* side

- size of variable

The variable z from our earlier example, would be declared:

.bss z,2

Declare an array of memory locations called x of length five with:

.bss x,5

#### .bss Tips

- Only directive with label in the operand field

- Use separate .bss statements for each named variable

- Remember .bss by thinking:

- Block reserves a block of memory

- Symbol beginning at address symbol

- Size of the specified size

- Example: Create a 5-word array 'x'

.bss x,5

# **Completed Example**

Putting together all of these sections yields:

# **Summary**

| Assembler<br>Directive | Example         | Definition                         |

|------------------------|-----------------|------------------------------------|

| .text                  | .text           | Code to follow                     |

| .data                  | .data           | Constants to follow                |

| .bss                   | .bss x, 10      | Allocate space for Variables       |

| .int<br>.word          | A .int 53h, 5Ah | Creates 16-bit integer constant(s) |

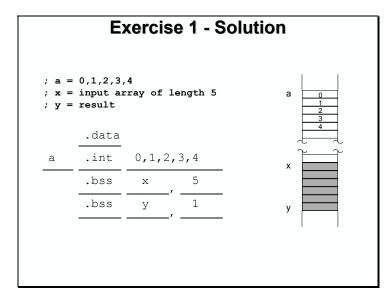

# **Exercise 1**

For a little more practice, let's go through another example to define the constants and variables needed for the following a sum-of-products:

$$y = \sum_{n=0}^{4} a(n) * x(n)$$

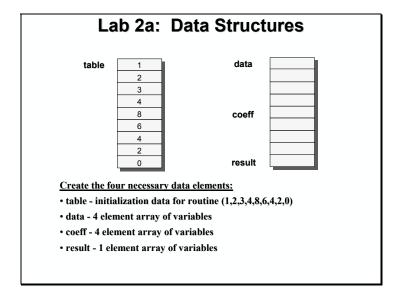

### Lab 2a

#### Objective

In Labs 2, 3, and 4 you will create a Sum-of-Products routine, multiplying and summing two arrays of four elements each. Lab 2 takes you through setting up the data structures and sections. Lab 3 practices data addressing by initializing the data and coefficient arrays. Lab 4 is where you will write the actual Sum-of-Products routine.

We begin the process by setting up the sections necessary to perform a sum-of-products.

Create the four necessary data elements:

- table Initialization data for the routine (1,2,3,4,8,6,4,2,0)

- data 4 element array of variables

- coeff 4 element array of variables

- result 1 element array of variables

**Note:** For those already comfortable with COFF Assembler syntax and Code Composer, try creating LAB2.ASM to accomplish the objectives above. If you're new to this syntax — or a bit rusty on assembler programming in general — the next page provides a step-by-step procedure.

#### Procedure

### **Create a New Project**

1. Double click on the Code Composer icon on the desktop. Maximize Code Composer to fill your screen. The menu bar (at the top) lists File ... Help. Note the horizontal tool bar below the menu bar and the vertical tool bar on the left-hand side. The window on the left is the project window and the large right hand window is your workspace.

2. A *project* is all the files you'll need to develop an executable output file (.OUT) which can be run on the target hardware. Let's create a new project for this lab. On the menu bar click:

```

Project → New

```

and make sure the "SAVE IN" location is: C:\DSP24\LABS and type LAB2 in the file name window. This will create a *make* file which will invoke all the necessary tools (assembler, linker, compiler) to build your project.

3. Add the assembly file to the new project. Click:

```

Project → Add Files to Project

```

and make sure you're looking in C:\DSP24\LABS. Change the "files of type" to view assembly files (.ASM) and select LAB2.ASM and click OPEN. This will add the file LAB2.ASM to your newly created project.

- 4. Add LAB2. CMD to the project using the same procedure. This will be used during Lab 2b.

- 5. In the project window on the left click the plus sign (+) to the left of Project. Now, click on the plus sign next to LAB2.MAK. Notice that the LAB2.CMD file is listed. Click on Source to see the current source file list (i.e. LAB2.ASM).

#### **Edit LAB2.ASM**

- 6. To open and edit LAB2. ASM, double click on the file in the project window. The code you see in this file is not related to setting up the data structures and sections. It is simply a place holder for use during future labs.

- 7. Define three arrays in RAM as described on the "Lab 2a: Data Structures" slide by creating uninitialized sections called *data*, *coeff*, and *result*. Refer to the diagram for the sizes.

- 8. Define an initialized data table section called *table* that contains the nine values shown on the "Lab 2a: Data Structures" slide.

- 9. Define an initialized program section for code above the beginning label of the code (*start*). Save your changes by clicking the disk on the horizontal tool bar "Save", or on the menu bar click: File → Save

#### Assemble LAB2.ASM

10. Assemble LAB2. ASM by clicking on the top button on the vertical toolbar (or on the menu bar click: Project → Compile File). When your mouse hovers over this button, you will see the words Compile File. Check for errors. If you get an assembly error, scroll the Build window at the bottom of your screen until you can see the error and simply double-click the error shown in red. Your cursor should now be positioned at the start of the line with the error in your assembly file. We added a little error (in addition to any others you may have made) so you could see how Code Composer reacts. To correct the error, replace label 'strt' with 'start'. Save your changes and compile the file again. When completed (No Errors, No Warnings), you can close the LAB2. ASM edit window.

#### **End of Exercise**

# **Linking Assembly Code**

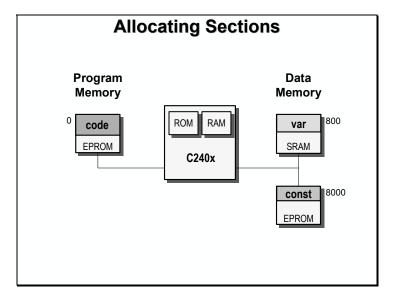

The three sections of an assembly file, discussed earlier, must be located in different memories in your *target system*. This is the big advantage of creating the separate sections for code, constants, and variables. In this way, they can all be linked (located) into their proper memory locations in your target embedded system.

Generally, they're located as follows:

#### **Program Code**

Program code must be defined upon system reset (power turn-on). Due to this basic system constraint it is usually necessary to place program code into non-volatile memory chips, such as EPROM's.

#### Constants (initialized data)

Initialized data are those data memory locations defined at reset. Similar to program code, constant data is expected to be valid upon reset of the system. It is often found in EPROM or other non-volatile memory.

#### Variables (uninitialized data)

Uninitialized data or variables must reside in volatile memory, such as RAM so they can be modified and updated.

# Linker Command Files (.cmd)

The linker concatenates each section from all input files, allocating memory to each section based on its length and location as specified by the MEMORY and SECTIONS commands in the linker command file.

### Files - input and output

The two most common linker options are -o to specify the output file name, and -m to specify a map file name.

### **Memory-Map Description**

Describe the memory configuration of your target system to the linker. Without this specification, the linker might place code or data into memory that doesn't exist.

For example, if you placed an 2K EPROM starting at memory location zero, it would read:

```

MEMORY

{

NAME: origin = 0000h , length = 0800h

}

```

You define each memory segment using the above format. If you added a RAM and an ABT646 transceiver, it might look like:

```

MEMORY

{

EPROM: origin = 0000h , length = 0800h

RAM: origin = 1000h , length = 02000h

ABT646: origin = 8000h , length = 00001h

```

Remember that the C240x processors have three memory maps: *Program*, *Data*, and *I/O*. Therefore, the MEMORY description must describe each of these separately. TI's loader uses the following syntax to delineate each of these:

| Linker Page | TI Definition |

|-------------|---------------|

| Page 0      | Program       |

| Page 1      | Data          |

| Page 2      | I/O           |

# **Memory Suggestions**

- Describe each memory resource on the processor (internal RAM and/or ROM)

- 2. Describe each external memory chip in your system

- 3. Combine contiguous memory segments, if desired

- 4. Split any memory segment into multiple segments, if desired

- 5. Name memory segments with useful names; e.g.:

- Types of memory chips (EPROM, RAM, EEPROM)

- · Usage (vectors, code, variables)

- · Chip layout names (U1, E2)

### **Section Placement**

You can specify how you want the sections to be distributed through memory. You would use the following code to link the three sections into the memory specified in the former example:

```

SECTIONS

{

.text:> EPROM

.data:> DEPROM

.bss:> SRAM

}

```

The linker will gather all the .text sections from all the files being linked together. Similarly, it will combine all 'like' sections.

Beginning with the first section listed, the linker will place it into the specified memory segment.

```

Linker Command File

MEMORY

{

PAGE 0:

/* Program */

org = 00\bar{0}0h, len = 0800h

EPROM:

/* Data */

PAGE 1:

SRAM: org = 0800h, len = 2000h

DEPROM: org = 8000h, len = 2000h

SECTIONS

.text:> EPROM

PAGE 0

.data:> DEPROM

PAGE 1

PAGE 1

.bss:>

SRAM

```

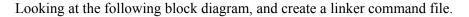

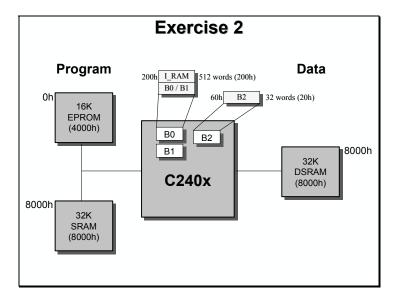

# **Exercise 2**

Fill in the blanks:

```

Exercise 2 - Command File

MEMORY

PAGE_:

/* Program Memory */

__: org = _

_, len =

/* Data Memory */

B2__: org = _

_, len =

__: org = ____, len =

: org = _

_, len =

SECTIONS

.text: > EPROM

.bss: > DSRAM

.data: > I_RAM

PAGE 0

PAGE 1

PAGE 1

/* I_RAM = B0 + B1 */

```

The answer should look like:

```

Exercise 2 - Solution

MEMORY

/* Program Memory */

PAGE 0:

EPROM: org = 0000h,

len = 4000h

SRAM:

org = 8000h, len = 8000h

PAGE 1:

/* Data Memory */

org = 0060h, len = 0020h

I RAM: org = 0200h,

len = 0200h

\overline{DSRAM}: org = 8000h, len = 8000h

SECTIONS

.text: > EPROM

PAGE 0

.bss: > DSRAM

PAGE 1

.data: > I_RAM

PAGE 1

/* I_RAM = B0 + B1 */

```

## **Summary: Linker Command File**

The linker command file (.cmd) contains the inputs — commands — for the linker. This information is summarized below:

### **Linker Command File Summary**

- ♦ Memory Map Description

- Name

- Location

- Size

- Attributes

- Sections Description

- Directs software sections into named memory regions

- Allows per-file discrimination

- Allows separate load/run locations

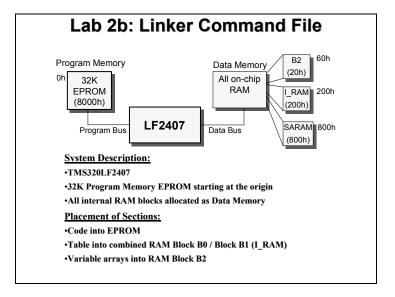

### Lab 2b

#### Objective

Link your assembly file (LAB2.ASM) into the system described below. Create a linker command file as part of this process.

#### **System Description**

- TMS320LF2407

- 32K Program EPROM starting at the origin

- All internal RAM blocks allocated as Data memory

#### **Placement of Sections:**

- Code into EPROM

- Table into combined RAM Block B0 / Block B1 (I RAM)

- Variable arrays into RAM Block B2

#### > Procedure

#### Edit LAB2.CMD

- 1. To open and edit LAB2.CMD, double click on the filename in the project window.

- 2. Edit the Memory { } declaration by describing the system memory shown on the "Lab2b: Linker Command File" slide.

- 3. Place the sections defined in LAB2. ASM into the appropriate memories via the Sections { } area. Save your work.

#### Link LAB2

4. Setup the linker options by clicking:

Project → Options

on the menu bar. Select the Linker tab. In the middle of the screen select "No Autoinitialization". Create a map file by typing LAB2.MAP in the Map Filename [-m] field.

Next, select the Assembler tab. In the middle of the screen check "Enable Source Level Debugging". This feature will be useful during the next part of the lab.

Then select OK to save the Build Options. To open up more workspace, close any open files that you do not need.

5. The top four buttons on the vertical toolbar control code generation. Hover your mouse over each button as you read the following descriptions:

| Button | Name              | Description                                     |

|--------|-------------------|-------------------------------------------------|

| 1      | Compile File      | Compile, assemble the current open file         |

| 2      | Incremental Build | Compile, assemble only changed files, then link |

| 3      | Rebuild All       | Compile, assemble all files, then link          |

| 4      | Stop Build        | Stop code generation                            |

- 6. Click the "Rebuild All" button and watch the tools run in the build window. Debug as necessary. Right-click on the build window and Hide the build window. Close the LAB2.CMD edit window.

- 7. Open and inspect LAB2.MAP. Make sure you are looking in C:\DSP24\Labs. This file will show you the results of the link process. Note the addresses for the sections. What address does it indicate for:

| text_ | 5      |  |

|-------|--------|--|

|       |        |  |

| data  | a<br>a |  |

|       |        |  |

| bss   |        |  |

Are the results as expected? Close the .MAP file when you are done.

8. Load the output file onto the target. Click:

File → Load Program...

Make sure you are looking in C:\DSP24\Labs. Select LAB2.OUT and click OPEN.

Note: Code Composer can automatically load the output file after a successful build. On the menu bar click: Option → Program Load... and select: "Load program after build", then click OK.

- 9. If code generation is successful, the Dis-Assembly window will display the LAB2.ASM source file and a yellow highlight on the line at address "0000h" should appear. This indicates that you are now ready to run.

- 10. On the menu bar click:

View → Memory

or click the View Memory button on the vertical toolbar. Type "table" into the address to display the contents of the memory starting at label *table*. (Note: Code Composer is case sensitive). You can display as many independent windows as you require. Do you see your initial values in the memory window displaying "table"?

Note that by double-clicking on any location you can edit the contents of the memory location.

11. Close the Dis-Assembly and Memory windows (and source window, if open).

### **End of Exercise**

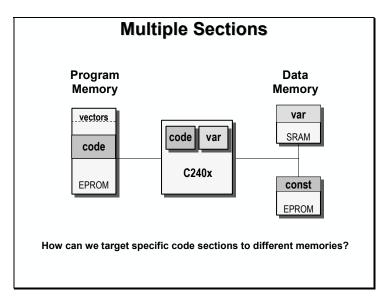

# **Multiple Sections**

We've spoken of placing sections in memory, but what if we want to put code — or data — in more than one location?

For example, if you wanted to run some code from EPROM and the critical routines from internal memory.

# **Creating Your Own Sections**

Two assembler directives allow you to create and name your own sections. These allow programmers to create multiple constant-data, program-code, or variable-data sections and link them to different memory locations.

|                        | Mı         | ultiple Sect   | ions                                       |  |  |

|------------------------|------------|----------------|--------------------------------------------|--|--|

| Assembler<br>Directive | E          | xample         | Description                                |  |  |

| ect                    | .se        | ct "vectors"   | Creates initialized sections:              |  |  |

| sect                   | label .use | ect "name", 23 | Creates uninitialized sections • variables |  |  |

|                         | Unnamed<br>Sections | User Named<br>Sections     |

|-------------------------|---------------------|----------------------------|

| Initialized<br>Memory   | .text<br>.data      | .sect "name"               |

| Uninitialized<br>Memory | .bss symbol, size   | symbol .usect "name", size |

### **Bottom Line**

Use .sect and .usect directives whenever you need to place code or data in specific memory locations.

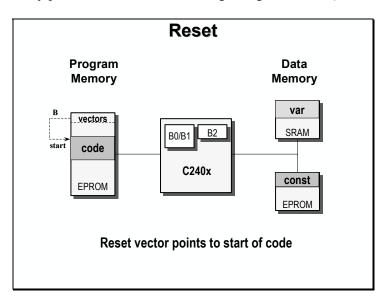

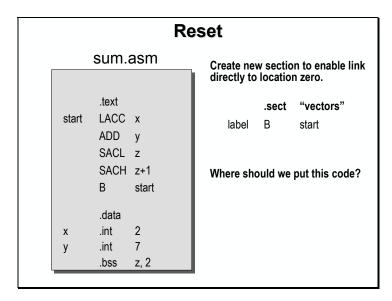

### **Reset Vector**

Finally, how do we start from the beginning?

All real-world programs begin at RESET. Here's the basic sequence of events when the  $\overline{\text{RESET}}$  pin is toggled low by the hardware or debugger:

- Pins and registers are set to specific values (discussed later)

- Program Counter (PC) is set to 0

- Processor starts executing at zero

(we usually put a branch at zero to the beginning of our code)

# **Setting Up a Reset Vector**

1. Determine the starting address (label) of your code.

**Note:** In this workshop, we use the label start at the beginning of our programs, similar to the way the C language uses main.

2. Branch to this starting label

b start ; RESET vector

3. Locate this code at memory location ZERO.

The optimum method of placing the reset value at location zero is to use the .sect directive, as follows:

We could have placed the code into the .text section, but it makes it much more difficult to force this code specifically to location 0.

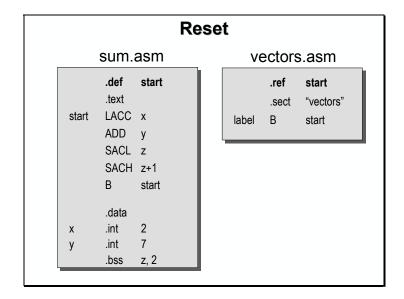

# **Referencing Labels**

If a label is to be shared between two (or more) files, it must be defined — declared — as global. This is done with the .def and .ref commands.

.def is defined in the current module and used in another module.

**.ref** is referenced in the current module, but defined in another module.

**.global** may be either of the above.

# **Linker Command File**

The linker command file might be modified to:

```

Linker CMD File with Vectors

MEMORY

PAGE 0:

/* Program Memory */

/* EPROM: org = 0000h,

VECS: org = 0000h,

len = 2000h

len =

len =

EPROM: org =

len = \overline{8000h}

SRAM: org = \overline{8000h}',

PAGE 1:

/* Data Memory

org = 0060h,

len = 0020h

B2:

I_RAM: org = 0200h,

len = 0200h

\overline{\text{DSRAM}}: org = 8000h, len = 8000h

SECTIONS

.text: > EPROM

PAGE 0

.bss: > DSRAM

PAGE 1

.data: > B2

PAGE 1

_: >

PAGE

```

**Note:** It is convenient to create a separate segment of memory to place the vector table. This prevents another section from accidentally being linked ahead of the vectors section.

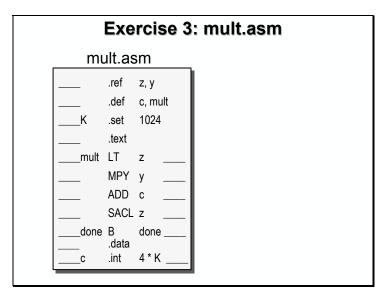

### **Exercise 3**

Let's put ourselves into the linkers position.

### **Exercise 3**

### **Procedure**

- 1. Resolve .set expression in mult.asm

- Using EX3.CMD, fill-in the post-link addresses (left-hand side blanks) of the three ASM files

- Put an 'X' in any blank that has no address

- Branch is a 2-word instruction

- Other instructions are single-word

- Resolve symbolic references (i.e. replace righthand side symbols with the corresponding left-hand side address)

- 4. Link Order: mult.obj sum.obj vectors.obj

### **Exercise 3: EX3.CMD**

```

MEMORY

PAGE 0:

/* Program Memory */

\label{eq:VECS:org = 0000h, len = 0040h} \mbox{VECS: org = 0000h, len = 0040h}

EPROM: org = 0040h, len = 1FC0h

SRAM: org = 8000h, len = 8000h

PAGE 1:

/* Data Memory */

B2: org = 0060h, len = 0020h

I_RAM: org = 0200h, len = 0200h

DSRAM: org = 8000h, len = 8000h

SECTIONS

.text:

> EPROM

PAGE 0

> DSRAM

PAGE 1

.bss:

.data: > B2

PAGE 1

vectors: > VECS

PAGE 0

}

```

# Summary

|                     | Assembler<br>Directives | Definition                                                    |  |  |

|---------------------|-------------------------|---------------------------------------------------------------|--|--|

|                     | .text                   | program code section (initialized)                            |  |  |

| Section             | .data                   | initialized data (constants) section                          |  |  |

| Directives          | .sect                   | user-named initialized section                                |  |  |

|                     | .bss                    | variable data section (uninitialized)                         |  |  |

|                     | usect                   | user-named uninitialized section                              |  |  |

| Define<br>Constants | .int<br>.word           | creates integer constant                                      |  |  |

|                     | .float                  | creates floating-point constant                               |  |  |

| Global              | .def                    | defines labels globally                                       |  |  |

| Labels              | .ref                    | references a global label                                     |  |  |

|                     | .global                 | declares label global (does the job of both .ref and .def)    |  |  |

|                     | .set<br>.equ            | assigns a value (similar to #define in C)                     |  |  |

| Misc.               | .title                  | prints title at top of every page in listing                  |  |  |

|                     | .end                    | the assembler will stop when it finds this or the end-of-file |  |  |

### Lab 2c

### Objective

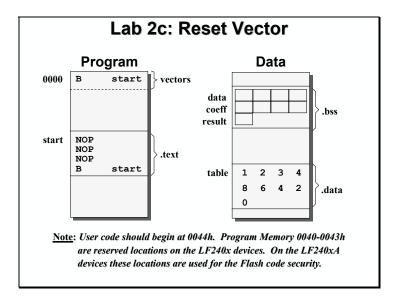

Finally, Lab 2c asks us to add a reset vector to the system we've been working with. The reset vector resides in external memory (at address 0).

Your challenge is to use the assembly tools to specify the value for the reset vector using "relocatable" assembly coding techniques; i.e., labels. Create a new file to contain your reset vector.

### > Procedure

### Create VECTORS.ASM

- 1. Create a new file by clicking on the left most button on the horizontal toolbar "New".

- 2. Add an initialized code section named "vectors" that contains: B start Make sure that the label (*start*) is visible to the linker (.ref). Save your file by clicking on the Save button on the horizontal toolbar. When prompted, save your file and name it "vectors" as type "Assembly Source File" in the C:\DSP24\LABS directory.

### Assemble VECTORS.ASM

- 3. Assemble VECTORS.ASM by clicking on the compile button as you did before to assemble LAB2.ASM. Check for errors before moving on. Save your work after changes.

- 4. Add VECTORS. ASM to the project using the procedure shown earlier. Close the VECTORS. ASM edit window.

### Edit LAB2.ASM

5. To open and edit LAB2. ASM, double click on the file in the project window. Make sure that the label (*start*) is visible to the linker (.def). Save your file by clicking on the Save button on the horizontal toolbar. Close the LAB2. ASM edit window.

### Edit LAB2.CMD

6. To open and edit LAB2.CMD, double click on the filename in the project window. Modify the Memory{}, and Sections{} area, as needed. Note: User code should begin at 0044h. Program Memory 0040-0043h are reserved locations on the LF240x devices. On the LF240xA devices these locations are used for the Flash code security. Save your work. Close the LAB2.CMD edit window.

### Rebuild All

7. Click the "Rebuild All" button and watch the tools run in the build window. Debug as necessary. Right-click on the build window and Hide the build window.

Note: Code Composer can automatically load the output file after a successful build. On the menu bar click: Option → Program Load... and select: "Load program after build", then click OK.

- 8. Open and inspect LAB2.MAP. This file will show you the results of the link process. Note the addresses for the sections. Are the results as expected? Close the .MAP file when done.

- 9. Reload the output file onto the target. Click: File → Reload Program...

Then reset the DSP by clicking on: Debug  $\rightarrow$  Reset DSP

10. If code generation is successful, the Dis-Assembly window will display the source file and a yellow highlight on "B start" should appear. This indicates that you are now ready to run. To debug using both source and assembly, right click on the VECTORS.ASM window and select Mixed Mode. (This should explain why we checked "Enable Source Level Debugging" on the Assembler tab Build Options during our previous lab).

### **Running LAB2**

**Note:** Should you experience a problem with Code Composer, quit, then restart, and reload your project and program.

11. Hit the <F8> key or click the single step button on the vertical toolbar repeatedly and single-step through the program. When you are done close the Dis-Assembly window.

### **Features of Workspace**

12. As you can probably tell, the windows in Code Composer can be moved around and resized. Typically, the default window arrangement is not a desirable one. To customize your display,

move the windows around where you want them. You also may want to right click on each window and select: Float in Main Window. This will allow each window to be visible when it is active.

- 12. Right click on the project window and select: Hide

- 13. To see the CPU registers. On the menu bar click:

```

View → CPU Registers → CPU Registers

```

- 14. Right click in the CPU Registers window and deselect "Allow Docking". You can now move and resize the window as you like. Close the CPU Register window. Locate the "Register Window" button on the vertical toolbar, then click it to see if it appears.

- 15. You can edit the contents of any CPU register by double-clicking on it. Try this with AR7 now. Try typing in both hex and decimal numbers. Note that Code Composer will convert decimal to hex for you.

- 16. To see the disassembly window, find and click the "View Disassembly" button (at the bottom of the vertical toolbar) or click: View → Dis-Assembly on the menu bar.

- 17. As shown earlier, to open a Memory window, on the menu bar click: View → Memory or click the View Memory button on the vertical toolbar.

- 18. If you're familiar with the Command Window used by previous TI debuggers, you can add one by clicking: Tools → Command Window on the menu bar. Resize and dock or undock to your liking.

- 19. At the command line, type: Step 20 →

and watch the Code Composer actions. You should see the screen update to reflect the results of each individual "step".

Notice that reset takes you back to the reset vector located at 0000h. Restart, on the other hand, will return you to the entry label.

21. You can save your workspace by clicking:

```

File → Workspace → Save Workspace

```

and selecting a name. Make sure you save it in C:\DSP24\LABS. **DO NOT save your new workspace as the "default".** When you restart Code Composer, you can reload "your" workspace by clicking:

```

File \rightarrow Workspace \rightarrow Load Workspace and select your filename.

```

You may want to save a "generic" workspace rather than one that opens up a project. Make sure that you close the project before you save this workspace.

### **End of Exercise**

# **Review**

### Review

- 1. List the three assembler directives that are used for initialized sections

- 2. List the two assembler directives that are used for uninitialized sections

- 3. List the two parts of the linker command file

# **Solutions**

```

Lab 2a: Solution - lab2.asm

.bss

data,4

.bss

coeff,4

.bss

result,1

.data

1,2,3,4

table

.int

8,6,4,2

.int

.int

.text

start

nop

nop

nop

nop

b

start

```

### **Exercise 2 - Solution**

### Lab 2b: Solution - lab2.cmd

```

MEMORY

{

PAGE 0:

EPROM: org = 0000h, len = 8000h

PAGE 1:

B2: org = 0060h, len = 0020h

I_RAM: org = 0200h, len = 0200h

SARAM: org = 0800h, len = 0800h

}

SECTIONS

{

.text: > EPROM PAGE 0

.data: > I_RAM PAGE 1

.bss: > B2 PAGE 1

}

```

### **Linker CMD File with Vectors**

### Exercise 3: Solution - mult.asm

### mult.asm

```

Χ

.ref z, y

Χ

.def c, mult

^{\mathsf{X}}\mathsf{_K}

.set 1024

Χ

.text

40 mult LT z

8000

MPY y

41_

42

ADD c

60

43

8000

SACL z

44_done B

done 44

Χ

.data

60_c

.int 4 * K 4096

```

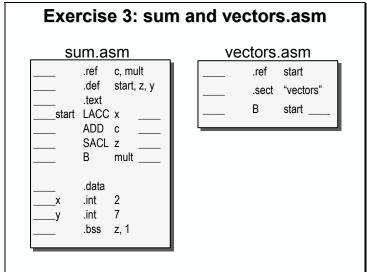

# Exercise 3: Solution - sum and vectors.asm

#### sum.asm .ref c, mult Χ .def start, z, y X .text 61 46 start LACC x 47 ADD c 60 48 SACL z 8000 В 49 mult <u>40</u> .data

.int 2

int 7

.bss z, 1

61 <sub>X</sub>

62 y

8000

# x .ref start x .sect "vectors" 0 B start 46

# Lab 2c: Solution - lab2.asm

```

.def

start

.bss

data,4

.bss

coeff,4

.bss

result,1

.data

.int

1,2,3,4

table

.int

8,6,4,2

.int

.text

start

nop

nop

nop

nop

b

start

```

### Lab 2c: Solution - vectors.asm

```

.ref start

.sect "vectors"

b start

```

### Lab 2c: Solution - lab2.cmd

```

MEMORY

{

PAGE 0:

VECS: org = 0000h, len = 0040h

EPROM: org = 0044h, len = 7FBCh

PAGE 1:

B2: org = 0060h, len = 0020h

I_RAM: org = 0200h, len = 0200h

SARAM: org = 0800h, len = 0800h

}

SECTIONS

{

vectors: > VECS     PAGE 0

.text: > EPROM     PAGE 0

.data: > I_RAM     PAGE 1

.bss: > E2     PAGE 1

}

```

This page is left intentionally blank.

# **Addressing Modes**

# Introduction

This module will describe the various addressing modes available on the TMS320C240x. The ability to express constants, especially useful in the initialization process, is called immediate addressing. Direct addressing allows for general purpose memory access. Indirect addressing makes use of auxiliary registers to provide hardware support for various pointer functions, such as accessing data organized in arrays. Techniques for managing data pages, relevant to direct addressing, will be discussed.

# **Learning Objectives**

### **Learning Objectives**

- Use large and small constants

- Setup and use direct and indirect addressing modes

- ♦ Identify the best mode for a process

- Load, store, add and subtract values between memory and the accumulator

# **Module Topics**

| Addressing Modes        | 3-1  |

|-------------------------|------|

| Module Topics           | 3-2  |

| Memory Organization     |      |

| Data Addressing Modes   | 3    |

| Immediate Addressing    |      |

| Direct Addressing       | 3-0  |

| Indirect Addressing     | 3-10 |

| Addressing Modes Review | 3-13 |

| Addressing Exercise     | 3-10 |

| Lab 3: Addressing       | 3-17 |

| Review                  |      |

| Solutions               | 3_20 |

# **Memory Organization**

As was previously noted, the C240x memory map is made up of three 64K ranges for program, data, and I/O memory. A 64K-memory range requires a 16-bit address to uniquely identify each location within the range. The contents of all locations are treated as 16-bit words.

Program memory is generally addressed via 16-bit immediate values such as was seen in the branch instruction (e.g., B 1234h). I/O memory addressing will be presented in Module 7. After a review of the memory structures present on the C240x, this module will concentrate on how to express data values, or operands, as numerical constants or as components of the data memory map.

### **On-Chip Memory Modules**

The C240x devices offer a variety of memory mixes, which include program ROM/Flash, Data RAM, and Dual-purpose RAM.

C240x-based devices may contain ROM which is enabled when the  $MP/\overline{MC}$  pin is taken low. The ROM, if selected, is present at the lowest addresses of program space.

Data RAM is composed of two blocks of memory located at 0060- 007Fh and 0200-03FFh in the Data memory map. All C240x-based devices have these memories in common. An additional feature of these RAMs is that they are "dual access" memories, which are useful in implementing delay lines (and will be demonstrated in Module 7). These dual access RAMs are the most costly of the on-chip memories.

One dual access block, called *RAM Block 0*, is located at 0200-02FFh in Data memory at reset, and may be relocated to FF00-FFFFh in Program memory via the CNF (configure) bit under program control.

### LF2407 Memory Map

# **Data Addressing Modes**

The C240x instruction set allows several modes for addressing data memory and expressing constants. In this module, we will concentrate on the following:

### **Data Addressing Modes**

| Mode                    | Purpose                                                               |

|-------------------------|-----------------------------------------------------------------------|

| Immediate<br>(Constant) | Initialize registers, operate with constants                          |

| Direct<br>(Paged)       | Access data on a given page in any order                              |

| Indirect<br>(Pointer)   | Access data from arrays anywhere in data memory in an orderly fashion |

### Instructions used in Module

Addressing modes in this module will make use of the following instructions:

```

LACC x ;Load ACCumulator from <dma> "x"

SACL y ;Store ACcumulator Low half to <dma> "y"

ADD a ;ADD to accumulator value from <dma> "a"

SUB b ;SUBtract from accumulator value from <dma> "b"

```

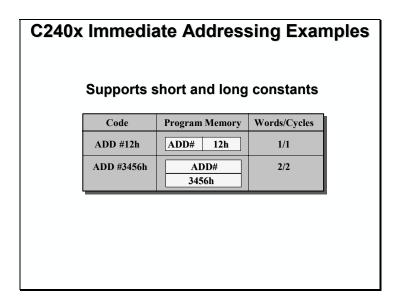

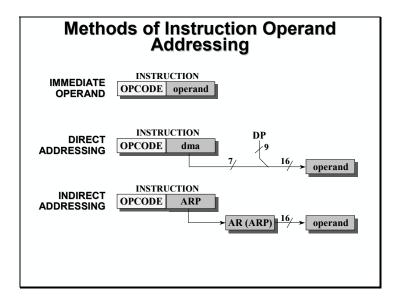

# **Immediate Addressing**

In immediate addressing, the operand is part of the instruction word itself and is identified by the pound (#) symbol.

Small values may be expressed within a single program word, while large values require a second program word (and therefore, a second cycle to execute). Small, or "short," immediate values are generally limited to 8 bits, but depending on the instruction in which they are used, may range from as small as a 1-bit constant to as large as 13 bits. The *TMS320C240x User's Guide* presents a table of immediate instruction word widths.

Values which exceed the limit of a short constant become two-word, two-cycle operations on the C240x, but look identical from the programmers perspective, as seen in the example below:

```

ADD #12h ; 0012h is added to the Acc, 1 cycle ADD #3456h ; 3456h is added to the Acc, 2 cycles

```

Long immediate instructions also allow a second operand to be specified: a shift value which can be used to position the 16-bit constant within a 32-bit register. Shift operations will be described and used in later modules.

For a complete list of the operations which support immediate addressing, refer to the *TMS320C240x User's Guide*.

An example of the immediate addressing process is shown in the previous figure. Note that the data environment is not used in this type of instruction. A true Harvard machine derives operands from data space only — the ability to pass operands from program space is one of the reasons why the 320 are said to have a "modified" Harvard architecture.

# **Direct Addressing**

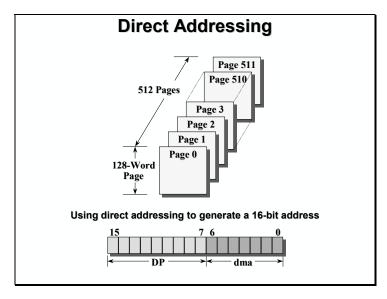

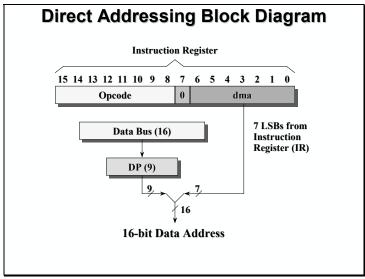

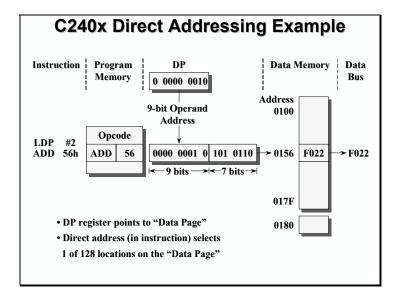

Since the C240x has an instruction word size of 16 bits and a data address width of 16 bits, it would seem that attempting to directly use a data memory value would require two cycles; i.e., one to specify an operation, and the second to express the data memory address to be accessed (somewhat like the method used in long immediate addressing). This, however, would yield slow (two-cycle) access for direct addressing, which is undesirable in most systems. Instead, the C240x allows the user to specify an area of memory, and direct-addressed instructions operate within this reduced range of memory. This "paged" memory approach is common to many processors, as a compromise between memory range and speed.

In the C240x, a 9-bit Data Page (DP) register is used to specify the active area of memory. Thus, at any one time, 128 locations, on any one of 512 selectable pages, are active for direct addressing. These 128 locations may be addressed with only 7 bits, making single-cycle operation possible. Since the DP is a programmable register, the entire memory map is accessible 128 locations at a time.

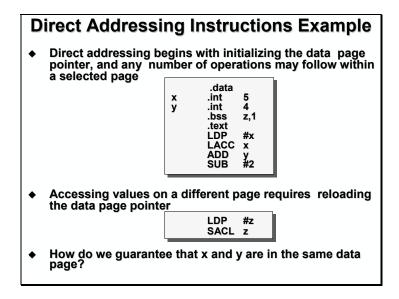

Direct addressing, therefore, begins with initializing the DP, most commonly with the LDP (Load Data Page) instruction. Any number of operations may follow within the selected page.

### **Direct Addressing Considerations**

As such, the programmer is advised to group as much data for a given process on a single page, thus minimizing the time spent modifying DP, and maximizing the time spent in actual processing. This presents two more issues. First, as described in Module 2, the COFF tools used at TI are most beneficial when symbolic, as opposed to fixed, addresses are used. How then is the DP to be set, and how does the programmer know when a page boundary is to be crossed?

It turns out that the method for performing direct addressing on a symbolic address is quite simple, as noted in the following example.

```

.bss x,1 ; allocate 1 (16 bit) location for the variable "x" LDP \#x ; load the DP with the page containing "x" ADD x ; add to the acc. the contents of location "x"

```

In the above examples, it is important to note the use of the pound (#) in the LDP operand. Without the pound sign, data page would be loaded from the lower 9 bits of location x on the current page and, since the page has not yet been initialized, an effectively random value will be loaded to DP.

As to the second question raised above, how does the programmer know when a page boundary is going to be crossed? Consider the following example.

From this segment of code, it is not known that x and y is on the same data page. The following approaches exist for building reliable direct addressed code.

### **Keeping Variables on Same Data Page**

- 1. Place an LDP before every direct operation

- 2. Force the sections containing the variables / data onto a single page using the link command file

- 3. Use FILE LIST linker option to split sections into specific files

- 4. Use the contiguous page switch

- 5. Use BLOCK or ALIGN linker options

Note: Refer to the Student Guide for more details on each option

- 1. Place an LDP before every direct operation. Effective and fail-safe, but wastes processor time and code space.

- 2. Load .bss or .usect allocations (via the linker command file) into a memory structure on a single data page. Excellent for smaller sections, inadequate for systems which exceed 128 requests.

- 3. Use the FILE LIST option in the section declaration within the linker command file. A standard linker command file allocates .bss this way:

```

.bss {} : > RAM PAGE 1

```

The braces "{}" may contain a list of files to operate upon. Thus, if a system contained files f1, f2, and f3, and the first two fit on a single page, but the last one needed to be directed to a new page, the command file could be modified to read:

```

.bss {f1,f2} : > RAM1 PAGE 1

.bss {f3} : > RAM2 PAGE 1

```

In this way, .asm files could use simple .bss allocations, and the linker command file would manage their pagewise continuity.

4. Use the .bss Contiguous Page Switch, e.g., .bss x, 5, 1. This would force all five locations in the array x to reside on a single page. The linker will skip to the next data page if insufficient room is present on the current page for the entire allocation. Skipped locations may be backfilled by later .bss allocations which can fit in without being split up.

When using this method, note that the contiguous switch pertains only to the single allocation, thus:

```

.bss x, 5, 1

.bss y, 4, 1

```

may reside on two separate pages. To assure x and y on the same page, consider this approach:

```

.bss x, 9, 1 y .set x+5

```

By setting x as one large array, and declaring y as a point within the array, the linker will treat both as a single entity, on a single page. In most cases, this is the optimal method for handling direct addressing.

5. Use linker keyword BLOCK or ALIGN in linker command file.

Methods 3-5 require the programmer to set the data page when entering a new program. Thereafter, all .bss for the individual program will then be on a single page.

None of these concepts present the single best solution. The programmer should choose the method that yields the desired performance for the given system with the least amount of effort. Simple systems may be served by the earlier suggestions, while more demanding systems will invoke concepts from latter options, or a combination of several.

## **Direct Addressing Review**

An example of direct addressing on the C240x is presented in the following figure.

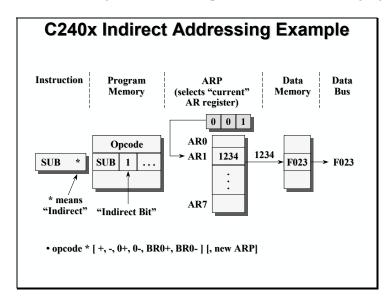

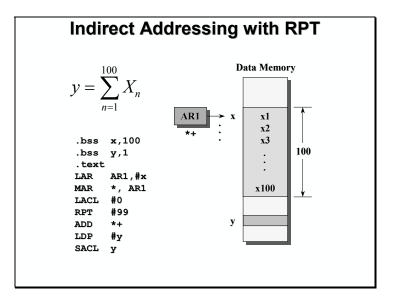

# **Indirect Addressing**

Indirect addressing is an efficient and powerful way to access data stored in lists, arrays, or other orderly groupings in memory. Unlike direct addressing, the address is not expressed in the instruction word, but instead is located in an Auxiliary Register (AR). The use of an AR provides several benefits. First, ARs are 16-bit registers, and thus may point to any location in the entire data memory map without the aid of the data page register. Additionally, the AR may be automatically incremented or decremented after an operand is read, so that a new datum is being pointed to for use in a later operation. The use of this feature makes the performance of iterative processes fast and easy.

Eight ARs are available on the C240x devices. For indirect addressing to be used, an AR must first be initialized and selected. ARs are initialized via the LAR (Load Aux Register) instruction. Initial selection of the active AR is via the MAR (Modify Aux Register) instruction. For greater performance, subsequent AR selections can be specified within any instruction using indirect addressing.

## **Indirect Addressing Operands**

The use of the asterisk (\*) is the indirect operator, indicating the use of the current AR to point to the data value to be used. When the plus sign (+) is added, it represents the auto-increment function, where the current AR is to be incremented by one after the operand is read. Similarly, the use of a minus sign (-) would specify an auto-decrement. Since the C240x devices provide dedicated hardware for implementing auto-increment/-decrement operations, no extra cycle time is required for this operation.

### **Indirect Addressing Sequence**

ADD \*+,1,AR0

- 1. \* ARP selects AR to address operand

- 2. 1 Shift operand left 1-bit optional, 0 default

- 3. ADD Operate on shifted operand

- 4. + Modify AR value optional

- 5. AR0 New ARP value optional

Indirect addressing allows 16-bit registers to be used as pointers to data memory. It is frequently used to operate on arrays of data, and includes built-in hardware to implement several forms of auto-increment or auto-decrement functions (and new AR selection options) within the operation as indicated in the following figure.

| C240x I | ndirect Addressing Options |

|---------|----------------------------|

| Option  | Function                   |

| *       | Does not change current AR |

| *+      | Increments current AR      |

| Option | Function                                                     |

|--------|--------------------------------------------------------------|

| *      | Does not change current AR                                   |

| *+     | Increments current AR                                        |

| *-     | Decrements current AR                                        |

| *0+    | Adds AR0 to current AR                                       |

| *0-    | Subtracts AR0 from current AR                                |

| *BR0+  | Adds AR0 to current AR with reverse carry propagation        |

| *BR0-  | Subtracts AR0 from current AR with reverse carry propagation |

|        |                                                              |

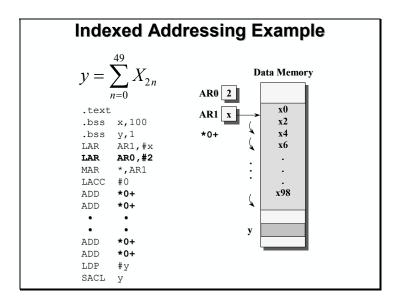

## Indirect Addressing Example

Consider the following example demonstrating the use of indirect addressing to help illustrate the process. Allocate two arrays in memory, x and y, each containing four values. One AR can be initialized to point to x and another to y. To add all these values together, it would first be necessary to make one AR active for summing the x values, and then have the second AR be active for summing the y values. The following code implements this process.

```

Indirect Addressing Example

;allocate 4 locations for the "x" array

.bss

.bss y,4

;allocate 4 locations for the "y" array

.text

LAR

AR2, #x ;load AR2 with the first "x" address

LAR

AR5,#y

;load AR5 with the first "y" address

*,AR2 :LARP AR2

MAR

LACC *+

;load ACC using AR2, then increment AR2

ADD

*+

;add to ACC using AR2, then increment AR2

*+

; add to ACC using AR2, then increment AR2 \,

ADD

ADD

*,0,AR5 ;add to ACC using AR2, then make AR5 active

ADD

*+

; add to ACC value pointed to by AR5 (y), inc AR5

ADD *+

add and increment

ADD *+

;add and increment

ADD *+

; add and increment

```

Note that when AR5 is made active, a 0 had been specified as the second operand. This is because instructions which operate on the Accumulator offer a shift option in the second operand field. Since no shift was needed in this instance, a 0 (the default value) was inserted to get to the third operand field — the NARP (New ARP) field. From this discussion, it is apparent that a single instruction is capable of finding, shifting, and using an operand; then operating on the current AR; and then selecting a new ARP, as shown in the above figure.

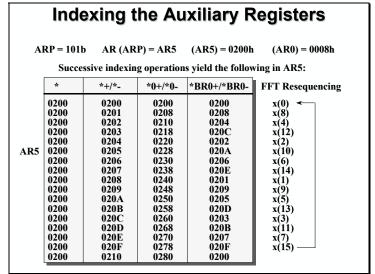

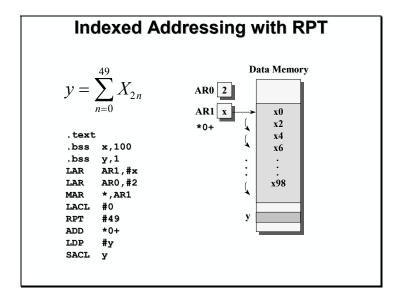

### Indexing with Indirect Addressing

Sometimes it is desirable to be able to increment/decrement by values other than one. In these instances, an index register is required to specify the step size to be used. On the C240x, AR0 can be used as either a pointer or an index value on any other pointer. Use of the index during auto-increment/auto-decrement is specified by adding a 0 (shorthand for "AR0") before the modifier, as in \*0+ or \*0-.

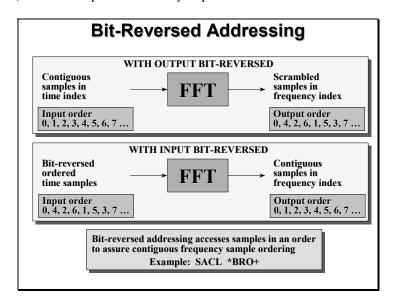

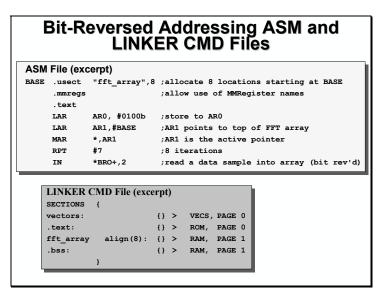

### Bit-Reversed Addressing

Bit-reversed addressing is a very efficient means of addressing in Fast Fourier Transforms (FFTs). The FFT is a process for converting information in the time domain to information in the frequency domain, and relies upon a "butterfly" operation as the core mathematical procedure.

Notice in the figure above that the process causes the outputs to be out of sequence. Reordering the array requires significant amounts of processor time, or the use of external logic. The C240x

has a form of addressing which eliminates the need for address correction, by putting the out-of-order results in their proper locations *during* processing of the FFT. No extra time or hardware is required, allowing a much more efficient FFT implementation. To best understand this addressing mode, note the order of the outputs as binary numbers. At first, they seem random, but notice the pattern that exists if the number is read as if the order of most significant to least significant bit were reversed: it is (read backwards) a simple increment of one, with the carry operations propagating to the right. This addressing operation, sometimes called *reverse carry propagation* is much like a "mirror image" of the normal addressing order. Bit-reversed addressing, as used by the C240x, acts like placing the reversed addresses generated by the FFT in a mirror — they are read normally. To implement this "double mirror image" requires that the array counting value be placed in AR0, and that any other AR be used as the addressing register, with the "\*BR0+" or "BR0-" mode selected. The array counting value is simply a 1 in the correct bit position for the increment process. Use the value N/2 for an N-size array.

The actual code to implement the FFT may be found on the TI bulletin board, and will not be discussed here.

One further detail needs to be established for bit-reversed addressing to function properly; i.e., the FFT array must be established at a "0" starting address, or, as it turns out, an address with a sufficient number of LSBs equal to zero. In this example (an 8-point FFT), three LS bits are used in the bit-reversed addressing and the 13 remaining MSBs remain unchanged. Thus, any data memory address with three LS bits at zero would be an acceptable starting point. The need for a specific type of RAM for the FFT calls for the use of a .usect in the .asm file. Specifying the number of LS zero bits is taken care of in the linker command file with the align directive, as indicated in the following figure.

# Indirect Addressing Review

An example of indirect addressing on the C240x is presented in the following figure.

# **Addressing Modes Review**

Three addressing modes have been presented. Each is best suited for different purposes.

**Immediate addressing** is best for providing constants at initialization time.

**Indirect addressing** is a powerful addressing mode, best suited to iterative and tabular operations, where the increment/decrement function becomes quite useful.

**Direct addressing** may be considered the best general-purpose addressing mode. Given an understanding of the paged-memory concept, direct addressing is a very easy-to-use mode, is simpler to debug, and is as fast as indirect addressing in operation (both are single-cycle operations). With direct addressing, no time penalty occurs for operands selected in any order on a given page; however, with indirect addressing, the locations used must be in order.

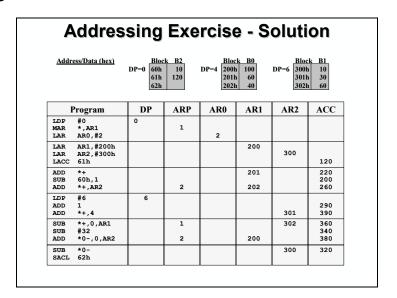

# **Addressing Exercise**

Before beginning the labs, the details of addressing will be exercised with the segment of code below. You are to read the code on the left, use the memory as defined above, and perform the program as you expect the C240x would. As is often the case in program development, look out for errors.

| Addressing Exercise |                               |                        |           |                           |      |                           |                   |

|---------------------|-------------------------------|------------------------|-----------|---------------------------|------|---------------------------|-------------------|

| Addr                | ess/Data (hex)                | DP=0 60h<br>61h<br>62h | 10<br>120 | DP=4 2001<br>2011<br>2021 | 1 60 | DP=6 3001<br>3011<br>3021 | h 30              |

| I                   | Program                       | DP                     | ARP       | AR0                       | AR1  | AR2                       | ACC               |

| LDP<br>MAR<br>LAR   | #0<br>*,AR1<br>AR0,#2         |                        |           |                           |      |                           |                   |

| LAR<br>LAR<br>LACC  | AR1,#200h<br>AR2,#300h<br>61h |                        |           |                           |      |                           | 120               |

| ADD<br>SUB<br>ADD   | *+<br>60h,1<br>*+,AR2         |                        |           |                           |      |                           | 220<br>200<br>260 |

| LDP<br>ADD<br>ADD   | #6<br>1<br>*+,4               |                        |           |                           |      |                           | 290<br>390        |

| SUB<br>SUB<br>ADD   | *+,0,AR1<br>#32<br>*0-,0,AR2  |                        |           |                           |      |                           | 360<br>340<br>380 |

| SUB                 | *0-<br>62h                    |                        |           |                           |      |                           | 320               |

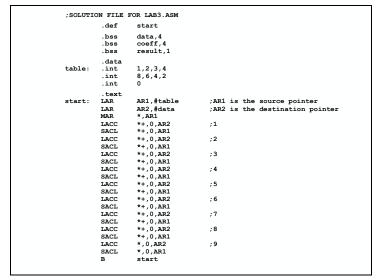

## Lab 3: Addressing

#### Objective

The objective of this lab is to practice and verify the mechanics of addressing. In this process we will expand upon the ASM file from the previous lab to include new functions. Additionally, we learn how to run and observe the operation of code using Code Composer.